Устройство для контроля многоканальных блоков памяти

Иллюстрации

Показать всеРеферат

Союз Советских

Социапистических

Республик

О П И C А Н И Е (,gag()58

ИЗО6РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 04. 02. 80 (21) 2880644/18-24 (51)М. Кл.. с присоединением заявки М

G 11 С 29/00

Говударстненньн1 квинтет

СССР (23) Прноритет—

ll0 делам наебретеннй н атнрытнй

Опубликовано 30. 11. 81. Бюллетень М 44 (53) УДК 681,327, (088.8 ) Дата опубликования описания 01 .12.8 1 (12) Авторы изобретения

В. К. Цапулин, В. В. Алешко (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ 1НОГОКАНАЛЬНЫХ БЛОКОВ ПАХ1ЯТИ

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля многоканальных блоков памяти, содержащее счетчик числа обращений, счетчик математических ожиданий, генератор случайных чисел и сумматор $1) .

Недостатком этого устройства является его сложность.

Наиболее близким к предлагаемому по технической сущности является устройство для контроля многоканальных блоков памяти, содержащее блок анализа переменной составляющей, блок восстановления, исполнительный блок, 15 и блок сравнения, на первые входы которого поступает информация из нако- . пителя, а на вторые входы — информация, прошедшая через блок восстановления (21.

Недостатками этого устройства являются низкая достоверность контроля вследствие невозможности проверки накопителя сигналами с точно определенными статистическими параметрами и невозможности анализа ошибок любой кратности, а также схемная сложность блока восстановления и блока анализа переменной составляющей.

Цель изобретения — упрощение устройства и повышение достоверности контроля.

Поставленная цель достигается тем, что в устройство для контроля многоканальных блоков памяти, содержащее схему сравнения, одни из входов являются входами устройства, а выходы подключены ко входам исполнительного блока, введены группа регистров и генератор псевдослучайных сигналов, входы которого подключены к выходам регистров группы, входы которых сое- динены с выходами исполнительного блока, выходы генератора псевдослучайных сигналов подключены к другим входам схемы сравнения и являются выходами устройства

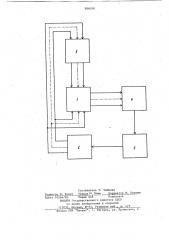

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит схему 1 сравнения, генератор 2 псевдослучайных сигналов, группу регистров 3 и исполнительный блок 4.

На чертеже изображен также контролируемый блок 5 памяти.

Одйй из выходов схемы 1 сравнения являются входами устройства, а выходы подключены ко входам исполнитель-. ного блока 4. Входы генератора 2 псевдослучайных сигналов соединены с выходами регистров 3 группы,. входы которых соединены с выходами исполни- 1 ,тельного блока 4. Выходы генератора 2 псевдослучайных сигналов подключены к другим входам схемы 1 сравнения и являются выходами устройства. Генератор 2 псевдослучайных сигналов выполнен на регистрах максимальной последовательности;

Устройство работает следующим образом.

Перед началом режима записи в гене- ратор 2 псевдослучайных сигналов заносится начальная комбинация информации записи и одновременно она запоминается в регистрах 3 группы. Генератор 2 псевдослучайных сигналов повто- зо ряет генерируемую информацию через число циклов, определяемое внутренними обратными связями, а при условии одинаковой начальной комбинации генерирует одну и ту же псевдослучайную

ЗЭ последовательность. В режиме записи исполнительный блок 4 выдает сигналы, по которым информация с выхода генератора 2 псевдослучайных сигналов передается для записи в контролируемый блок 5 памяти.

Перед воспроизведением начальная комбинация иэ регистров 3 группы переписывается в регистры генератора 2 псевдослучайных сигналов. При воспро43 изведении информации из блока 5 памяти поступает на одни из входов схемы

58 4 сравнения., на другие входы которых поступает информация с генератора 2 псевдослучайных сигналов. Так как начальная комбинация информации генератора 2 псевдослучайных сигналов при воспроизведении такая же, как и при записи, информация с его выхода при воспроизведении повторяет ранее записанную информацию, т.е. используется в качестве эталонной. Зталонная информация сравнивается с информацией, принимаемой из контролируемого блока 5 памяти, схемой сравнния l„ результаты сравнения фиксируются в испольнительном блоке 4.

Технико-экономические преимущества предлагаемого устройства заключаются

Ю 1 в его большей схемкой простоте и более высокой достоверности контроля по сравнению с известным. формула изобретения

Устроиство для контроля многоканальных блоков памяти, содержащее схему сравнения, одни из входов которой являются входами устройства, а выходы подключены ко входам исполнительного блока, о т л и ч а ю щ е ес я тем, что, с целью упрощения устройства и повышения достоверности контроля, оно содержит группу регистров и генератор псевдослучайных сигналов, входы которого подключены к выходам регистров группы, выходы которых соединены с выходами исполнительного блока, выходы генератора псевдослучайных сигналов подключены к другим входам схемы сравнения и являются выходами устройства, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР №- 52б952, кл. G ll С 29/00, 1974.

2. Авторское свидетельство СССР

¹ 534795, кл. G 11 С 29/00, 1975 (прототип).

886058

Составитель Т. Зайцева

Редактор !О. Ковач Техред М. Надь Корректор M. Нароши

Заказ 10566/80 Тираж 648 Подписное

ВНИ11ПИ Государственного комитета СССР по делам изобретений и открытий

113035 МосКВа Ж-35 Раушская наб.д д. 4/5

Филиал ППЛ "Патент", r. Ужгород, ул. Проектная, 4