Цифровой фильтр

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ .Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<в886216

Союз Сонетскик

Социалистическик

Республик с (72) Авторы изобретения

М. И. Курячий, .Г. А. Сваткова и В. И . .- Ицкович

У

Томский институт автоматизированных систем управления и радиоэлектроники (71) Заявитель (54) ЦИФРОВОЙ ФИПЬТР

Изобретение относится к радиотех нике н п для.фильтрации входного физического параметра, выраженного цифровым кодом.

Известно устройство Фильтрации, ao"" строенное на основе цифровой.систе" мы фазовой автоподстройки частоты и. содержащее последовательно соединенные дискриминатор, реверсивный счетчик, блок добавления-исключения, счетчик импульсов, элемент И и блок памяти, при этом второй вход элемента И соединен с первым выходом синхронизатора, второй выход которого. со» единен со вторыми входами дискрими" натора н блока добавления-исключения, причем второй выход счетчика ймпуль сов соединен с третьим входом Пискриминатора Г1 ) °

Недостатком цифрового фильтра, построенного по такому принципу, является наличие зоны нечувствитель" ности, обусловленной округлением результата s реверсивном счетчике, 2 а количество разрядов входного и выходного кодов одинаково, что существенно снижает точность входного параметра цифрового фильтра.

Цель изобретения — повыщение точ . ности фильтрации.

Для этого в цифровом фильтре, содержащем дискриминатор, первый вход которого является входом устройства, а выходы подключены ко входам . реверсивного счетчика, последователь. но включенные блок добавления-иск.лючения импульсов, счетчик импульсов,, элемент И и блок памяти целой части, а также синхронизатор, первый выход !

Э, которого соединен с другим входом элемента И, а второй выход - с первым входбм блока добавления-исключения импульсов и со вторым входом дискриминаторат третий вход которого подключен к выходу счетчика импульсов к выходу реверсивного счет чика подключены последовательно нор. мирующнй блок, дополнительный эле-

886216 4

15 ции.

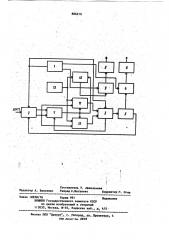

На чертеже представлен цифровой, фильтр, структурная электрическая схема.

Устройство содержит синхрониза- . 20 тор 1, первый выход которого подключен к одноименным входам дискримина" тора 2 и блока 3 добавления-исключения импульсов, а второй выход синхронизатора 1 соединен с одноименным « входом элемента И 4. Второй вход дискриминатора 2 соединен с одноименным выходом счетчика 5 импульсов, первый вход которого соединен с од" ноименным выходом блока 3 добавле" 50 ния-исключения импульсов, а первый. выход счетчика 5 импульсов подключен к последовательно соединенным элемен- ту И 4 и блоку 6 памяти целой части.

Выходы дискриминатора 2 соединены с

"одноименными входами реверсивного счетчика 7.

В устройство также введены: блок .

8 памяти дробной части; элемент И 9, нормирующий блок 10, первый и второй компараторы ll и 12, блок 13 памяти постоянной фильтрации.

Выход реверсивного счетчика 7 подключен через первый и второй компараторы 11 и 12 ко второму и третьему входам блока 3 добавления-исключения импульсов и к последовательно соединенным нормирующему блоку 10, элементу И 9 н блоку 8 памяти. При этом третьи входы первого и второго компараторов ll и 12 соединены со вторым выходом дискриминатора 2, а первые входы вышеупомянутых компараторов и нормирующего блока 10 под" ключены к выходу блока 13 памяти.

Кроме того, установочный вход реверсивного счетчика 7 соединен сО вто рым выходом блока 3 добавления-исключения, а третий выход синхронизатора

0 мент И, другой вход которого .соеди" нен с третьим выходом синхронизатора, и блок памяти дробной части, между одним из выходов дискриминатора и входами блока добавления-исключения импульсов включены соответствующие компараторы, вторые входы которых подключены к выходу ре,версивного счетчика, установочный вход которого соединен со вторым выходом блока добавления-исключения импульсов, а к третьим входам компараторов н ко второму входу нормирующего блока подключен выход блока памяти постоянной фильтраl подключен ко второму входу элемента И 9.

Устройство работает следующим образом.

До. поступления на вход устройства входного сигнала (пТ ) в блоках 6 и

8 памяти записаны нулевые значения кодов выходного сигнала, в блоке 13 памяти записано значение кода посто-. янной фильтрации А. При этом с первого выхода синхронизатора 1 на один . из входов блока 3 добавления-исключения, а также на первый вхо дискриминатора.2 поступают последовательности тактовых импульсов, но, так как на другом входе блока 3 добавленияисключения и на первом входе дискриминатора 2 сигналы отсутствуют, реверсивный счетчик 7 и счетчик 5 находятся в состояниях, соответствующих нулевому. На компараторах 11 н 12 по первым входам выставлены значения порогов И+А и Й-А соответственно.

Й - код нулевого состояния реверсивного счетчика 7, емкость которого равна 2М.

Прн поступлении .на вход фильтра выборки из произвольяого сигнала

X(nT) с выхода дискриминатора 2 на второй и третий входы реверсивного счетчика 7 соответственно постуаают модуль и знак рассогласования, в первом периоде Т работы цифрового фильтра, численно равный модулю н знаку выборки из сигнала, так как ка второй вход дискриминатора 2 поступает нулевое значение кода.

В зависимости от знака рассогласования происходит изменение значения кода реверсивного счетчика 7 в сторону увеличения, либо уменьшения, и при достижении соответствующего порога одного из компараторов

11 и 12 происходит либо исключение (при йоложительиом знаке рассогласования), либо добавление (при отрицательном знаке рассогласования) одного импульса к эталонной последовательности, поступающей на первый вход блока Э добавления-исключения. 1

При превышении пррога какого-либо из компараторов происходит сброс реверсивного счетчика 7 в состояние М, соответствующее нулевому.

Таким образом, в каждом периоде работы устройства нз эталонной последовательности импульсов, имеющейся на первом входе блока 3 добавле886216 низ-исключения, происходит исключение (либо добавление в нее) некоторого количества импульсов, равного целой части частного от деления модуля рассогласования между сигнала- 5.. ми на первом и втором входах дискриминатора 2 на постоянную фильтрации А, а дробная часть этого частного остается в реверсивном счетчике 7, т. е. состояние его в следу щем периоде работы устройства будет отличаться от N на величину этой дробной части.

Скорректированная в блоке 3 добавления"исключения последовательность импульсов поступает на вход счетчика 5 и изменяет фазу выходного импульса счетчика 5 таким образом, что уменьшается величина рассогласования между сигналами на 2D первом и втором выходах дискримина- тора 2. Фазой выходного импульса счетчика 5 является сдвиг заднего фронта того импульса относительно начала периода работы-цифрового фильт. 55 ра.

Остаток от деления модуля рассогласования на постоянную Фильтрации

А учитывается в следующем периоде работы фильтра, а также с . выхода 5р реверсивного счетчика 7 поступает на второй вход нормирующего блока l0, на первый вход которого поступает постоянная фильтрации A. Нормированное к постоянной фильтрации значение остатка поступает с выхода нормирующего блока IO через элемент И 9 записывается в блок 8 памяти при поступлении импульса переписи на второй вход элемента И 9 с третьего выхода синхронизатора,l, Таким образом, формируется дробная часть выходного кода Qp(nT). Целая часть выходного кода Y (nT) заключена в фазе выходного импульса счетчика 5 и с его

45 первого выхода через элемент И 4 записывается в блок 6 памяти при поступлении иа второй вход элемента

И 4 импульса переписи с одноименного выхода синхронизатора l a co второго выхода счетчика 5 информаSD ция о целой части поступает на второй вход дискриминатора 2. б

В последующих периодах работы цифрового фильтра в каждом из периодов дискриминатор 2 вычисляет разность

М f (n T) - Y„(n "1 ) Т3, которая поступает на первый и второй входы реверсивного счетчика 7 (входы модуля и знаках, и вышеупомянутые операции повторяются.

Формула изобретения

Цифровой фильтр, содержащий дискриминатор, первый вход которого является входом устройства, а выходы подключены ко входам реверсивного счетчика, последовательно включенные блок добавления-исключения импульсов, счетчик импульсов, элемент И .и блок памяти целой части,. а также синхронизатор, нервый выход которого соединен с другим входом элемента И, а второй выход — e первым входом блока добавления-исключения импуль- сов и со вторым входом дискриминатора, третий вход которого подключен к .выходу счетчика импульсов, о т— л и ч а ю шийся тем, что, с целью повьапення точности фильтрации, к выходу реверсивного счетчика подключены последовательно нормирующий блок, дополнительный элемент И, другой вход которого соединен с третьим выходом синхронизатора, и блок памяти дробной части, между одним иэ выходов дискриминатора и входами блока добавления-исключения импульсов включены соответствующие компараторы, вторые входы которых подключены к выходу реверсивного счетчика, установочный вход которого соединен со вторым выходом блока добавления-исключения импульсов, а к третьим входам компараторов и ко второму входу нормирующего блока подключен выход блока памяти постоянной фильтрации.

Источники информации, принятые во внимание при экспертизе

Системы фаэовой автоподстройки частоты с элементами дискретизации. Под. ред. В. В. Шахгильдяна, М., "Связь", 1979, с. l02-104, рис. 4.5 (прототил).

886216

Составитель Т. Афанасьева

Техред С.Иигунова. . Корректор Г, Огар

Редактор А. Власенко

° ВЮ ЮЮЮВ Ф

Заказ 10S58/76 Тирам 991 . ., Яодписиое

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д, 4/S еюееаююееевеюеааев4вееавюевеанеаеавевенвавееаве аеееареавееввве

Филиал ЛЛП "Патент, r..Умгород ул,.йроектная, 4 ппп,патент зак. 8S08