Блок контроля цифрового кода

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ИПЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву В 818018 (22) Заявлено 061179 (23) 2837389/18-21 (5 ) N

Н 03 К 19/23 с присоединением заявки М— (23) Приоритет

Государствеиимй конитет

СССР ио делан изобретеиий и открытий

Опубликовано 30.1181, Бюллетень Ж 44

Дата опубликования описания 301181 (53) УДК 681.32 (088.8) (72) А вторы изобретения

В.В.Блатов и А.А.Чудов (71) Заявитель (54 ) БЛОК КОНТРОЛЯ ЦИФРОВОГО КОДА

Изобретение относится к импульсной технике и может быть использовано для обработки цифровой информации

При обработке цифровой информации в ряде случаев, например при построении дешифраторов комбинационноГо типа для обработки результатов изме-. рений, необходимо одновременно или последовательно производить контроль четности принимаемых сигналов, заданных двоичными кодами, знать о количестве принимаемых сигналов одновре» менно (определять наличие одного из и или двух и более из п входных сигналов).

Известен блок контроля цифрового кода, содержащий элемент ИЛИ и группы полусумматоров, выходы переносов которых соединены с входами элемента ИЛИ, входы полусумматоров первой группы соединены с входами блока кон троля цифрового кода, а входы полу-. сумматоров остальных групп, кроме первой, соединены с выходами сумм полусумматоров предыдущей группы f1).

Недостатком этого устройства asляются ограниченные функциональные возможности.

Цель изобретения — расширение функциональных возможностей.

Поставленная цель достигается тем: что в блок контроля цифрового кода, содержащий элемент ИЛИ и группы полу- сумматоров, выходы переносов которых соединены с входами элемента ИЛИ, входы полусумматоров первой группы соединены с входами блока контроля цифрового кода, а выходы полусумматоров остальных групп, кроме первой соединены с выходами сумм полусумма» торов. предыдущей группы, введены ин+ вертор и элемент И, выход и первый вход которого соединены соответственно с дополнительним выходом бло15 ка контроля цифрового кода и выходом инвертора, вход которого соединен с выходом элемента ИЛИ, а второй .. вход элемента И соединен с выходом суммы полусумматора старшей группы.

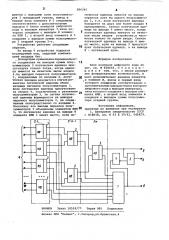

2О На чертеже показана структурная схема блока контроля цифрового кода

Блок контроля цифрового кода со; держит элемент ИЛИ 1 и группы 2-1-2-п полусумматоров 3, выходы переносов которых соединены с входами элемента ИЛИ 1, входы полусумматоров первой группы 2-1 соединены с входами 4 блока контроля цифрового кода, а входы полусумматоров 3 бсЗО тальных групп, кроме первой, сое886245

Формула изобретения

2-f

1 у) 1

ВНИИПИ Заказ 10559/77 Тираж 991 Подписное

Филиал ППП "Патент", r.ужгород,ул.Проектная,4 динены с выходами сумм полусумматоров 3 предыдущей группы, выход и первый вход элемента И 5 соединены соответственно с дополнительным выходом б блока контроля цифрового кода. и выходом инвертора 7,вход которого соединен с выходом 8 элемента ИЛИ 1, а второй вход элемента И 5 соединен с выходом суммы полусумматора 3 старшей группы 2-п.

Устройство работает следующим образом.

На входы 4 устройства подается исследуемый код, заданный комбинацией входных бит.

Вследствие приме не ни я пирамидаль ного соединения на выходах суммы полусумматоров 3 логическая единица присутствует только тогда, когда единица имеется на нечетном числе входов

4.На выходах переноса полусумматоров

3, сбединенных со входами 4, логическая единица находится в случае равенства логической единицы обоих входных сигналов полусумматоров 3.

Если логические единицы присутствуют на входах 4, подключенных к различным полусумматорам 3, то сигнал логической единицы формируется на выходах переноса полусумматоров 3, не соединенных непосредственно со входами 4.

Поскольку все выходы переноса полусумматоров 3:объединены элементом ИЛИ

1 то логическая единица на выходе 8 элемента ИЛИ 1 имеет место, если логическая единица имеется на выходе переноса хотя бы одного полусумматора 3, т.е. если логическая единица находится на двух или более входах 4 одновременно. Сигнал логической единицы на выходе 9 имеет место, когда логическая единица имеется на нечетном числе входов устройства,в частности только на одном входе. Сигнал логической единицы на выходе б имеет место,, если на выходе 9 присутст

1О вует логическая единица, а на выходе

8 — логический нуль.

Блок контроля цифрового кода по авт. св. Ф 818018, о т л и ч а ю— шийся тем, что, с целью расширения функциональных возможностей, в

;@ него дополнительно введены инвертор ,и элемент И, выход и первый вход которого соединены соответственно с дополнительным выходом блока контроля цифрового кода и выходом инверторар вход которого соединен с выходом элемента ИЛИ, а второй вход элемента И соединен с выходом суммы полусумматора старшей группы.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР.(:. 818018, кл. Н 03 К 19/42, 0404.79.