Устройство для защиты от импульсных помех

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Социаиистичаскик

Республик

< 886259

{бт) Дополнительное к авт. сеид-ву ¹ 661822 (22) Заявлено 01.02. 80 {21) 2879200/18.-09 с присоединением заявки М (23) Приоритет

Опубликовано 30.11. 81. бюллетень М 44

Дата опубликования описания 02. 1 2. 81 (5I)M. Кл..

Н 04 В 1/10

Ркударетеанвй квинтет

СССР кв делам кзебретекк% к етернткк (53) УДК 621 396 .621 (088 8) В. А. Ларионов, В. А. Гусев, А. С. Панфилов, В. E. Пониматкин и Я, A. Собенин (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ОТ ИМПУЛЬСНЫХ

ПОМЕХ

Изобретение относится к радиотехнике и может быть использовано прк разработке устройств приема и обработки сигналов.

По основному авт. св. % 661822 известно устройство для зашиты от кмпульсных помех, содержашее первый ключ, инS формационный вход которого подключен ко входу устройства через первый элемент задержки,. сумматор, второй вход которого подключен ко входу устройства через е второй ключ, фильтр и последовательно соединенные детектор, дискретизатор, второй элемент задержки, усилитель, блок сравнения, второй вход которого подключен к выходу дискретизатора, третий эле !

% мент задержки, блок совпадения, второй вход которого соединен с выходом блока сравнения и управляюшим входом второго ключа 13.

Однако известное устройство обладает недостаточной помехоустойчивостью, так как не устраняется эффект последействия импульсной помехи.

Цель изобретения - повышение помехоустойчивости.

Поставленная цель достигается тем, что в устройстве для защиты от импульсных помех, содержащем два ключа, три элемента задержкк, сумматор, фильтр, детектор, дискретизатор, блок сравнения, блок совпадения и усилитель, между выходом сумматора и входом фильтра включены последовательно управляющий элемент, первый дополнительный ключ, дополнительный элемент задержки и второй дополнительный ключ, причем сигнальный вход второго дополнительного ключа подключен к выходу сумматора, а управляющий вход первого дополнительного ключа объединен с управляющим входом управляющего элемента и подключен к выходу второго ключа.

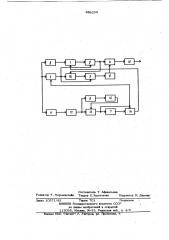

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство содержит ключи 1 - 4, / элементы 5 - 8 задержки, сумматор 9, 886259 фильтр 10, детектор 11, дискретизатор

12, блок 13 сравнения, блок 14 совпад ния, усилитель 15 и управляющий элемент

16.

Устройство. работает следующим обраэом.

Входной процесс одновременно поступает на входы первого элемента 5 задержки, второго ключа 2 и детектора 1 1, с выхода которого - на дискретизатор 1 2, 10

° осуществляющий дискретизацию входного процесса с интервалом дискретизации, равным интервалу разрешения. Отсчеты полученной выработки поступают на второй элемент 6 задержки и соответствующий вход блока 3 сравнения.

Задержаннъ и с помощью второго элемента задержки сигнал через усилитель

15 поступает на второй вход блока 13 сравнения. zo

Результат сравнения значения текущего элемента выборки У; с умноженным на коэффициент усиления предшествующим элементом с g c выхода блока 13 сравнения поступает на управляющий вход вто- у3 рого ключа 2, вход третьего элемента 7 задержки и соответствующий вход блока

14 совпадения, на второй вход которого поступает сигнал с выхода третьего элемента 7 задержки, 30

Второй ключ 2 обеспечивает прохождение входного процесса в s -й момент времени при условии превышения значени-ем задержанного элемента выборки с М„4 значения текущего элемента выборки 1(;

Лервый ключ 1 обеспечивает прохождение элемента выборки У» л с выхода первого элемента 5 задержки в том случае, если текущий и предшествующий результаты сравнения соответствуют условию превышения 40 значения текущих (для каждого этапа сравнения) элементов выьорки Y и 9»„ предшествующих значений элементов с

Y < и cV< g соответственно. Сигналы с вйходов ключей 1 и 2 поступают на вход

4S сумматора 9, с выхода которого сигнал

4 поступает на сигнальный вход второго дополнительного ключа 4 и первый вход управляющего элемента 16. Последний открывает первый дополнительный ключ 3, если на первом входе управляющего элемента 16 нуль, а на втором - напряжение, отличное от нуля. Это состояние управляющий элемент сохраняет до поступления нуля на его второй вход с, выхода второго . ключа 2. Сигнал с выхода второго ключа

2 поступает на дополнительный элемент

8 задержки через открытый первый дополнительный ключ 3 и с задержкой на один дискрет запирает второй дополнительный ключ 4, подавляя эффект последействия импульсной помехи. Сигнал с выхода второго дополнительного ключа 4 поступает на фильтр 10.

Таким образом подавляется не только пиковое значение импульсной помехи, но и последующие эффекты ее воздействия на сигнал.

Формула изобретения

Устройство дпя .зашиты от импульсных помех по авт. св. М 661822, о т л ичающееся тем, что, сцельюповы щения помехоустойчивости, между выходом сумматора и входом фильтра включе.ны последовательно управляющий элемент,,первый дополнительный ключ, дополнитель ный элемент задержки и второй дополнительный ключ, причем сигнальный вход второго дополнительного ключа подключен к выходу сумматора, а управляющий вход первого дополнительного ключа объединен с управляющим входом управляющего элемента и подключен к выходу второго ключа..Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

hb 661822, кл. Н 04 В 1/10, 1977 (прототип ).

886259

Составитель Т. Афанасьева

PeдактоР T. Мермелштайн Техред E. Харитончик Корректор М. Демчик

Заказ 10571/83 Тираж 701 Подписное

ВНИИПИ Государственного комитета СССР по делам. изобретений и открытий

113035; Москва, Ж-35, Раушская наб., д..4/5 атент . г. жгород; ул. роектная,