Устройство для регулирования коэффициента передачи измерительного канала

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

Е. А. Дерденков и К. M. Терещук (7I) Заявитель (54) УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ КОЭФФИЦИЕНТА

ПЕРЕДАЧИ ИЗМЕРИТЕЛЬНОГО КАНАЛА

Изобретение относится к измерительной технике и может использоваться в системах сбора и обработки экспериментальных данных при преобразовании сигнала, изменяющегося в широком амплитудном диапазоне, например, при

5 вибрационных и. ударных испытаниях.

Известно устройство для регулирования коэффициента передачи измерительного канапа, содержащее блок задерж10 ки, выход которого подключен ко входу усилителя, другой вход которого соединен с выходом амплитудного дискриминатора, и ключ (11 .

IS

Однако известное устройство характеризуется невысокой точностью регулирования коэффициента передачи.

Цель изобретения — повышение точности регулирования.

Для достижения поставленной цели в устройство для регулирования коэффициента передачи измерительного канала, содержащее блок задержки, выход которого подключен ко входу усилителя. другой вход которого соединен с выходом амппитудного дискриминатора, и ключ, введены выпрямитель, пиковый детектор, блок формирования. стробирующего импульса, компаратор, первый и второй запоминающие элементы и блок синхронизации, при этом вход выпрямителя объединен со входом блока задержки, выход выпрямителя подключен ко входу пикового детектора, входу -ключа и входу первого запоминающего элемента, выход которого подключен ко входу компаратора и входу второго запоминающего элемента, другой вход которого соединен с выходом блока синхронизации, другой выход которого подключен ко второму входу первого запоминающего элемента, выход компаратора, другой вход которого соединен с выходом второго запоминающего элемента, через блок формирования стробирующего импульса подключен к другому входу ключа, выход которого, объединенный с

8862

Блок 11 синхронизации формирует тактовые импульсы, частота повторения

И которых значительно превышает частоту наиболее высокочастотной гармоники в спектре. входного сигнала. Причем тактовые импульсы на входы управления запоминающих элементов 9 и 10 поступают поочередно, т. е. в первом такте информация заносится с выхода выпрямителя 3 в запоминаюший элемент 9, а в следующем такте эта информация с выховыходом пикового детектора, подключен ко входу амплитудного дискриминатора.

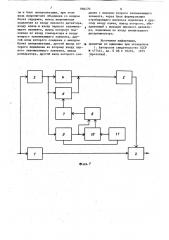

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 — временные диаграммы, поясняющие его работу.

Устройство содержит блок 1 задержки, усилитель 2, выпрямитель 3, пиковый детектор 4, амплитудный дискриминатор 5, ключ 6, блок 7 формирования 10 стробирующего импульса, компаратор 8, запоминающие элементы 9, 10 и блок 11 синхр они з ации .

Предлагаемое устройство работает следующим обр азом.

Рассмотрим работу устройства на примере конкретного сигнала, характер- ный вид которого приведен на фиг. 2а.

Выпрямитель 3 осуществляет выпрямпение

Я входного сигнала и на его выходе он щ имеет вид Ugqipp. (фиг. 2б) .

На интервале времени (to, t, ) на выходе выпрямителя 3 присутствует нулевой сигнал, который одновременно поступает на входы пикового детектора 4, 25 ключа 6 и запоминающего элемента 9.

В соответствии с этим сигнал на выходе пикового детектора 4, а следовательно, и на входе амплитудного дискриминатора 5 также равен нулю. на данном интер- 3О вале времени. При этом на выходе амплитудного дискриминатора 5 сформирован сигнал, соответствующий максимальному. коэффициенту передачи усилителя 2.

В запоминающий элемент 9 сигнал с выхода выпрямителя 3 заносится только при поступлении тактового импульса с выхода блока 11 синхронизации на вход управления запоминающего элемента 9, который выполняет функцию дискретизатора сигнала Ug»» . Запоминающий элемент 10 работает аналогичным образом, воспринимая информацию с выхода запоминающего элемента 9 только при поступлении на его вход управле45 ния тактового импульса с выхода блока

11.синхронизации.

70 4 да запоминающего элемента 9 переносится .в запоминающий элемент 10. Таким образом, периодически происходит запоминание значения амплитуды входного сигнала в запоминающем элементе 9 и

его последовательный сдвиг в запоминающий элемент 10.

На интервале времени (й,1,) на выходе запоминающих элементов 9 и 10 присутствует нулевой сигнал, так как сигнал О ыпр. имеет нулевую величину.

Поэтому на входы компаратора 8 поступает нулевой сигнал. Однако за счет начального смещения по входу компаратор 8 находится в исходном состоянии и на его выходе присутствует нулевой потенциал, который поступает на вход блока 7 формирования стробирующего импульса, причем на выходе его также присутствует нулевой потенциал, за

° счет. которого ключ. 6 находится в закрытом состоянии.

С поступлением в момент времени с выхода выпрямителя 3 первой полуволны сигнала .0щяр. происходит заряд пикового детектора 4 до величины, равной максимуму этой полуволны. Одновременно с этим сигнал Ugq q .с выхода выпрямителя 3, как было показано выше, поступает на вход запоминающего элемента 9. заносится в него в виде дискретных значений амплитуды и продвигается в запоминакиций элемент 10 в соответствии с поступлением тактовых импульсов с выхода блока 11 синхронизации. Очевидно, что при возрастании сигнала на выходе запоминающего элемента 9 величина сигнала всегда больше, чем величина сигнала на выходе запоминающего элемента 10, следовательно, срабатывания компаратора 8 не происходит и на его выходе сохраняется исходный потенциал.

В момент времени t когда сигнал

0щ, яр., достигнув максимума, начинает убывать, на выходе запоминающего элемента 9 величина сигнала становится меньше, чем величина сигнала на выходе запоминающего элемента 10. При этом компаратор .8 срабатывает и на

его выходе формируется положительный перенад напряжения, по которому на выходе блока формирования стробирующего импульса 7 формируется стробимпульс малой длительности (фиг. 26) и поступает на вход управления ключа

6. На время действия стробимпульса ключ 6 открывается, шунтируя при этом выход пикового детектора 4 с его вхоФормула изобретения

5 8862 дом и обеспечивает снижение сигнала на выходе пикового детектора 4 до величины сигнала на его входе. Однако в момент времени t величины сигналов на входе и выходе пикового детектора 5

4 практически одинаковы, т. е. величина сигнала на его выходе остается неизменной.

По окончании действия стробимпульса с выхода блока формирования строби- 16 руюшего импульса.7 ключ 6 закрывается.

Очевидно, что чем выше частота такто.вых импульсов блока синхронизации 11, тем точнее к моменту времени t (поло.—

2 жительного экстремума) формируется 15 стр обимпульс .

В момент времени перехода сигналом

U щ,щр. точки отрицательного экстремума на выходе запоминающего элемента 3 величина сигнала вновь становится 20 больше, чем величина сигнала на выходе запоминающего. элемента 10. Компаратор 8 срабатывает, формируя на своем выходе отрицательный перепад напряжения. Однако в этом случае фор- И мирования стробимпульса не происходит, ключ 6 остается закрытым и величина напряжения на выходе пикового детектора 4 не изменяется.

Далее с поступлением с выхода вы- 5ф прямителя 3 очередных полуволн сигнала (кривая 0 выдр на фиг. 2б) устройство работает аналогичным образом. В момент времени t в еличина напряжения на выходе пикового детектора 4 (кривая 55

U gg. на фиг. 26)превышает пороговый уровень 0 pgp амплитудного дискриминатора 5. При этом на выходе амплитудного дискриминатора 5 формируется новый сигнал, по которому усилитель 2 переключается на более низкий коэффициент передачи.

В момент времени t<, когда амплитуда очередной полуволны сигнала Ues>np. становится меньше, чем амплитуда предыдущей, полуволны, вновь срабатывает компаратор 8, блок формирования стробирующего импульса 7 формирует очередной стробимпульс, по которому ключ 6 шунтирует пиковый детектор 4, При этом происходит быстрый разряд напряжения на выходе пикового детектора 4 через малое выходное сопротивление выпрямителя 3 до величины, равной максимуму полуволн сигнала 0 выпр в момент

S5 времени t5 (фиг. 26) . Аналогичным, образом через ключ 6 происходит разряд напряжения на выходе пикового детектора 4 в момент времени te. В этот мо70 Ь мент времени сигнал 0я вновь становится меньше уровня 0 пор. (фиг. 26), т. е. на выходе амплитудного дискримн . натора 5 формируется сигнал, по которому усилитель 2 вновь переключается на более высокий коэффициент передачи.

Таким образом, на интервале времени (t, t6) в соответствии с характе" ром входного сигнала устройство рабо-. тает с пониженным коэффициентом пере-, дачи, Далее устройство аналогичным образом функционирует на интервале времени (t>, t ), переключаясь на пониженный коэффйциент передачи, но уже для более высокочастотного процесса (фиг. 2) .

Заметим, что в моменты времени t и t7 осуществляется безынерционное переключение устройства на более низкий коэффициент передачи, а в моменты.времени t< и t$ осуществляется инерционное обратное переключение устройства на более высокий коэффициент передачи (фиг. 2г), Время инерционной задержки обратного переключения адаптивно изменяется с изменением частотных свойств

l входного сигнала. При этом величина инерционной задержки обратного переключения (т. е. время работы с заниженным коэффициентом передачи) не превышает длительности полупериода входного сигнала.

Применение предлагаемого устройства позволяет заметно повысить точность регулирования коэффициента передачи эа, счет адаптивного изменения времени инерционной задержки в соответствии с параметрами входного сигнала. В результате погрешность измерения сигналов, изменяющихся в широком. динамическом диапазоне, удается снизить в

2-3 раза.

Устройство для регулирования коэффициента передачи измерительного канала, содержащее блок задержки, выход которого подключен ко входу усилителя, другой вход которого соединен с выходом амплитудного дискриминатора, и ключ, о т л и ч а ю щ е е с я тем, что, с целью повышения точности регулирования, в него введены выпрямитель, пиковый детектор, блок формирования стробирующего импульса, компаратор, первый и второй запоминающие элемен886270 ты и блок синхронизации, при этом вход выпрямителя объединен со входом блока задержки, выход выпрямителя подключен ко входу пикового детектора, входу ключа и входу первого запоминающего элемента, выход которого подключен ко входу компаратора и входу второго запоминающего элемента, другой вход которого соединен с выходом блока синхронизации, другой выход ко- 1е торого подключен ко второму входу первого запоминающего элемента, выход компаратора, другой вход которого соединен с выходом второго запоминающего элемента, через блок формирования стробирующего импульса подключен к. другому входу ключа, выход которого; объединенный с выходом пикового детектора, подключен ко входу амплитудного дискриминатора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

В 477441, кл. G 08 С 19/02, 1975 (прототип), Ф

886270 а)

Фив.й

Тираж 701 Подписное

ВНИИПИ Государственного коиитета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 10572/84

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель Л. Казакова

Редактор Л. Пчелинская Техред P.Îëèÿí Корректор С. Шоиак