Система для передачи и приема дискретной информации

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ИТИЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. саид-sy (22) 3assneHo 180380 (21) 2894737/18-09 с присоединением заявки М9(23) Приоритет—

Опубликовано 301181. Бюллетень N9 44

Дата опубликования описания 30,1181 (51)М К„З

Н 04 17/00//

Н 04 L 3/00

Государственный комитет

СССР но делам изобретений н открытий (53) УДК 621.394.14 (088. 8) О.С. Когновицкий и Б.Н..Сюрин

Ленинградский электротехнический-инвижзут. а им. проф. M.A. Бонч-Бруеяича (72) Авторы изобретения (71) Заявитель (54) CHCTEMA ДЛЯ ПЕРЕДАЧИ И ПРИЕИА ДИСКРЕТНОЙ

ИНФОРИ ЦИИ

Изобретение относится к электросвязи

Известна система для передачи и приема дискретной информации, содержащая на передающей стороне информационный канал, состоящий из последовательно соединенных вычитающего счетчика, дешифратора и инвертора, блока совпадения, выходом соединенного с входом вычитающего счетчика, регистра сдвига, выходом соединенного с входом элемента задержки, на приемной стороне - последовательно соединенные блок выделения псевдослучайной последовательности, выходом соединенный с одним входом сумматора по модулю два, инвертор, выходом соединенный с входом счетчика, а в каждом канале — генератор псевдослучайной последовательности, выход которого соединен с входом блока сравнения, а также суммирующий счетчик, подключенный к накопителю (1).

Однако в известной системе недостаточная пропускная способность.

Цель изобретения - повышение пропускной способности.

Для достиженйя поставленной цели в систему для передачи и приема дискретной информации, содержащую на ЗО передающей стороне инфбрмационный канал, состоящий из последовательно соединенных вычитающего счетчика, дешифратора и инвертора, блока совпадения, выходом соединенного с вхо.дом вычитающего счетчика, регистра сдвига, выходом соединенного с входом элемента задержки, на приемной стороне — последовательно соединенные блок выделения псевдослучайной последовательности, выходом соединенный с одним входом сумматора по модулю два, инвертор, выходом соединенный с входом счетчика, а в каждом канале— генератор псевдослучайной последовательности, выход которого соединен с входом блока сравнения, а также суммирующий счетчик, подключенный к накопителю, введены на передающей стороне информационный канал, идентичный первому; а в каждом канале выход инвертора соединен с входом блока совпадения, а также общий сумматор по модулю два, входы которого соединены с выходами элементов задержки обоих информационных каналов, на приемной стороне введены последовательно соединенные блок опознавания псевдослучайной последовательности, ключ и блок умножения. а в каждый

886296 канал - блок управления, причем вы ход блока выделения псевдослучайной последовательности соединен с.вхо дом блока опознавания псевдослучайной последовательности, выход которого соединен с входом инвертора, выход счетчика соединен с другим .входом ключа и одним входом блоков управления обоих каналов, выход блока умножения соединен с другими вхо дами блоков сравнения, в каждом ка нале выход блока сравнения через блок управления соединен с объединен- ными входами:суммирующего счетчика и генератора псевдослучайной последовательности.

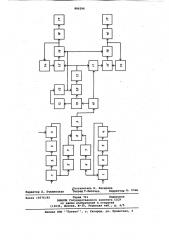

На чертеже изображена структурная электрическая схема предлагаемой системы.

Система содержит на передающей стороне вычитающий счетчик 1 дешифратор 2, инвертор 3, блок 4 совпадения, регистры 5 и 6 сдвига, элементы 7 задержки, сумматор 8 по модулю два, канал 9 связи, на приемной стороне — блок 10 выделения псевдослучайной последовательности, сумматор

11 по модулю два, инвертор 12, счетчик 13, а в каждом канале генератор

14 псевдослучайной последовательности, блок 15 сравнения, суммирующий счетчик 16, накопитель 17 и блок 18 управления, блок 19 опознавания псев« дослучайной последовательности, ключ

20 и блок 21 умножения.

Предлагаемая система работает следующим образом.

По команде с управляющего ycгройства (не показано) в ячейки двоичных вычитающих счетчиков 1 обоих каналов записываются комбинации первичного кода от двух различных источников информации, работающих с одина ковой скоростью. Если записанные комбинации отличаются от нулевых, то на выходах дешифраторов 2 появляются нулевые сигналы, которые инвертируются инверторами 3 и открывают блоки.

4 совпадения, через которые проходят быстрые тактовые импульсы, частота следования которых не менее чем в

N раз превышает номинальную тактовую частоту (где N -, выраженная в числе элементов длина комбинации вторичного кода, передаваемого в канал связи 9) . Значение N должно удовлетворять неравенству М42"-1,где n — длина комбинации первичного кода.,Быстрые тактовые импульсы с выходов блоков 4 совпадения поступают на счетные входы двоичных вычитающих счетчиков 1 и на тактовые входы регистров 5 и 6 сдвига. Быстрые тактовые импульсы подаются до тех пор, пока вычитающие счетчики 1 не устанавливаются в нулевое состояние. В последнем случае на выходах дешифраторов 2 появляются единичные сигналы, кото; рые инвертируются инверторами 3 и

20 закрывают блоки 4 совпадения, что приводит к прекращению подачи быстрых тактовых импульсов (ТИ) на счетный вход вычитающих счетчиков 1 и на тактовые входы регистров 5 и 6 сдвига. Таким образом, количество поступивших на тактовые входы регистров 5 и б.сдвига быстрых ТИ зависит от того, какая комбинация первичного кода записана в ячейки соответствующего двоичного вычитающего счетчика

1.Под действием быстрых тактов за время, не превышающее периода номинальной тактовой частоты (длительности одной элементарной посылки), производится сдвиг фаз формируемой в регистре 5 .сдвига первой псевдослучайной последовательности (ПСП-1) и формируемой в регистре б сдвига второй псевдослучайной последовательности (ПСП-2) на число шагов, равное десятичным цифрам, соответствующим двоичным комбинациям первичного кода, записанным в двоичные вычитающие счетчики 1 соответственно обоих каналов.

Под действием ТИ номинальной частоты с выходов регистров 5 и б сдвига через элементы 7 задержки производится выдача ПСП-1 и ПСП-2 с новыми значениями фаз на входы сумматора 8 по модулю два, где они поэлементно складываются по модулю два и суммарная последовательность поступает далее на вход канала 9 связи. Принимаемая с выхода канала 9 связи суммарная последовательность поступает на вход блока 10. С выхода блока 10 последовательность, сдвинутая по фазе относительно принимаемой в составе суммарной последовательности, поступает на вход блока 19. Если на вход приемника поступает .последовательность, 40 не содержащая ошибок или содержащая безошибочный участок длиной 1=2п+К, где К вЂ” емкость счетчика, n .- коли чество разрядов рекуррентного регистра), то с выхода блока 19 через 2п тактов следует нулевая последовательность. Эта последовательность нулей инвертируется инвертором 12 и поступает на счетный вход счетчика 13 емкостью К, где К вЂ” больше нуля. При этом происходит заполнение счетчика

13, сигнал с выхода которого открывает ключ 20 и параллельно поступает на первые входы блоков 18 управления обоих каналов. Безошибочный иэлементный участок первой рекурренткой последовательности ПСП-1 с ячеек блока 19 последовательность поступает через открытый ключ 20 на блок

21 умножения, выполняющий функцию обратного сдвига фазы ПСП-1 до сов49 падения с фазой ПСП-1, принимаемой в составе суммарной последовательности. Сформированный на выходе. блока

21 умножения и-элементный участок

ПСП-1 и и-элементный участок суммар-

Я ной последовательности с выхода бло886296 ка 10 соответственно поступают на входы сумматора 11, при. этом на его выходе Формируется безошибочный иэлементный участок ПСП-2, принятый из канала связи в составе суммарной последовательности. Также после за.полнения счетчика 13 с его выхода поступает сигнал на первые входы . блоков 18 управления, которые, в свою очередь начинают вырабатывать быстрые тактовые импульсы, .поступающие на тактовые входы генераторов

14 соответственно и на счетные вх0l ды суммирующих счетчиков 16 соответствующих каналов. Под воздействием быстрых тактовых импульсов генераторы 14, а также суммирующие счетчики 15

16 начинают последовательно изменять свои состояния с высокой частотой.

При передаче быстрых ТИ суммирующие счетчики 16 находятся в исходном состоянии, генераторы 14 ра- 20 ботают с номинальной частотой. Формирование в каждом иэ каналов быстрых ТИ продолжается до тех пор, пока не происходит совпадения фаз, выделенных ПСП-1 и ПСП-2 с Фазами сиг- 25 налов, вырабатываемых соответствующими генератОрами 14. Последовательности в каждом из каналов поступают на соответствующие блоки 15 сравнения и в момент совпадения фаз на

30 их выходе вырабатываются сигналы, поступающие на вторые входы блоков

18. управления, которые в свою очередь, прекращают формирование быотрых тактовых импУльсов. Число быстрых тактовых импульсов, подсчитанное суммирующими счетчиками 16 соответствующих каналов, представляет собой комбинации первичного кода, введенные на передаче. С выхода суммирующих счетчиков 16 информация не- 40 посредственно или через накопители

17 выдается потребителям. После выдачи информации устройство на приемной стороне возвращается в исходное состояние. 45

Предлагаемое устройство позволяет увеличить пропускную способность системы.

Формула изобретения

Система для передачи и приема дискретной информации, содержащая на пе- 5

50 редающей стороне информационный канал, состоящий из последовательно соединенных вычитающего счетчика, дешифратора и инвертора, блока совпадения, выходом соединенного с входом вычит;,ющего счетчика, регистра сдвига, выходом соединенного с входом элемента задержки, на приемной стороне - последовательно соединенные блок выделения псевдослучайной последовательности, выходом соединенный с одним входом сумматора,:пo модулю два, инвертор, выходом соединенный с входом счетчика, а в каждом. канале— генератор псевдослучайной последовательности, выход которого соединен с входом блока сравнения, а также суммирующий счетчик, подключенный и накопителю, о т л и ч а ю щ а я с s тем, что, с целью повышения пропускной способности, введены на передающей стороне информационный канал, идентичный первому, а в каждом канале выход инвертора соединен с входом блока совпадения, а также общий сумматор по модулю два, входы которого соединены с выходами элементов задержки обоих информационных каналов, на приемной стороне введены последовательно соединенные блок опознавания псевдослучайной последовательности, ключ и блок умноже-, ния, а в каждый канал — блок управления, причем выход блока выделения псевдослучайной последовательности соединен,с входом блока опознавания псевдослучайной последовательности, выход которого соединен с входом инвертора, выход счетчика соединен с другим входом ключа и одним входом блоков управления обоих. каналов, выход блока умножения соединен с другими входами блоков сравнения, в каждом канале выход блока сравнения через блок управления соединен с обьединенными входами суммирующего счетчика и генератора псевдослучайной последовательности.Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 642867, кл Н 04 Ь 17/00, 1976 (прототип).

886296,Составитель Н. Лазарева

Техред Т.Маточкин . Корректор " Стес

Редактор Л. Пчелинская

Филиал ППП Патент, r. Ужгород. Ул. Проектная, 4

Заказ 10576/85 Тираж 701 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5