Синхроселектор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ „886314

ИЗОБРЕТЕН ИЯ

Союз Советски к

Социалистических

Республик

К АВТОРСКОМУ СВИ4ЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 03.03.80 (21) 2890129/18-09. с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

Н 04 N 5/08

Гасударственный кемнтет

СССР (53) УДК 621,397 (088.8) Опубликовано 30 11.81. Бюллетень № 44

Дата опубликования описания 05.12.81 по делам нзввретеннй и вткрмтнй (72) Авторы изобретения

В. П. Дворкович, (71) Заявитель (54) СИНХРОСЕЛЕКТОР

Изобретение относится к средствам селекции синхроимпульсов из полного телевизионного сигнала.

Известен синхроселектор, содержащий входной конденсатор, соединенный вторым выводом с параллельно включенными ограничителем и ключевым блоком фиксирующий диод, резонансный контур и усилитель-ограничитель (1).

Наиболее близким к предлагаемому является синхроселектор, содержащий вход10 нои конденсатор, первый вывод которого через предварительный селектор, дифференцирующий блок, формирователь и ключ подключен к первому входу порогового блока, а второй вывод подключен через буферный усилитель, пик-детектор, фильтр и делитель напряжения ко второму входу порогового блока, а непосредственно — к первому его входу (2).

Недостатком известных синхроселекторов является нарушение выделения синхроимпульсов при их малой величине. 20

Цель изобретения — повышение устойчивости селекции сийхроимпульсов при Их малой величине- в зашумленном сигнале.

Поставленная цель достигается тем, что в синхроселекторе, содержащем входной конденсатор, второй вывод которого подключен к последовательно .соединенным усилителю и пик-детектору, а также к первому входу порогового блока, дифференцирующий блок, делитель напряжения, выход которого подсоединен ко второму входу по- . рогового блока, и, ключ, усилитель выполнен дифференциальным, неинвертирующий вход его заземлен, выход пик-детектора через резистор обратной связи соединен со вторым выводом входного конденсатора, который подключен также к первому входу ключа, выход которого соединен со входом делителя напряжения, а управляющий вход которого подключен к выходу дифференцирующего блока, вход которого соединен с выходом дифференциального усилителя.

При этом делитель напряжения выполнен на конденсаторе с параллельно подключенными к нему двумя последовательно соединенными резисторами, средняя .точка подключения которых является выходом делителя.

886314

Предлагаемый селектор позволяет обеспечить выделение синхроимпульсов прк их малой величине в ТВ сигнале и при наличии значительного уровня помех за счет фиксации уровня синхронизирующих импульсов

ТВ сигнала методом компенсационного детектирования и изменения уровня ограничения в зависимости от размаха синхроимпульсов в ТВ сигнале.

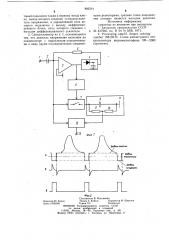

На фиг. 1 представлена структурная схема синхроселектора; на фиг. 2 — диаграм- 10 мы, поясняющие его работу.

Синхроселектор содержит на входе 1 конденсатор 2, второй вывод которого подключен к одному из входов дифференциального усилителя (ДУ) 3, второй вход кото15 рого заземлен. Выход ДУ подключен к упомянутому выводу конденсатора 2 через пиковый детектор (ПД) 4 и резистор 5. Кроме того, выход ДУ соединен через дифференцирующий блок (ДБ) 6 с управляющим входом ключа 7. Ключ 7 соединяет первый 20 вход ДУ 3 с параллельно включенными вторым конденсатором 8 и резисторами 9 и

10 делителя 11 напряжения. Первый вход

ДУ подключен также к первому входу порогового блока 12, на второй вход которого поступает напряжение с делителя напряже25 ния. На выходе порогового блока 12 выделяются синхроимпульсы.

Синхроселектор работает следующим образом.

На вход 1 поступает полный ТВ сигнал (фиг. 2а). Этот сигнал подается через конденсатор 2 на инверсный вход ДУ 3, прямой вход которого заземлен.

Инверсный вход ДУ соединен с его выходом через ПД и 4 и резистор 5. Схема, содержащая ДУ 3, ПД 4 и резистор 5, представляет собой компенсационный детектор. В начальный момент подачи ТВ сигнала на вход ДУ, обладающего большим коэффициентом усиления, на его выходе выделяется усиленный и ограниченный ТВ сиг- 40 нал обратной полярности. При этом пиковый детектор заряжается и положительное напряжение обратной связи через резистор 5 поступает на вход ДУ. Указанное положительное напряжение будет изменять положение уровня синхроимпульсов ТВ сигна- 45 ла (фиг. 2а) до тех пор, пока он не станет равным уровню нулевого потенциала, соответствующего потенциалу прямого входа ДУ.

В этом случае на выходе ДУ 3 сигнал станет малым по величине и ПД 4 начнет разряжаться. Таким образом, в установив50 шемся режиме уровень синхроим пульсов на входе ДУ 3 будет соответствовать уровню нулевого потенциала. Точность этого соответствия определяется коэффициентом усиления ДУ и коэффициентом обратной связи.

На выходе ДУ выделяются усиленные и ограниченные вершины синхроимпугьсов

ТВ сигнала, которые подаются на ДБ 6.

На выходе ДБ формируется двухполярный сигнал (фиг. 26) . Импульсы отрицательной полярности этого сигнала несколько смещены относительно срезов синхроимпульсов ТВ сигнала за счет частотных свойств

ДУ и соответствуют передаче задних площадок строчных гасящих импульсов. Эти импульсы обеспечивают замыкание ключа 7.

Во время замыкания ключа конденсатор 8 заряжается до уровня гасящих импульсов и напряжение на нем оказывается равным размаху синхроимпульсов в ТВ сигнале.

Выделенное постоянное напряжение делится пополам резисторами 9 и 10 и поступает на второй вход порогового блока 12, на другой вход которого подается ТВ сигнал, уровень синхроимпульсов которого соответствует нулевому потенциалу. Таким образом, пороговый блок 12 всегда обеспечивает ограничение ТВ сигнала на уровне половины размаха синхроимпульсов (фиг. 2а) и их выделение на выходе 13 (фиг. 2в).

Использование компенсационного детектирования для фиксации уровня синхроимпульсов ТЬ сигнала позволяет обеспечить нормальное выделение синхроимпульсов при значительных низкочастотных помехах

Изменение уровня ограничения в зависимости от размаха синхроимпульсов во входном ТВ сигнале обеспечивают высокую помехоустойчивость синхроселектора.

Испытания предлагаемого синхроселектора показывают, что он обеспечивает устойчивое выделение синхроимпульсов при уменьшении их размаха во входном ТВ сигнале до 10 — 20 мВ (при размахе ТВ сигнала до 2В), а также при наличии фоновой помехи размахом до 1 В и квазипиковом размахе флуктуационной помехи, равном размаху синхроимпульсов. Это позволяет использовать предлагаемый синхроселектор в устройствах, в которых необходимо выделение синхроимпульсов при значительных изменениях ТВ сигнала.

Формула изобретения

1. Синхроселектор, содержащий входной конденсатор, первый вывод которого предназначен для подачи полного телевизионного сигнала, а второй вывод подключен к последовательно соединенным усилителю и пикдетектору, а также к первому входу порогового блока, дифференцирующий блок, делитель напряжения, выход которого подключен ко второму входу порогового блока, и ключ, отличающийся тем, что, с целью повышения устойчивости селекции синхроимпульсов при нх малой величине в зашумленном сигнале, усилитель выполнен дифференциальным, причем неинвертирующий вход

его заземлен, выход пик-детектора через резистор обратной связи соединен со вторым выводом входного конденсатора, ко886314 ень нченио ооонь ннооимп.

Фиг,2

Составитель В. Максимова

Техред А. Бойкас Корректор М Шароши

Тираж 701 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Редактор Ю. Ковач

Заказ 10592/86 торый подключен также к первому входу ключа, выход которого соединен со входом делителя напряжения, а управляющий вход которого подключен к выходу дифференцирующего блока, вход которого соединен с выходом дифференциального усилителя. 5

2. Синхроселектор по п. 1, отличающийся тем, что делитель напряжения выполнен на конденсаторе с параллельно подключенными к нему двумя последовательно соединенными резисторами, средняя точка подключения которых является выходом делителя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 437246, кл. Н 04 N 5/08, 1971.

2. Processing amplif. Ampex catalog

number 168130.01. Схема амплитудного синхроселектора видеомагнитофона VR — 2000 (прототип).