Преобразователь двоичного кода с масштабированием

Иллюстрации

Показать всеРеферат

Союз Советсиик

Социалистичвсиик

Рвс<ублии

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дополнительное к авт. свид-ву— (22) Заявлено 280380 (21) 2901085/18-24 (5 l ) M. Кд.

G 06 F 5/02 с присоединением заявки № аееударатееввы!1 квМитет

СССР вв делам иэабретение и атерытк!! (23) ПрморнтетОпубликовано 071281. Бюллетень № 45

Дата опубликования описания 0712.81 (53) УДК 681. 325 (088. 8) (72) Автор изобретения

A.Ï. Алексеев (7I) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА С МАСШТАБИРОВАНИЕМ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей в устройствах вывода информации.

Известно устройство преобразования двоичного кода в двоично-десятичный код с учетом коэффициента масштабирования P1), содержащее двоично-десятичный сумматор, дешифратор, коммутатор, декадный счетчик переполнений, блоки управления поразрядного умножения.

Недостаток данного устройства состоит в низком быстродействии и сложности управления.

Наиболее близким решением по техни- ческой сущности и достигаемому резул ьт ату я вляет ся у стройст во для масшт абиро вани я двоичного кода $ 2), содержащее распределитель импульсов, сумматор эквивалентов, блок деления

М на два и сдвиговый регистр.

Работа этого устройства основана на последовательном суммировании эквивалентов преобразуемого кода, образуемых путем последовательного де.ления на две величины старшего эквивалента и подаваемых на вход сумматора эквивалентов в соответствии с наличием единиц и нулей в преобразуемом двоичном коде.

Недостаток указанного устройства состоит в низкой надежности, связанной с тем, что при наличии нулей в преобразуемом коде к содержимому сумматора эквивалентов добавляется число нуль и в. относительно большом объеме аппаратуры.

Целью изобретения являются упрощение устройства и повышение его надежности °

Поставленная цель достигается тем, что преобразователь двоичного кода с масштабированием, содержащий распределитель импульсов, сумматор эк-вивалентов, выходы которого являются. выходами устройства, блок деления на два, информационные входы которого

888105 соединены с входами масштабной величины устройства, регистр сдвига, информационные входы которого являются информационными входами устройства, а управляющий вход регистра сдвига соединен с первым выходом распределителя импульсов, второй выход которого соеди» нен с управляющим входом блока деления на два, первая группа информационных входов сумматора является входом <р минимального значения масштабной величины устройства, дополнительно содержит элемент И, первый вход которого соединен с выходом регистра сдвига, второй вход соединен с третьим выходом распределителя импульсов, а выход элемента И соединен с управляющим входом сумматора эквивалентов, вторая группа информационных входов которого соединена с выходами блока деления го на два.

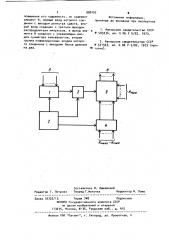

Блок-схема преобразователя с масштабированием двоичного кода приведена на чертеже.

Преобразователь содержит регистр 1 г5 сдвига, распределитель 2 импульсов, элемент И 3, блок 4 деления на два, сумматор 5 эквивалентов.

Преобразователь содержит двоичный регистр 1 сдвига, анализирующий состояние разрядов преобразуемого двоичного кода посредством его сдвига в сторону старшего разряда, информационные входы которого подключены к входам преобразователя, распределитель З5

2 импульсов, осущест вляющий формирование управляющих сигналов, первый и второй выходы которого соединены соответственно с управляющими входами регистра 1 сдвига (сдвиговый вход) и блока 4 деления на два, образующего эквивалентные значения весов преобразуемого кода в выбранной системе счисления, информационные входы которого подключены к входам масштабной величины преобразователя, а выходы - к второй группе информационных входов сумматора 5 эквивалентов, первые информационные входы которого подключены к входам задания минималь- Ж ного значения масштабной величины, выход старшего разряда регистра 1 и третий выход распределителя 2 соединены с соответствующими входами элемента И 3, выход которого соединен H с управляющим входом (вход записи) сумматора 5, выходы которого соединены с выходами устоойства.

Преобразователь работает следующим образом.

В регистр 1 вводится преобразуемое двоичное число А, а в блок 4 - эквивалентное значение веса старшего разряда преобразуемого кода в выбранной системе счисления N„„ „-й „, При намазе мин личии единицы в старшем разряде. преобразуемого кода содержимое блока 4 заносится в сумматор 5 посредством управляющего импульса, вырабатываемого распределителем 2 и поступающего на управляющий вход сумматора 5 через элемент И 3. После этого распределитель 2 вырабатывает импульсы для регистра 1 и блока. При наличии нуля в следующем разряде преобразуемого кода

его эквивалент, содержащийся в блоке

4, в сумматор 5 не заносится, так как управляющий импульс с распределителя

2 на управляющий вход сумматора 5 через элемент И 3 не пройдет. Процесс, аналогичный описанному, повторяется до тех пор, пока не будет проанализирован младший разряд преобразуемого кода. Содержимое сумматора 5 в виде преобразованного кода N подается на выход преобразователя. Предусмотрена возможность масштабирования для шкал с ненулевым началом отсчета - для этого на вход сумматора 5 подается код

"мин

Использование преобразователя позволит повысить коэффициент использования оборудования и надежность с сохранением, высокого быстродействия.

Формула изобретения

Преобразователь двоичного кода с масштабированием, содержащий распределитель импульсов, сумматор эквивалентов, выходы которого являются выходами преобразователя, блок деления на два, информационные входы которого соединены с входами масштабной величины преобразователя, регистр сдвига, информационные входы которого являются информационными входами преобразователя, а управляющий вход регистра сдвига соединен с первым выходом распределителя импульсов, второй выход которого соединен с управляющим входом блока деления на два, первая группа информационных входов сумматора является входом минимального значения масштабной величины преобразователя, отличающийся тем, что, с целью упрощения преобразователя и

888105

Яник

Составитель М. Аршавский

Редактор Г, Петрова Техред Т.Иаточка KoppeKTop M. Пожо

Заказ 10725/13. Тираж 748 Подпи сное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, M-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 повышения его надежности, он содержит элемент И, первый вход которого соединен с выходом регистра сдвига, второй вход соединен с третьим выходом распределителя импульсов, а выход элемента И соединен с управляющим входом сумматора эквивалентов, вторая группа информационных входов которого соединена с выходами блока деления на два.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

11 503234, кл. С 06 F 5/02, 1973.

2. Авторское свидетельство СССР

8 521563, кл. С 06 F 5/02, 1973 (npo14 тотип).