Устройство умножения

Иллюстрации

Показать всеРеферат

Союз Советских

Соцнаанстнческик

Реснублнк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ТВЛЬСТВУ (1) 888108 (61) Дополнительное к авт. сеид-ву (22) Заявлено 290679 (21) 2786004/18-24 с присоединением заявки Йо (23) Приоритет

Опубликовано 07.12,81.Бюллетень Н9 45

Дата опубликовамия описания 07. 12. 81 51)М Кдз

G 06 F 7/39

G 06 F 11/30

Государственный комитет

СССР но делам кзобретеннй н открытий (53) УДК 681.325 (088. 8) (72} Авторы изобретения

Г.Г.Алексеев, A. К. Варыбин, Е. A

Е.Г.Катковская, Ю.В.Кутыннн, атников, убботин (71) Заявитель (54) УСТРОЙСТВО УМНОЖЕНИЯ

Изобретение относится, к вычислительной технике.

Известно устройство умножения, содержащее регистр множимого, регистр множителя, дешифратор множителя и многоразрядную суммирующую схему (11 °

Наиболее близким техническим решением к изобретению является устройство для контроля арифметического блока. по модулю, содержащее блок сравнения контрольных кодов, подключенный входами к первому выходу бло-. ка управления, выходу блока сложения контрольных кодов, подключенного первым входом к второму. выходу блока управления, и выходу блока умножения контрольных кодов, один из входов которого соединен с первым . выхадом регистра множителя, второй выход которого подключен.к первому входу блока управления, соединенному третьим выходом через блок элементов И с вторым входом блока сложения контрольных кодов, третий вход которого подключен к выходу блока свертки, подключенного входами к четвертому выходу блока управления, одному из выходов сумматоров, подключенного другим входом и выходом к блоку управления, элемент И подключен к пятому выходу блока управления, элемент ИЛИ подключен входом к выходу элемента И и шестому входу блока управления и соединенный выходами с вторыми входами блока элементов И, схема совпадения соединена выходом с вторым входом элемента И, логический блок подключен входами к третьему выходу регистра множимого и выходу схемы совпадения и соединенным выходом с вторым входом блока умноженияЯ j.

Целью изобретения является повышение достоверности результата.

Для достижения поставленной цели устройство умножения, содержащее регистр множимого, регистр множителя, блок суммирования и дешифратор мно2О жителя, при этом выход регистра множнмого подключен к первому входу блока суммирования, второй вход которого подключен к выходу дешифратора множителя, вход которого соединен с выходом регистра множителя, первый выход блока суммирования является выходом устройства; блок подсчета коли чества переполнений, блок определения положительного результата и блок

ЗО определения количества отрицательных

888108 частичных произведений, при этом выход блока суммирования подключен к входу блока подсчета количества переполнений, выход которого соединен с ! . первым входом блока определения положительного результата, выход которого является выходом устройства, выход блока определения количества отрицательных частичных произведений подключен к входу блока определения положительного результата, второй выход дешифратора множителя соединен с входом блока определения количества отрицательных частичных произведений, с вторым выходом многорядной суммирующей схемы, а выход с первым входом блока определения положительного результата, вход блока определения количества отрицательных частичных произведений соединен с вторым выходом дешифратора ,множителя, а выход — -с вторым вхо- 20 дом блока определения положительного результата, выход которого является выходом устройства умножения.

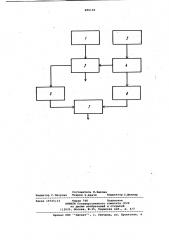

На чертеже представлена блок-схема предлагаемого устройства. . д

Устройство умножения содержит регистр 1 множимого, регистр. 2 множителя, многорядную суммирующую схему 3, дешифратор 4 множителя, блок 5 пбдсчета количества переполнений, блок 6 определения количества отрицательных частичных произведений, блок 7 определения положительного результата.

Первый выход многорядной суммирующей схемы и выход блока определения положительного результата являются выходами устройства.

При выполнеии операции умножения содержимое регистра множимого поступает на первый вход многорядной сум- 40 мирующей схемы в зависимости.от кода, выдаваемого с первого выхода дешифратора множителя и поступающего на второй вход многорядной суммирующей схемы. 45

Содержимое регистра множителя поступает на вход дешифратора множите-. ля, в котором происходит формирование управляющих сигналов для каждой пары разрядов множителя. В аТНх разрядах с равными вероятностями могут встретиться комбинации 00, 01, 10

11 °

Кодирование двух разрядов множителя можно представить следующим обРМом: 2 о

00=0 01=2, 10=2, 11=2 -2

В соответствии с этим представлением при дешифрации каждых двух разрядов множителя требуется произвести не более одного прибавления и вычита- 69 ния множимого.

В дешифраторе множителя расшифровывается комбинация из цифр, имеющихся в анализируемой паре разрядов множителя и в следующем разряде множителя.

При дешифрации каждой пары разрядов множителя необходимо производить не более одного прибавления или вычитания множимого или удвоенного множимого к сумме частичных произведений.

Информация о количестве отрицательных частичных произведений с выхода дешифратора 4 передается в блок б.

С выхода многоразрядной суммирующей схемы 3 в блок 5 передается информация о наличии переполнений при сложении частичных произведений.

Блоки 5 и б могут быть реализованы на стандартных суммирующих схемах.

С выходов блоков 5 и 6 информация поступает на входы блока 7. формула изобретения .Устройство умножения, содержащее регистр множимого, регистр множителя, блок суммирования и дешифратор множителя, при этом выход регистра множимого подключен к первому входу блока суммирования, второй вход которого подключен к выходу дешифратора множителя, вход которого соединен с выходом регистра множителя, первый выход блока суммирования является выходом устройства, о т л ич а ю щ е е с я тем, что, с целью повышения достоверности результата, оно содержит блок подсчета количества переполнений, блок определения положительного результата и блок определения количества отрицательных частичных произведений, при этом выход блока суммирования подключен к входу блока подсчета количества переполнений, выход которого соединен с первым входом блока определения положительного результата, выход которого является выходом устройства, выход блока определения количества отрицательных частичных произведений подключен к входу блока определения положительного результата, второй выход дешифратора множителя соединен с входом блока определения количества отрицательных частичных произведений. !

Источники информации, принятые во внимание при экспертизе

1. Карцев М.A. Арифметические устройства электронных цифровых машин .-М., Государственное издание физико-математической литературы, 1978.

2. Авторское свидетельство СССР

Р 411454, кл. G 06 F 11/06,1970 (про тотип) .

888108

Составитель Н. Быкова

Редактор Г. Петрова Техред З.фанта Корректор С.Шекмар

Заказ 10725/13 Тирам 748 Подписное

ВНКИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Уигород, ул. Проектная, 4