Процессор для вычисления элементарных функций

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii)888131 (6I ) Дополнительное к авт. саид-ву (22)Заявлено 11.11.79 (21) 2842574/18-24 с присоединением заявки РЙ (23) Приоритет

Опубликовано 07.12.81. Бюллетень Ме 45

Дата опубликования описания 09.12.81 (51)М. Кл.

6 06 Г 15/34

Гоеудератееииый квинтет

СССР

IIo делам каебретенкй и открытий (53) УДК 681..3(088.8) (72) Автор изобретения

3. С. Кузин (7I ) Заявитель

Ленинградское высшее инженерное морское училище им. С. О. Макарова (54) HPOHECCOP ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ

ФУНКЦИЙ

Изобретение относится к цифровой вычислительной технике и может бытЬ использовано в высокопроизводительных вычислительных машинах и в автономных вычислителях.

Известен процессор параллельного действия с накапливающим сумматором 11), который вычисляет эжментарные функции аппаратурным способом по последовательно-параллельному алгоритму. УсттО ройство -содержит. три параллельных накапливающих сумматора, выполненных на трех регистрах со счетным входом и одним общим управляющим регистром, а также приемный регистр и параллель15 ный сдвигатель.

Недостатком такого процессора является его низкая производительность.

Наиболее близким техническим решением к изобретению является процессор (2), выполняющий вычисление элементарных функций по параллельно-параллельному алгоритму и содержащий три параллельных накапливающих сумматора, два сдвигателя, ABB коммутатора, постоянное запоминающее устройство и устройство управления, первый и второй выходы которого соединены соответственно с первым и вторым входами сумматоров; третий и четвертый выходы устройства управления соединены соответственно с первыми входами сдвигателей и коммутаторов, а пятый выход соединен с постоянным запоминающим устройством, выход которого соединен с третьим входом первого накапливающего сумматора, а первые выходы сумматоров соединены с входом устройства управления.

Недостатком известного процессора является низкая производительность. Например, на этом процессоре вычисление элементарных функций типа Огсый

ОгСС05р6 Э по алгоритму цика за цифрой можно выполнить только за время четырех команд умножения, поскольку каждую итерацию приходится выполнять за два этапа. На первом этапе определяется знак операции, а на втором этапе

888131 производится собственно вычисление, причем, кажпая итерация, выполняется дваждыв

Можно повысить производительность процессора в два раза, если совместить по времени выполнение первого и второго этапов.

Целью изобретения является повышение быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее три сумматора, два сдвигareas, два коммутатора, блок памяти и блок управления, первый выход которого подключен к первым входам сумматоров, вторые входы которых соединены с вторым выходом блока управ лени я, ехоп которого сое динен с первыми выходами сумматоров, третий выход блока управления соединен с первыми входами сдвигателей, четвертый выход блока управления соединен с управляющими вхопами коммутаторов, пятый выход блока управления соединен

i с входом блока памяти, выход которого соединен с третьим вхопом первого сумматора, введен четвертый сумматор, первый и второй входы которого соединены с первым и вторым входами блока управления соответственно, третьи входы второго и четвертого сумматоров соединены с выходом первого сдвигателя, вход которого соединен с выходом первого коммутатора, третий вход третьего сумматора соединен с выходом второго сдвигателя; второй вход которого соединен с выходом второго коммутатора, первый и второй информационные входы которого соединены с вторыми входами второго и третьего сумматоров, первый и второй информационные входы первого коммутатора соединены со втсрыми выходами третьего и второго сумматоров соответственно.

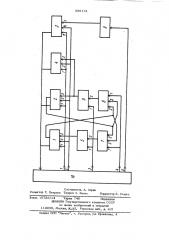

Елок-схема устройства представлена на чертеже.

Устройство содержит сумматоры 14, сдвигатели 5 и 6, коммутаторы 7 и

8, блок 9 памяти и блок 10 управления.

Блок 10 содержит генератор импульсов, дешифратор и группу элементов И HE„

Работу устройства рассмотрим на примере вычисления функций агсь! и, агссол, } а:,Я.

Известно, что по численному методу цифра за цифрой функцию огс1иможно вычислить с использованием следующих рекуррентных формул:

Х.=Х + } 2 }." ") } 1-1 1 1 1 (}) где Ц„. — угловые константы, вычисленные предварительно по формуле

8„.=9&4@g -1).

}О оператор поворота вектора, оп1 ределяющий знак в операции, f =+1, еслибы}.. <О V Х <0 иначе Я.= -1

1-1 1-1 1

Индекс 1 характеризует номер ите}$ рации, причем каждая итерация должна выполняться дважды. М аксимальное количество итераций определяется выбран— ной разрядностью И процессора, т.е. 1„„„„=

=И.

Линейные координаты вектора Х и У будем вычислять соответственно на сумматорах 1 и 2, а угловую координа- ту — на сумматоре 3. Включенный чет- вертый сумматор 4 позволяет свести операции определения знака f к простому анализу содержимого сумматоров

1 и 3. Для этого первые выходысумматоров соединены с вхопом блока управления, который на втором выходе формирует

30 соответствующее значение для каждого сумматора. Сдвинутые значения } . и

1-1

X. 1на (1 -1) разрядов вправо соответственно сдвигателями 5 и 6 поступают на третьи входы сумматора. Непосредственное выполнение сложениявычитания производится под воздействием синхронизирующих импульсов, постуI пающих на первые входы с первого выхода блока управления.

4О

Разрешение для сдвига операндов Х и У формируется третьим выходом блока управления, а четвертый выход формирует сигналы для коммутаторов 7 и 8, 4$ пропуская на вход спвигателя соответствующую координату вектора Х или У. Пятый выход устройства управления формирует адреса константы Ц., которые хра1ю нятся в постоянном запоминающем устройстве.

Начальные координаты вектора(ХО= 1!К, }сi=О,Хо=О7-< У)записываются а соответствующие сумматоры 1, 2, 3 и 4, гдето- коэффициент масштабирования, ко$$ торый вычисляется по формуле

М

К=п (4+9 2(1 }))

1=1

888 131

После вычисления р двойных итераций по формулам 1-4 получаем следующие результаты:

X =43-М =coo

И вЂ” МИ с(oL>--Огсв1п, .

ZwO °

Для вычисления функций ОГССо целе сообразно Хо=0 записывать во второй сумматор. Такой прием позволяет использовать всего одну связь третьего входа сумматора 4 с выходом только одного сдвигателя 6.

Таким образом, функциональные возможности процессора действительно позволили за время 2 И сложений-вычитаний

/ т.е. за время команд умножения вычисI лить одновременно три элементарные функции, что приводит к значительному повышению его производительности.

Формула изобретения

Процессор для вычисления элементарных функций, содержащий три сумматора, два сдвигателя, два коммутатора, блок памяти и блок управления, первый выход которого подключен к первым входам сумматоров, вторые входы кототорого соединены с вторым выходом блока управления, вход которого соединен с первым выходом сумматоров, третий выход блока управления соединен с первыми входами сдвигателей, четвертый выход блока управления соединен с управляющими входами коммутаторов, пяS тый выход блока управления соединен с входом блока памяти, выход которого соединен с третьим входом первого сумматора, от лича ющийс ятем, что, с целью повышения быстродействия, 10 в него введен четвертый сумматор, первый и второй входы которого соединены с первым и вторым выходами блока управления соответственно, третьи входы второго и четвертого сумматоров соединены с выходом первого сдвигателя, вход которого соединен с выходом первого коммутатора, третий вход третьего сумматора соединен с выходом второго сдвигателя, второй вход которого сое20 динен с выходом второго коммутатора, первый и второй информационные входы которого соединены с вторыми входами второго и третьего сумматоров, первый и второй информационные входы первого

>> коммутатора соединены с вторыми входами третьего и второго сумматоров соответственно.

Источники информации, принятые во внимание при экспертизе

30 1. Авторское свидетельство СССР

М 618740, кл. S 06 Р 7/38, 1978.

2, Авторское свидетельство СССР

M 525086, кл. О 06 F 7/38, 1976 (прототип) .

Составитель А, Зорин

Редактор Г. Петрова Техред 3. Фанта Ксрректор E. Рошко

Заказ 10726/14 Тираж 748 Поднисное

ЭНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж 35,. Раушская наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4