Устройство для временного сжатия входного сигнала

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (i))888165 (61) Дополнительное к авт. свид-ву (51)M. Кл3

G 0B С 19/00 (22) Заявлено 200380 (21) 2898832/18-24 с присоединением заявки Н9 (23) Приоритет

Опубликовано 07.1281Бюллетень @ 45

Дата опубликования описания 07.1281

Государственный комитет

СССР по делам изобретений н открытий (53) УДК 621 398 (088.8) (72) Авторы изобретения

Г.Г.Живилов, В.А.Прянишников и Н.М.Смета ин (71 ) 3a яв и тель (54) УСТРОЙСТВО ДЛЯ ВРЕМЕННОГО СЖАТИЯ ВХОДНОГО

СИГНАЛА

Изобретение относится к автоматике и вычислительной технике и предназначено для согласования полосы входного сигнала с полосой пропускания анализирующей и измерительной

5 аппаратуры.

Известно устройство для временного сжатия сигналов, содержащее несколько петель накопления с коммутатором и рециркуляционную линию задержки в каждой петле, используемую в качестве запоминающего .устройства, сумматор, выход которого является выходом устройства, блок управления, выходы элементов запоминания уровня напряжения и вход коммутатора первой петли накопления объединены и образуют входную шину устройства (1).

Известное устройство не может быть использовано для измерения характеристик периодических сигналов, так как не осуществляет выделение периода входного сигнала. Известное устройство автоматически не определяет оптимальное число фиксируемых точек за один период входного сигнала и, следовательно, в широком диапазоне частот изменяющаяся погрешность аппроксимации входного сигнала может оказаться выше допустимой. Это сужа- ЗО ет частотный диапазон сжимаемых входных сигналов, что является недостатком известного устройства.

Наиболее близким решением по технической сущности к изобретению является устройство для временного сжатия входного сигнала, содержащее блоки управления и блок памяти, выполненные с применением магнитострикционных линий задержки, причем входы магнитострикционных линий задержки блоков памяти соединены с помощью магнитострикционных линий задержки блока управления с выходами преобразователя аналог-код, а выходы соединены с входом преобразователя коданалог (2) .

Недостаток известного устройства заключается в том, что оно не может быть использовано для измерения характеристик периодических сигналов, так как оно не осуществляет выделение периода входного сигнала. При сжатии периодических сигналов, этим устройством, изменяется погрешность аппроксимации входного сигнала в зависимости от его частотного диапазона. Это сужает область применения устройства.

888165

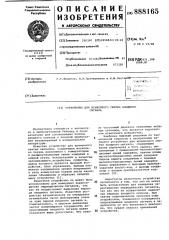

Устройство содержит преобразователь 1: аналог-код, оперативный запоминающий блок 2, преобразователь 3 код-аналог, блок 4 определения периода входного сигнала, блок 5 умножения частоты, блок 6 адресации, блок 7 управления.

Блок 5 выполнен на элементе И 8, счетчике 9 импульсов, управляющем счетчике 10, делителе 11, дешифраторе 12.

Блок 6 выполнен на счетчике 13, элементе 14 сравнения, регистре 15 записи, элементах ИЛИ 16, 17.

Предлагаемое устройство работает следующим образом.

Входной периодический сигнал поступает на вход преобразователя 1 аналог-код и блок 4. В блоке 4 фиксируется уровень, например нулевое значение, с которым сравнивается входной сигнал. Три пересечения зафиксированного уровня входным сигналом опреледяют период входного сигнала.

После запуска устройства и Сброса всех его блоков первый и второй выходы блока 5 заперты сигналами блока 7. Импульс начала периода входного сигнала с второго выхода блока 4 подается на первый вход. блошка 7, с четвертого выхода которого тактовая частота поступает на третий вход умножителя 5. С первого выхода блока 4 на первый вход блока 5 подается импульс, по длительности равный периоду входного сигнала. Начинается автоматическое :определение тактовой частоты запуска преобразователя 1 аналог-код и осуществляется выделение периода входного сигнала. Блок 5 формирует частоту запуска преобразователя 1 таким образом, что независимо от частоты входного сигнала его период делится на постоянное число. формирование частоты запуска преобразователя .1 заканчивается с приходом на первый вход блока 5 и на первый вход блока 7 сигналов конца периода входного сигнала (начала следующего периода). На следующем периоде входного сигнала блока 7 с шестого выхода подается разрешающий сигнал на четвертый вход блока 5 и с =ретьего выхода. — запрещающий сигнал на вход блока 5. При этом с первого выхода блока 5 на управляющий вход преобра-, зователя 1 подаются импульсы запуска, которые поступают также на четвертый вход блока 6 ° Импульсы запуска преобразователя 1 формируют в блоке б коды адресов, которые подаются с его выхода в блок 2. В блок 2 записываЦелью изобретения является расширение области применения устройства.

Эта цель достигается тем., что в устройство для временного сжатия входного сжгнала, содержащее преобразователь аналог-код, информационный вход которого соединен с входом устройства, выход — с информационным входом оперативного запоминающего блока, выход которого соединен с информационным входом преобразователя код-аналог, управляющий вход которого соединен с первым выходом блока управления, а выход — c выходом устройства, введены блок умножения частоты, блок адресации и блок определения периода входного сигнала, вход которого подключен к входу устройства, первый выход соединен с первым входом блока умножения частоты, второй выход — с первым входом блока адресации и первым входом блока управления, 20 второй, третий, четвертый, пятый и шестой выходы которого соединены соответственно с вторым и третьим вхо дами блока адресации, вторым, третьим и четвертым входами блока умножения д5 частоты, первый выход блока .умножения частоты соединен с управляющим входом преобразователя аналог-код и четвертым входом блока адресации, выход которого соединен с управляющим входом оперативного запоминающего блока, второй выход блока умножения частоты соединен с вторым входом блока управления, кроме того, блок умножения частоты выполнен на делителе частоты, элементе И, счет:чике импульсов, управляющем счетчике и дешифраторе, выход которого соединен с первым входом элемента И, выход которого -1ерез последовательно соединенные счетчик импульсов и уп- 4О равляющий счетчик соединен с первым входом дешифратора, второй вход коTopoFo соединен с первым выходом делителя частоты, выход дешифратора и второй выход делителя частоты соединены соответственно с первым и вторым выходами блока умножения частоты, первый, второй, третий и четвертый входы которого соединены соответственно с вторым и третьим входами элемен- gO та И, входом делителя частоты и третьим входом дешифратора, кроме того, блок адресации выполнен на регистре записи, элементе сравнения, элементах ИЛИ и счетчике, выход которого соединен с первыми входами элемента сравнения и регистра записи, выход которого соединен с вторым входом элемента сравнения, выход элемента сравнения соединен с первым входом первого элемента ИЛИ, выход которого 60 соединен с первым входом счетчика, выход которого соединен с выходом блока адресации, первый и второй, третий и четвертый входы блока адресации соединены .соответственно с 65 первым входом второго элемента ИЛИ и объединенными вторыми входами элементов ИЛИ, вторым и третьим входами счетчика.

На чертеже представлена блок-схе,ма предлагаемого устройства.

888165 ются коды ординат входного сигнала в течение второго из рассматриваемых периодов сигнала. Адреса ординат сигнала формируются блоком 6 до момента, когда на третьем входе блока 5 ,блоком 7 снимается разрешающий сигнал по окончании второго периода входного сигнала. После окончания второго рассматриваемого периода входного сигнала прекращается запуск преобразователя 1 и в блоке 2 накоплено ординат входного сигнала, относящихся к одному периоду. Далее следует процесс воспроизведения периодического сжатого сигнала. После окончания второго рассматриваемого периода входного сигнала блок 7, кроме того, подает разрешающий потенциал на управляющий вход блока 3 и с третьего входа на третий вход блока б подает тактовую частоту, с которой формируются адреса считывания в блоке б. Адреса 20 считывания из блока б поступают на вход блока 2. Тактовая частота считывания поступает на второй вход блока 7 с второго выхода блока 5.

Считывание информации в блоке 2 25 происходит без разрушения циклически период за периодом. Считываемые коды ординат сигнала поступают на вход преобразователя 3, на выходе которого формируется периодический сжатый сигнал, с зависящей от количества ординат погрешностью аппроксимации, характеристики которого могут быть измерены.

Такой процесс будет происходить до прихода следующего импульса запус- З

35 ка в блок 7, при котором все изложенные процессы в устройстве повторяются.

В предлагаемом устройстве за счет введения блоков 4, 5 и 6 появилась возможность испольэовать устройство 40 для сжатия входных сигналов для измерительных целей, измерять ряд характеристик периодических сигналов.

Блок 5 работает следующим образом.

На первый и второй входы блока 5 45 приходят разрешающие потенциалы, которые поступают на входы элемента И 8, причем на первый вход блока 5 приходит разрешающий потенциал на время одного периода входного сигнала. На второй вход блока 5 приходит тактовая частота, которая поступает на делитель ll. Bce частоты, формируемые делителем 11, подаются на входы дешифратора 12, а одна из частот с первого выхода блока 5 используется как тактовая при считывании информации из блока 2. Дешифратор 12 построен так, что после сброса всех триггеров устройства на его выходе (на первом выходе блока 5) формиру- dp ется максимально возможная частота, которая подается также на третий вход элемента И 8. После .подачи импульса начала периода входного сигнала на вход элемента И 8 максимальная часто- 65 та поступает через дешифратор 12 на вход счетчика 9, Максимальное число импульсов, которое может подсчитать счетчик 9, равно 2 n.. Как только число в счетчике 9 достигает значения 2п, счетчик 9 передает импульс в счетчик 10,. а в счетчике 9 записывается число и . Счетчик 10 управляет работой дешифратора 12. Получив единицу и изменив свой код, счетчик 10 переключает частоту на выходе дешифратора 12 на более низкую. Такой процесс происходит до окончания импульса длительности периода входного сигнала, подаваемого на первый вход блока 5 — на элемент И 8. Частоты от максимальной до минимально возможной на выходе дешифратора 12 рассчитаны на возможный диапазон длительностей периодов входного сигнала, При этом счетчик 9 регулирует число точек на периоде входного сигнала в пределах от p,до 2 и при соответствующей частоте на выходе дешифратора 12.

Блок б работает следующим образом.

На первом цикле работы устройства на первом выходе блока 5 устанавливается соответствующая частота запуска преобразователя 1, которая гарантирует получение на периоде входного сигнала от и до 2 и ординат. Перед началом последующего периода входного сигнала блок 7 подает на входы элементов

ИЛИ 16 и 17 сигнал, который поступает с них на счетчик 13, как сигнал сброса и, как сигнал записи нулевого кода, в регистр 15. Далее на четвертый вход блока б поступают сигналы запуска преобразователя 1, которые счетчиком 13 подсчитываются. Коды счетчика 13 при его счете образуют коды адреса для блока 2. В соответствии с этими адресами в блоке 2 фиксируются от и до 2 и ординат входного сигнала.

Импульс конца второго периода .входного сигнала поступает на второй вход блока 6 и подается на первый вход элемента ИЛИ 17, а с его выхода — на шину записи регистра 15. На входы регистра 15 в этот момент подается код максимального числа ординат (код последней ординаты, который из счетчика 13 перезаписывается в регистр 15).

После записи этого кода срабатывает элемент 14 и своим выходным сигналом через элемент ИЛИ 16 сбрасывает счетчик 13 в нуль. Блок 7 сигналом с пятого выхода запирает дешифратор 12.

На третий вход блока 6 поступает выбранная тактовая частота сжатия входного сигнала. Снова формируются счетчиком .13 коды адресов ординат сигнала, максимальный код которых записан в регистре 15. При достижении счетчиком 13 кода, записанного в регистре 15, на вход преобразователя 3 последовательно будут поданы все запи" санные в устройство 2 коды ординат

888165 за один период входного сигнала. Из блока 2 коды считываются без разрушения информации. Как только код счетчика .13 станет равным коду регист" ра 15, срабатывает элемент 14 и сбрасывает датчик 13 в нуль. Так как на вход счетчика 13 с третьего входа

5 блока 6 продолжают поступать счетные импульсы, процесс вывода информации из блока 2 продолжается, Такой процесс продолжается циклически, период за пе-, риодом,до следующего запуска устройства, при котором произойдет сброс регистра 15.

Формула изобретения

1. Устройство для временного сжатия входного сигнала, содержащее преобразователь аналог-код, информационный вход которого соединен с вхо gg дом устройства, выход — с информационным входом оперативного запоминающего блока, выход которого соединен с информационным входом преобразователя код-аналог, управляющий вход которого соединен с первым. выходом блока управления, а выход - c выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства, в него введены блок умножения частоты, блок адресации и блок определения периода входного сигнала., вход которого подключен к входу устройства, первый выход соединен с первым входом блока умножения частоты, второй выход " с первым входом блока адресации и первым входом блока управления, второй, третий, четвертый, пятый и шестой выходы которого соединены соответственно с вторым и третьим вхо- 4О дами блока адресации, вторым, третьим и четвертым входами блока умножения частоты, первый выход блока умножения частоты соединен с управляющим входом преобразователя аналог-код и четвертым входом блока адресации; выход которого соединен с управляющим входом оперативного запоминающего блока, второй выход блока умножения частоты соединен с вторым входом блока управления.

2. Устройство по п,1, о т л и ч аю щ е е с я тем, что блок умножения частоты выполнен на делителе частоты, элементе И, счетчике импульсов, управляющем счетчике и дешифраторе, выход которого соединен с первым рходом элемента И, выход которого аерез последовательно соединенные счетчик импульсов и управляющий счетчик соединен с первым входом дешифратора, второй вход которого соединен с первым выходом делителя час.оты, выход дешифратора и второй выход делителя частоты соединены соответственно с первым и вторым выходами блока умножения частоты, первый, второй, третий и четвертый входы которого соединены соответственно с вторым и третьим входами элемента И, входом делителя частоты и третьим входом дешифратора.

3. Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок адресации выполнен на регистре записи, элементе сравнения, элементах ИЛИ и счетчике, выход которого соединен с первыми входами элемента сравнения и регистра записи, выход которого соединен с вторым входом элемента сравнения, выход элемента сравнения соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым входом счетчика, выход которого соединен с выходом Cëoêà адресации, первый и второй, третий и четвертый входы блока адресации соединены соответственно с первым входом второго элемента ИЛИ и обьединенными вторыми входами элементов ИЛИ, вторым и третьим входами счетчика.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

У 617827, кл. Н 03 К 5/159, 1977.

2. Авторское свидетельство СССР

Р 253456, кл. G 06 3 01/62, 1968 (прототип) .

888165

Составитель Д.Шеин

Техред A.Бабинец

Редактор Г.Петрова

Корректор Е.Рошко

Тираж 694 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 10729/15

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4