Запоминающее устройство с защитой информации при отключении питания

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДВТИЛЬСТВУ

Союз Соввтсник

Социалистических

Рвспубпии (и)888205 (61) Дополнительное к ввт.свид-ву (22)Заявлено 070380 (21) 2893406/18-24 с присоединением заявки М (23) ПриоритетОпубликовано 07,1 231. бюллетень М 45 (53}N, Кл.

6 11 С 11/00

3Ьеудерствеяый квинтет

СССР ею делам нзебретеииХ н открытнХ (53) УДК 681.327 (088.8) Дата опубликования описания 07.1281 (72) Авторы изобретения

В,.Г. Псарев, К.P. Бурик, А.И. Кись и В.П. Тищенко (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ЗАЩИТОЙ

ИНФОРМАЦИИ ПРИ ОТКЛЮЧЕНИИ ПИТАНИЯ

Изобретение может быть использовано при разработке полупроводниковой памяти.

Известны запоминающие устройства (ЗУ) с защитой информации при отключении питания (1, 2)

Одно из известных ЗУ содержит блоки памяти с накопителями на основе полупроводниковых запоминающих элементов, в которых параллельно соедйнены соответствующие шины Х и У, то шины выбора корпуса (,кристалла), записи-считывания, входные и выходные информационные шины $1).

Недостатком этого устройства яв1$ ляется то, что при снятии питания информация не сохраняется, Из известных устройств наиболее близким техническим решением к изобретению является ЗУ, содержащее основной, вторичный и батарейный источни ки питания, .основной переключатель энерГопитания, стабилизатор напряжения, память (одноразрядные блоки

2 памяти), электронный переключатель питания, соединенный по входам с выходами первичного источника питания и стабилизатора напряжения, à по выходу - с памятью, в котором вход системы соединен с основным переключателем энергопитания и вторйч-. ным источником питания, выходы вто" ричного и батарейного источников подключены ко входу стабилизатора напряжения, а выход основного переключателя энергопитания соединен су входом основного источника питания 21.

Недостатком этого устройства яв" ляется то, что память в режиме работы и хранения постоянно находится под напряжением, что приводит к уменьшению ее ресурса работы, увели" .чению потребляемой мощности и снижению надежности устройства в целом.

Целью изобретения является повышение надежности устройства..

Поставленная цель достигается тем, что в ЗУ с защитой информации при

888205

5 !

15 отключении питания, содержащее блоки памяти, элементы ИЛИ, первую группу элементов И и источники питания, причем входы элементов ИЛИ подключены к первому источнику питания, первые входы элементов И первой группы соединены со вторым источником питания, выходы элементов ИЛИ подключены соответственно к выходам элементов И первой группы и входам питания блоков памяти,, введены триггеры и вторая группа элементов И. Первые входы элементов И второй группы являются соответственно адресными входами устройства, вторые входы соединены с управляющей шиной, а выходы подключены соответственно к первым входам триггеров, вторые входы которых соединены со входами питания соответствующих блоков памяти. Инверсные выходы триггеров подключены ко вторым входам соответствующих элементов И первой группы.

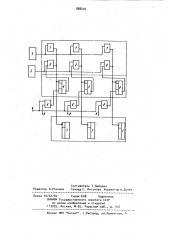

На чертеже изображена структурная схема предложенного устройства.

Устройство содержит блоки памяти 1 (полупроводникового типа, одноразрядные), первый основной источник питания 2, второй источник питания 3 (батарейного типа), триггеры 4, образующие регистр управления питанием блоков памяти, первую и вторую группы элементов И 5 и 6 и элементы ИЛИ 7.

Входы элементов ИЛИ 7 подключены к источнику питания 2. Первые входы элементов И 5 первой группы соединены с источником питания 3. Выходы элементов ИЛИ 7 подключены соответственно к выходам элементов И 5 первой группы и входам питания блоков памяти

Первые входы элементов И 6 второй группы являются соответственно адресными входами 9 устройства, вторые входы соединены с управляющей шиной 8. а выходы подключены соответственно к первым входам триггеров 4. Вторые входы триггеров 4 соединены со входами питания соответствующих блоков па" мяти 1, а инверсные выходы с вторыми входами соответствующих элементов И

Устройство работает следующим образом.

В исходном состоянии питание с источника питания 2 не подается, на управляющей шине 8 сигнал отсутствует, элементы И 5 и 6 и элементы ИЛИ 7 закрыты, питание на триггеры 4 и блоки памяти 1 не подается.

Зо

4

Для работы устройства s режиме приема и выдачи информации с источника питания 2 подается питание, элементы ИЛИ 7 открываются, и питание поступает на блоки памяти 1.

Хранение информации осуществляется в нескольких режимах.

В режиме кратковременного хранения информации перед снятием питания источника, питания 2 в блоки памяти 1 записывается информация, подлежащая хранению, на шину 8 подается сигнал, открывающий элементы И 6.

На адресные входы 9 устройства подается такой код, который устанавливает триггеры 4 в единичное состояние.

При этом элементы И 5 открываются и подключают источник питания 3 к блокам памяти 1, после чего отключается источник питания 2.

В режиме долговременного хранения ограниченной информации перед отключением источника питания 2 в один или несколько блоков памяти 1 производится запись информации, подлежащей хранению. Затем на шину 8 подается сигнал, открывающий элементы И 6, а на входы

9 — такой код нулей и единиц,.который устанавливает соответствующие элементы И 5 и 6 и триггеры 4 в состояние, обеспечивающее подачу питания от источника питания 3 на входы тех блоков памяти 1, в которые записана информация, подлежащая хранению.

После отключения источника питания 2 блоки памяти 1 и соответствующие триггеры 4 обеспечиваются, за исключением тех, на входы которых подано питание от источника питания 3 в соответствии с сигналами на входах 9 устройства.

Информация, подлежащая хранению, может быть любой, в том числе и информацией самого ЗУ, преобразованная из формата и-разрядных слов в

m-разрядное слово, где 1 (m

Причем обьем хранимой информации не должен превышать — 2 слов или

?n a

m2 бит (где а — разрядность адреса ЗУ).

Для равномерного расходования ресурса блоков памяти 2 при длительном.хранении производится периодическая смена дежурных разрядов. Максимальный ресурс будет в том случае, когда информация хранится поочередно в каждом блоке памяти 2 в течение времени Т д = пТ 1, 8882

25 где и — число блоков памяти;

Т - ресурс одного блока памяти.

В режиме длительного хранения ограниченной информации может быть выделено несколько дежурных разрядов, хранящих одинаковую информацию, что дает возможность сохранить ее при отказе отдельных разрядов, При икратном резервировании информация сохраняется даже в том случае, если откажет и-1 блоков памяти 1.

При неисправности отдельных блоков памяти 1, отказ которых заранее определен, например аппаратным, тестовым иЛи другими видами контроля, указанные блоки памяти 1 заранее исключаются из дежурного режима длительного хранения ограниченной информации, что повышает надежность хранения информации оставшихся исправных разрядов..

При этом минимально потребляется мощность в режиме длительного хранения ограниченной информации, так как питание подается только в дежурные одноразрядные блоки памяти 1.

Технико-экономическое преимущество предложенного устройства заключается в его более высокой надежности.

Формула изобретения

Запоминающее устройство с защитой информации при отключении питания, 05 4 содержащее блоки памяти, элементы ИЛИ, первую группу элементов И, источники . питания, причем входы элементов ИЛИ подключены к первому источнику . итания, первые входы элементов И первой группы соединены со вторым источником питания, выходы элементов ИЛИ подключены соответственно к выходам элементов И первой групппы и входам питания блоков памяти, о т л и ч а ю щ е ес я тем, что, с целью повышения на" дежности устройства, оно содержит триггеры и вторую группу элементов И, причем первые входы элементов И вто" рой группы являются соответственно адресными входами устройства, вторые входы соединены с управляющей шиной, а выходы подключены соответственно к первым входам триггеров, вторые входы которых соединены со входами питания соответствующих блоков памяти, инверсные выходы триггеров подключены ко вторым входам соответствующих элементов И первой группы.

Источники информации, принятые во внимание при экспертизе

1. Каган Б.И. Электронные вычислительные машины и системы. M., "Энергия" 1979, с.131-138.

2. Патент CQA NÃ 3980935, кл. G 11 С 11/40, 1976 (прототип).

Составитель Т.Зайцева

Редактор Л.Утехина Техред С. Мигунова Корректор 0.Áèëàê, За каэ 10 732/16 Тираж 648 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, N 35, Раушская наб., д. 4/5 филиал ППП "Патент", r. Ужгород, ул. Проектная, 4