Усилитель считывания для интегрального запоминающего устройства

Иллюстрации

Показать всеРеферат

Союз Соввтсиих

Социалистических рвспубпин

ОП ИСАЙКЕ

ИЗОВРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ оц888206 (6I ) Дополнительное к авт. свид-ву (22) Заявлено 2833380 (21 j 2900443/1 8-24 с присоединением эапвкн И (23) П риоритет

Опубликовано 07.12р1. Ьктллетень М45

Дата опубликования описания 07.1281 (Sl)N. Кл.

G 11 С 11/40

Н 03 К 5/02 (асударетеенны3 квинтет

СССР (53) УДК681. 327 (088, 8) ео делам нзебретеннй н етхрытнй

В.П.Агапкин и Л.Г.Феденко (72) Авторы изобретения (7! ) Заявитель

{ 54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ ДЛЯ ИНТЕГРАЛЬНОГО

ЗАПОИИНАКМЦЕГО УСТРОЙСТВА. Изобретение относится к запоминающим устройствам и может быть использовано при создании БИС ЗУ большой емкости.

Известен усилитель которыи тоит из двух инверторов и двух ключевых транзисторов, причем вход первого инвертора подключен к истокам первого и второго ключевых транзисторов, сток первого ключевого транзистора подключен к выходу первого инвертора, обьединенного с входом второго инвертора, а сток второго ключевого транзистора подключен к выходу второго инвертора, а затворы ключевых транзисторов подключены к шинам управляющих сигналов I.Ij

Недостатками этого усилителя являются низкие чувствительность и быстродействие.

Наиболее близким техническим ре" шением к изобретению является усилитель считывания для запоминающих устройств, содержащий два усилитель2 ных транзистора с общим истоком, соединенных триггерной связью, стоки которых соединены соответственно с первой и второй сигнальными шинами, а общий исток - с первой шиной управ5 ления,.два нагрузочных транзистора, истоки которых соединены с соответствующими сигнальными шинами, а стокис второй шиной управления, два ИОПконденсатора и два ключевых транзистора, сток первого ключевого транзистора соединен с затвором первого нагрузочного транзистора и одной иэ обкладок первого ИОП-конденсатора, исток - с первой сигнальной шиной, затвор - с второй сигнальной шиной, сток второго ключевого транзистора соединен с затвором второго нагрузочного транзистора и одной иэ обкладок второго ИОП-конденсатора, а сток - с второй сигнальной шиной, затвор - с первой сигнальной шиной, другие обкладки ИОП-конденсаторов подключены к третьей шине управления (2).

888206

Недостатками этого усилителя являют ся низ кие чу вст вит ель ност ь и быстродействие вследствие зависимости чувствительности и быстродействия усилителя от порогового напряжения . транзисторов.

Целью изобретения является повышение быстродействия и чувствительности усилителя, Поставленная цель достигается тем, что в усилитель считывания для интегб рального запоминающего устройства, содержащий два усилительных транзистора с общим истоком, соединенных по триггерной схеме, стоки которых подключены соответственно к сигнальной шине и к выходу усилителя, первый и второй нагруэочные транзисторы, истоки которых соединены соответственно с выходом усилителя и с сигнальной шиной, стоки и затвор первого нагрузочного транзистора подключены к шине питания, затвор второго нагрузочного транзистора является одним из входов усилителя, введены ключевые транзисторы, третий и четвертый наг-. рузочные транзисторы, транзистор предварительной зарядки сигнальной шины и транзистор смещения, причем затвор транзистора смещения, стоки третьего и четвертого нагрузочных транзисторов и сток транзистора предварительной зарядки сигнальной шины соединены с шиной питания, затворы третьего и четвертого нагрузочных транзисторов подключены к истоку третьего нагрузочного транзистора и стоку первого ключевого транзистора, затвор которого соединен с затвором и стоком второго ключевого транзистора, с истоком третьего ключевого транзистора и истоком четвертого нагрузочного транзистора, истоки первого и второго ключевых транзисторов и исток транзистора смещения подключены к шине нулевого потенциала, сток транзистора смещения соединен с истоками первого и второго усилительных транзисторов, затвор третьего ключевого транзистора подключен к его стоку, к сигнальной шине и к истоку транзистора предварительной зарядки сигнальной шины, затвор которого является другим входом усилителя.

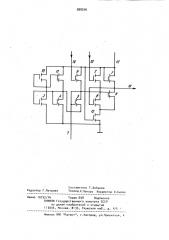

На чертеже представлена. принципиальная схема предлагаемого усилителя.

Усилитель содержит первый и второй 2 нагруэочные транзисторы, перS

1о

15 яо ь зо

35 о

sa

Д вый 3, второй 4 и третий 5 ключевые транзисторы, транзистор предваритель" ной зарядки сигнальной шины 6, сигнальную шину 7, первый 8 и второй 9 усилительные транзисторы, третий 10 и четвертый 11 нагрузочные транзисторы, шину 12 питания и транзистор 13 смещения, входы 14 и 15 и выход 16 усилителя. Транзисторы 8 и 9 имеют общий исток и соединены по триггерной схеме, а их стоки подключены соответственно к шине 7 и к выходу 16 усилителя. Истоки нагрузочных транзисторов 1 и 2 соединены соответственно с выходом 16 усилителя и шиной 7.

Стоки и затвор транзистора 1 подключены к шине 12 ° Затвор транзистора 2 является одним иэ входов усилителя 15.

Затвор транзистора 13, стоки транзисторов 10, 11 и сток транзистора предварительной зарядки шины 6 соединены с шиной 12. Затворы транзисторов 10 и 11 подключены к истоку транзистора 10 и стоку транзистора 3, затвор которого соединен с затвором, и стоком транзистора 4, с истоком транзистора 5 и истоком транзистора 11. Истоки транзисторов 3 и 4 и исток транзистора 13 подключены к шине нулевого потенциала. Сток транзистора 13 соединен с истоками транзисторов 8 и 9. Затвор транзистора 5 подкпючен к его .стоку, шине 7 и истоку транзистора предварительной зарядки шины 6, затвор которого является другим входом 14 усилителя.

Шина 7 подключается к ячейкам памяти запоминающего устройства (на чертеже не показаны).

Усилитель работает следующим образом.

Транзисторы 3, 4 и 5 и транзисторы 10 и t 1 формируют опорное напряжение.

В исходном состоянии шина 7 предварительно заряжается через транзистор предварительной зарядки шины 6 до потенциала +2 В. Напряжение опрокидывания усилителя равно 1, 71,8 В. После уменьшения потенциала на шине 7, которая подключена к ячейкам памяти, находящимся в состоянии логической н!", до 1,7-1,8 В, выход 16 усилителя устанавливается в состоянии логической "1

Если шина 7 усилителя подключена к ячейкам памяти, находящимся в сс с о тоянии логического "0", на выходе

888206

Формула изобретения

5 усилителя 16 будет установлен логический "0".

При поступлении на вход 15 высокого потенциала он через транзистор 2 поступает на шину 7 и-на ячейки памяти (на чертеже не показаны), которые находятся в состоянии логического "0".

На шине 7, подключенной к ячейкам памяти, которые находятся в состоянии логической "1", остается низкий потенциал, поддерживаемый открытыми транзисторами 8 и 13.

Таким образом, работа усилителя не зависит от пороговых напряжений транзисторов и напряжения источника питания, а зависит от разности опорного напряжения и напряжения опрокидывания усилителя.

Технико-экономическое преимущество предлагаемого усилителя заключается в его более высоких, по сравне- нию с прототипом, быстродействии и чувствительности, достигаемых за счет независимости работы усилителя от пороговых напряжений транзисторов.

Усилитель считывания для интегрального запоминающего устройства, содержащий два усилительных транзистора с общим истоком, соединенных по триггерной схеме, стоки которых подключены соответственно к сигнальной шине и к выходу усилителя, первый и второй нагрузочные транзисторы, истоки которых соединены соответственно с выходом усилителя и с сигнальной шиной, а стоки и затвор первого нагруэочного транзистора подключены к шине питания, затвор второго нагру эочного транзистора является одним из входов усилителя, о т л и ч а юшийся тем, что, с целью повышения быстродействия и чувствительности усилителя, введены ключевые транзисторы, третий и четвертый нагруэочные транзисторы, транзистор вредварительной зарядки сигнальной шины и

1ф транзистор смещения, причем затвор транзистора смещения, стоки третьего и четвертого нагрузочных транзисторов и сток транзистора предварительной зарядки сигнальной шины соедине.1у ны с шиной питания, затворы третьего . и четвертого нагрузочных транзисторов подключены к истоку третьего нагрузочного транзистора и стоку первого ключевого транзистора, затвор которо ro соединен с затвором и стоком второго ключевого транзистора, с истоком третьего ключевого транзистора и истоком четвертого нагрузочного транзистора, истоки первого и второго клю чевых транзисторов и исток транзистора смещения подключены к шине нулевого потенциала, сток транзистора смещения соединен с истоками первого и второго усилительных транзисторов, затвор третьего ключевого транзистора подключен к его стоку, сигнальной шине и истоку транзистора предварительной зарядки сигнальной шины, затвор которого является другим входом усилителя.

Источники информации, принятые во внимание при экспертизе

1.IEEE 3оигваI of So11d State, October, 1973, р. 306-307.

2. Авторское свидетельство СССР

llo заявке и 2393457/18-24, кл. С 1 1 С 1 1/40, 1976 (прототип) .

888206

Составитель Т.Зайцева

Редактор Г.Петрова Техред Л.Пекарь Корректор О.Билак

Эаказ 10732/16 Тираж 648 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, 3-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r.Óæãîðoä, ул.Проектная,