Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВМДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (ii>888210 (61) Дополнительное к авт. санд-ву (22) Заявлено 260380 (21) 2900038/18-24 (51)М. Кд.

11 С 27/00 с присоединением заявки М(23) Приоритет1ооударственный комитет

СССР ао делан нза4ретвннй н открытнй

Опубликовано 07.1281. бюллетень М45

Дата опубликования описания 07 . 1 2 . 81 (53) УДК681. 327..66(088.8) (72) Авторы изобретения

A.È.Áðàæíèêoâ, В.В.Задорожный и Е.A.Хомутов

I (71) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к электро- измерительной технике и предназначено для запоминания аналогового напряжения °

Известно аналоговое запоминающее устройство (13, включающее в себя операционный усилитель и запоминающий конденсатор в цепи его отрицательной обратной связи.

Однако известное устройство не обеспечивает одновременно высокого быстродействия и длительного времени хранения с высокой точностью.

Наиболее близким решением по технической сущно ти к изобретению является аналоговое запоминающее устройство (АЗУ), которое содержит операционный усилитель, конденсатор, включенный в цепь обратной связи, а между неинвертирующим входом усилителя и шиной нулевого потенциала включены параллельно соединенные дополнительный конденсатор и размыкающий контакт, что приводит к повы".шению точности запоминания - уменьше-. нию напряжения утечки запомненного напряжения за счет частичной компенсации входного тока по инвертирующему входу усилителя (21.

Однако при запоминании аналоговых сигналов в длительном временном диапазоне напряжение утечки вследствие неполной компенсации входных токов усилителя, может принимать неприем1о лемо большие значения.

Целью изобретения является повыше" ние точности устройства..

Поставленная цель достигается тем, что в аналоговое запоминающее устрой15 ство, содержащее основной интегратор, первый вход которого является входом устройства, а выход - выходом устройства, дополнительный интегратор, перЗо вый и второй накопительные элементы, например, первый и второй конденсаторы, одни из обкладок которых соединены соответственно с вторым входом основного интегратора и с первым вхо!

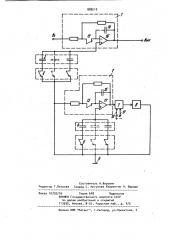

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит основной 1 и дополнительный 2 интеграторы, накопительные элементы, например конденсаторы 3 и 4, контакты реле 5 и 6, блок 7 сравнения, обмотку реле 8, шину нулевого потенциала 9, шины 10 и ll опорного напряжения, ключи 12 и 13, конденсаторы 14 и 15, усилители 16 и 17.

Устройство работает следующим образом.

Входной сигнал поступает на первый вход основного интегратора 1, При переводе устройства в режим памяти одновременно с размыканием ключа 12 в интеграторе 1 размыкается также ключ 13, в интеграторе 2 и на его выходе появляется напряжение утечки конденсатора t5, которое поступает на первый вход блока 7, выход кото- рого управляет работой реле 8 и в зависимости от соотношения величины и полярности выходного напряжения интегратора 2 с одной стороны, и опорных напряжений на шинах l0 и 11 с другой стороны, срабатывает определенное количе во контактов 5 и 6 реле, которые и подключены как к первому входу интегратора 2, так к вто рому входу интегратора 1 контакты 5 .и 6, за счет чего разностной входной ток усилителя 16 и 17 принимает нуле-, вое значение, причем соответствующий выбор опорных напряжений позволяет согласовать величины крутизны раз- 55

3 88821 дом дополнительного интегратора, репе, шину нулевого потенциала и шины опорного напряжения, введен блок сравнения, первый вход которого соед. нен с выходом дополнительного интегратора, второй вход которого подключен к шине нулевого потенциала, выход блока сравнения соединен с первым выводом обмотки реле, второй вывод которой подключен к шине нулевого потенциала, другие обкладки первого и второго конденсаторов соединены соответственно через первый и второй размыкающие контакты с вторым входом дополнительного интегратора, второй и третий входы блока сравнения соедине(ны с шинами опорного напряжения.

0 4 ностных входных токов усилителей 16 и 17 интегр.-торов 1 и 2 °

Таким образом, в предлагаемом устройстве напряжение утечки U>z конденсатора 14 по входной цепи усилителя,16 практически сводится к нулю: ! \

8 < Рy так как 5X "SWg > где i, tax - входные токи по перСД%1 вому и второму входам усилителя t6, с - емкость конденсатора 14, t - время хранения запомненного напряжения.

Формула изобретения

Аналоговое запоминающее устройство, содержащее основной интегратор, первый вход которого является входом устройства, а выход - выходом устройства, дополнительный интегратор, первый и второй накопительные элементы, например первый и второй конденсато" ры, одни из обкладок которых соединены соответственно с вторым входом основного интегратора и с первым входом дополнительного интегратора, реле, шину нулевого потенциала и шины опорного напряжения, о т л и ч а ющ е е с я тем, что, с целью повышения точности устройства, в него введен блок сравнения, первый вход которого соединен с выходом дополнительного интегратора, второй вход которого подключен к шине нулевого потенциала, выход. блока сравнения соединен с первым выводом обмотки реле, второй вывод которой подключен к шине нулевого потенциала, другие обкладки первого и второго конденсаторов соединены соответственно через первый и второй размыкающие KoHTBKTbl с вторым входом дополнительного ин-. тегратора, второй и третий входы блока сравнения соединены с шинами опорного напряжения.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N 193174, кл. G 11C 27/00, 1967.

2. Авторское свидетельство СССР

Ю 587508, кл. G 11 С 27/00, 1976 (прототип) .

Составитель А.Воронин

Редактор Г.Петрова Техред С. Мигунова Корректор М. Шароши

Заказ 10732/16 Тираж 648 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал flAF! "Патент", r.Ужгород, ул.Проектная, 4