Цифровой фильтр

Иллюстрации

Показать всеРеферат

Союз Советски к

Социапистическик

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< >888335 (61) plîâîëíèòåëüíîå к авт. свид-ву(22) З 25.03.80 (21) 2g023gp/18-24 с присоединением заявки Ле— (23) Приоритет

Опубликовано 0 712.о1. Бюллетень № 45

Дата опубликования описания 071281 (5! )М. Кл.

Н 03 Н 17/06

Гаеударстекииый комитет

СССР ио делам изобретеиий и открытий (53) УДК681. 3 (088. 8) (72) Автор изобретения

А.А. Охотин (71) Заявитель (S4) ЦИФРОВОЙ ФИЛЬТР

Изобретение относится к вычислительной технике и может быть использовано в и з мер и тел ь ной аппаратуре для выделения импульсов, длительность которых задается цифровым кодом.

Известен цифровой фильтр С13, содержащий одновибратор и элементы И-НЕ.

Недостатком устройства являются огра-ниченные функциональные возможности вследст вие от сутст вия регулирования

10 полос пропускания.

Из известных устройств наиболее близким по технической сущности к изоб-. ретению является цифровой фильтр $2), содержащий генератор импульсов, делители с переменным коэффициетитом деления, дифференцирующую цепь, элементы

И и одновибратор.

Недостатком известного устройства являются ограниченные функциональные возможности. Кроме того, параметры импульсов на выходе цифрового фильтра определяют ся н< соот вет ст вующими характеристиками входных импульсов, а способом технической реализации дифференцирующей цепи.

Целью изобретения является расширение функциональных возможностей устройства зэ счет регулирования полосы пропу скан ия фил ьт р а.

Эта цель достигается тем, что в цифровой фильтр, содержащий генератор импульсов, дифференцирующую цепь, делитель частоты, элемент И, выход которого соединен со счетным входом делителя частоты, первый установочный вход которого является установочным входом фильтра, прямой выход делителя частоты соединен с первым входом элемента И, второй вход которого подключен к выходу генератора импульсов, вход дифференцирующей цепи является информационным входом фильтра, введены дешифратор, регистр сдвига, триггер, первый и второй элементы НЕ, элемент 2И-ИЛИ, выход которого соединен с первым установочным входом регистра сдвига, вход синхронизации ко888335 торого соединен с выходом генератора импульсов. Второй установо чный вход регистра сдвига соединен с выходом дешифратор а, вход которого я вляется установочным входом фильтра. Выход старшего разряда регистра сдвига является выходом фильтра. Информационный вход фильтра подключен к информационному входу младше го разряда регистра сдвига и ко входу первого элемента НЕ, выход которого соединен с входом синхронизации триггера и со вторым установочным входом делителя частоты, инверсный и прямой выходы которого соединены соответственно с первым входом элемента 2И-ИЛИ и с ичформационным входом три ггера, установочный вход которого подключен к выходу дифференцирующей цепи, а выход триггера соединен со вторым входом элемента 2И-ИЛИ, третий вход .которого соединен с выходом второго элемента

НЕ. Вход второго элемента НЕ и четвертый вход элемента 2И-ИЛИ являются входом выбора режима фильтра.

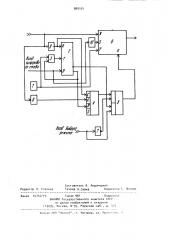

На чертеже изображена структурная схема цифрового фильтра.

Цифровой фильтр содержит генератор импульсов 1, делитель с переменным коэффициентом деления 2, элемент И 3, триггер 4, элемент 2И-ИЛИ 5, регистр сдвига 6, элементы HE 7 и 9, дифференцирующую цепь 8 и дешифратор 10.

Цифровой Фил ьтр работает следующим образом.

При работе в режиме фильтра нижних частот на вход инвертора 7 подается логический нуль. На установочный вход делителя 2 подан цифровой код, соответствующий частоте среза фильтра нижних частот при определенной частоте квантования генератора i На вычитающий вход делителя 2 через элемент И 3

Ь подается тактовая последовательность с генератора 1. Исследуемый импульс, пришедший на вход цифрового фильтра, через инвертор 9 разрешает работу делителя 2. Одновременно тактовая последовательность, приходящая на счетный вход сд ви ro ao го р е ги ст р а, пере пи сы вает содержимое информационного входа, куда приходит исследуемый импульс.

Из переднего фронта входного импульса дифференцирующая цепь 8 формирует короткий импульс, устанавливая на прямом выходе триггера 4 низкий уровень. Делитель 2 считает импульсы генератора, поступающие через элемент

И 3 до тех пор, пока их число не станет равным числу, записанному в виде числового кода на установочных входах делителя 2. После этого на прямом выходе последнего установится логик ческий "О", запрещающий прохождения импульсов с генератора 1 через элемент И 3. Процесс происходит таким образом, если длительность входного импульса

i0

/ (1)

"и i "0 где ь0 — период следования импульсов с генератора 1, К вЂ” число импульсов, соответствующее коэффициенту деления делит еля 2, Задний фронт информационного импульса, поступая на С-вход триггера

4 переписывает на прямой выход ин J формацию с D- входа, в данном случае

20 подтверждая нулевой потенциал на прямом выходе триггера 4 и, соответственно нулевой потенциал íà R-входах первых К триггеров регистра 6, т.е. информация, записанная в первых К три ггерах регистра б,сохраняется и поступает на выход цифрового фильтра через время, равное =, М, il) эо где 1 — время задержки входного импульса; число разрядов сдви гового ре ги стра.

Если же длительность входного импул ьса и оК то к моменту окончания исследуемого

40 импульса на прямом выходе делителя

2 останется высокий уровень, задний фронт информационного импульса опрокинет триггер 4 и установит на R входах первых К триггеров сдвигового регистра высокий потенциал, что при45 ведет к записи нулеи в первых К триггерах регистра 6, т. е. импульс, длительность которого не отвечает условию (1), на выход цифрового фильтра не поступает.

При работе цифрового фильтра в режиме фильтра верхних частот (что соответствует подаче на вход инвертора 7 логической 1) с приходом на вход цифрового фильтра исследуемого импульса на вход делителя 2 также начинают поступать тактовые импульсы с генератора 1 через элемент И 3. Однако в данном случае, если длительность

888335 исследуемого импульса удовлетворяет условию (1), то, по окончании интервала времени 1, равного

1=7 к

0 на инверсном входе делителя 2 установится высокий потенциал и с .выхода элемента И-ИЛИ 5 на к -входах первых

K триггеров регистра сдвига также установится высокий потенциал, что приводит к стиранию ранее записанной информации, т.е. импульс такой длительности на выход цифрового фильтра не поступает.

Если же длительность исследуемого импульса удовлетворяет условию (3), то за время, равное длительности импульса т., обнуление делителя 2 не произойдет, т.е. не произойдет стирания ранее записанной информации в регистре 6. В результате через интер- )î вал времени Т (2) информация об исследуемом импульсе появится на выходе цифрового фильтра.

Изменения частотного диапазона цифрового фильтра можно достичь либо изменением цифрового кода на входе делителя 2, либо сменой частоты генератора (возможно одновременное изменение). При смене цифрового кода на входе делителя 2 меняется и количество зо триггеров в регистре 6, содержимое которых можно стереть установкой "1" по R -входу регистра 6.

Цифровой фильтр может быть использован как фильтр нижних частот или как фильтр верхних частот. При этом сохраняется соответствие параметров импульсов на выходе фильтра соответствующим параметром входных импульсов.

Формула изобретения

Цифровой фильтр, содержащий генератор импульсов, дифференцирующую цепь, делитель частоты, элемент И, вьlxop ко- торого соединен со счетным входом делителя частоты, первый установочный вход которого явля;е т я уэст-ановочным входом фильт.р:а:,, при вввм прямей .выход делителя частоты соединен с первым входом элемента И.-,,второй вход каторого подключен к выходу генератора импульсов, вход дифферрнцируацей цепи является информацвояним вхедом фильтра, о т л и ч а. ю шийся тем, что, с целью расширения его функциональных возможностей зе- виет регулирования полосы пропускания, в него введены дешифратор, регистр сдвига, триггер, первый и второй элементы НЕ, элемент 2И-ИЛИ, выход которого соединен с первым установочным входом регистра сдвига, вход синхронизации которого соединен с Qblx@QQH генератора импульсов, при этом второй установочный вход регистра сдвига соединен с выходом дешифраторе„ .@авд которого является устанавочным вкадем фил ьтра; выход старшинств урщря@афррущстра сдви га -йяляатащмфыфдры::.фафа ра., и нформационньГй вн у фЩЬфа нсщкцижен к инфор.маци.онномуЖцф фф Мфйдщего разЮ Ж ного элемента NE- ., вв1фэф.Кетового соединен с входом синхдФнизеции триггера и со вторым усгановочным входом делителя частоты, инверсный и прямой выходы которого соединены соответственно с первым входом элемента 2ИИЛИИ с информационным входом триггера, установочный вход которого подключен к выходу дифференцирующей цепи, а выход триггера соединен со вторым входом элемента 2И-ИЛИ, третий вход которого соединен с .выходом другого элемента НЕ, вход которого и четвертый вход элемента 2И-ИЛИ являются входом выбора режима фильтра.

Источники информации принятые во внимание при экспертизе

1. "Электроника", Г 13, 1971, с. 58.

2. Авторское свидетельство СССР

N 691871, кл. G 06 F 1 5/36, !979 (прототип).

888335

Составитель 8. Аедоницкий

Техред А.Савка Корректор C. Некмар

Редактор Л. Утехина

Заказ 10742/19

Тираж 991 Подпи сноп

ВНИ ИПИ Государ ст венного комитета СССР по делам изобретений и открытий

113035, Иосква, К-35, Раушская наб., д. 4/

Филиал ППП Патент", г. Ужгород, ул. Про -t> «л,