Цифровая динамическая следящая система

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистическими

Республик (61) Дополнительное к авт. сеид-ву

{22) Заявлено 060380 (2f ) 2902174/18-24 с присоединением заявки Й9— (23) Приоритет—

Опубликовано 151281 Бюллетень Ио46

G 05 В 11/04

Государственный комитет

СССР но делам изобретений и открытий (5З) Ж 62: 50 (088. 8) Дата опубликования описания 15.1281 (71) Заявитель (54) ЦИФРОВАЯ ДИНАМИЧЕСКАЯ СЛЕДЯЩАЯ СИСТЕМА

Изобретение относится к радиотехнике, а именно к следящим системам управления и фильтрации, в частности к следящим фильтрам для выделения сигналов на фоне помех.

Известны цифровые следящие системы с промежуточным преобразованием кода в напряжение для перестройки управляемого генератора (1) и (2).

Недостатком таких устройств является высокий уровень собственных шумов управляемого генератора, не позволяющий обеспечить минимально возможную ошибку оценки частоты выделяемого сигнала. 15

Наиболее близкой к предлагаемой по технической сущности и достигаемому результату является цифровая динамическая следящая система с непосредственным цифровым преобразованием 20 кода в частоту, содержащая последовательно соединенные первый смеситель, усилитель промежуточной частоты, цифровой дискриминатор и цифровой фильтр-экстраполятор, а также и после 25 довательно соединенные блок опорных частот, делитель с переменным коэффициентом деления, второй смеситель, соответствующий вход которого соединен со вторым выходом блока опорных 30 частот, и полосовой фильтр., вых- д которого соединен со входом первого смесителя (3).

Недостатком подобной цифровой следящей системы является неудовлетворительная точность работы при увеличении диапазона перестройки частоты преобразователя код-частота, так как при этом возрастает ошибка дискретности, уменьшение которой за счет увеличения коэффициента деления управляс.мого делителя уменьшает диапазон перестройки частоты преобразователя код-частота. Кроме того, нелинейность перестройки преобразователя, обусловлена переменным шагом установки частоты в преобразователе.

Цель изобретения — повышение точности слежения во всем диапазоне изменения частоты входного сигнала.

Цель достигается тем, что в устройство введены последовательно соединенные интерполятор и блок сравнения, певый выход которого подключен к управляющему входу делителя с переменным коэффициентом деления, а соответствующий вход подключен к первому выходу цифрового фильтра-экстраполятора, второй выход которого соединен с первым выходом интерполя890358 тора, второй вход которого соединен с соответствующим выходом блока опорных частот.

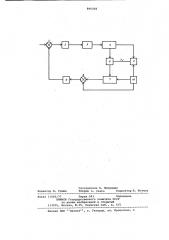

На чертеже приведена блок-схема устройства.

Цифровая динамическая следящая сиссистема содержит первый смеситель 1, на выходе которого установлен усилитель промежуточной частоты 2, выход которого подключен ко второму входу смесителя 1 через последовательно соединенные цифровой дискрименатор 3, цифровой фильтр-экстраполятор 4, интерполятор 5, блок сравнения 6, второй вход которого соединен со знаковым выходом пифрового фильтра-экстраполятора 4, делитель с переменным 15 коэффициентом деления 7, второй смеситель 8 и полосовой фильтр 9. Вторые входы интерполятора 5, делителя с переменным коэффициентом деления 7 и второго смесителя 8 соответственно соединены с выходами блока опорных частот 10. Выход знака цифрового фильтра-экстраполятора 4 соединен со входом блока сравнения 6.

Цифровая динамическая следящая система работает следующим образом.

Входной сигнал поступает на первый вход первого смесителя 1, на второй вход которого через последовательно соединенные делитель с переменным коэффициентом 7, второй сме- 30 ситель 8 и полосовой фильтр 9поступает выходной сигнал блока опорных частот 10 второй выхоц которого подключен ко второму входу второго смесителя 8, в результате чего на выхо- 35 де усилителя промежуточной частоты, поступающий на вход цифрового частотного (фазового) дискрименатора 3, где в цифровой форме выделяется величина рассогласования по частоте 40 (фазе) .

После обработки этого сигнала в цифровом фильтре-экстраполяторе 4 результирующее двоичное число выдается в интерполятор 5, на второй вход которого из блока опорных частот 10 поступает сигнал с частотой, преобразующий это число в частоту следованйя импульсов.

Эти импульсы поступают в блок сравнения 6, куда одновременно с выхо-5О да цифрового фильтра-экстраполятора 4 поступает информация. В блоке сравнения 6 формируется управляющее воздействие, которое устанавливает соответствующий коэффициент деления де- Я лителя с переменным коэффициентом деления 7.

Интерполятор 5 представляет собой преобразователь двоичного кода в число-импульсный, где каждому двоичному символу поставлены в соответствие распределенные по временной оси импульсы.

Формула изобретения

Цифровая динамическая следящая система, содержащая последовательно соединенные первый смеситель, усилитель промежуточной частоты, цифровой дискриминатор и цифровой фильтр-экстраполятор, а также последовательно соединенные блок опорных частот, делитель с переменным коэффициентом деления, второй смеситель, соответствующий вход которого соединен с соответствующим выходом блока опорных частот, и полосовой фильтр, выход которого соединен со входом первого смесителя, отличающаяся тем, что, с целью повышения точности системы, она содержит последовательно соединенные интерполятор и блок сравнения, первый выход которого подключен к управляющему входу делителя с переменным коэффициентом деления, а соответствующий вход подключен к первому выходу цифрового фильтра-экстраполятора, второй выход которого соединен с первым входом интерполятора, второй вход которого соединен с соответствующим выходом блока опорных частот.

Источники информации, принятые во внимание при экспертизе

CBHgJBTeJIbCTBO СССР

05 В 13/02, 1970, свидетельство СССР

03 В 3/04, 1975. свидетельство СССР

05 В 11/14, 1970

1 ° Авторское

Р 3284 30, кл. G

2. Авторское

Р 5374.32, кл. Н

3 ° Авторское

9 348979, кл. G (прототип).

Благодаря такому преобразованию на выходе делителя с переменным коэффициентом деления 7 удалось получить изменение частоты (фазы) по линейному закону. Установка соответствующих коэффициентов деления позволит изменять модуляцию выходной частоты блока 7 по фазе равномерно по. всей временной оси.

Выходной сигнал делится делителем с переменным коэффициентом деления 7, и, сформированный тем самым в симметрированный меандр, поступает на второй смеситель 8, на выходе которого с помощью второго выходного сигнала блока опорных частот 10 формируется суммарный сигнал, который через .полосовой фильтр 9 выдается на второй вход первого смесителя 1.

При одинаковых полосах перестройки предлагаемая система позволяет уменьшить шаг (ошибку) дискретности установки частоты в 7 раз и увеличить число дискретных установок частоты в

5 раз.

890358

Составитель Э. Митрошин

Техред A. Савка Корректор В. Бутяга

Редактор Н. Ромжа

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Заказ 11005/77 Тираж.943 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5