Дешифратор

Иллюстрации

Показать всеРеферат

Союз Советски к

Социапистическик

Республик

ОП ИСАНИЕ

ИЗЬБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< )890386

Ф

J // - (61) Дополнительное к авт. свнд-еу(22) Заявлено 040 1.80 (21) 2864135/18-24 с присоелиненнем заявкн М(23) ПриоритетОпубликовано 15.1281. Бюллетень М46

Дата опубликования овнсання 1 1281 (И)М. Кл.

G 06 F 5/00

)667Ааротееииый комитет

СССР ао делам изабретеиий и открытий (53) УЛК 681. 325 (088. 8) (72) Авторы изобретения

В. И. Мяснов и В. Б. Смирнов (71) Заявитель д (54) ДЕШИФРАТОР

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении дешифраторов в преобразователях интервала времени в цифровой код.

Известен дешифратор, состоящий из логических элементов (1) .

Недостаток известного устройства состоит в сложности е го реализации при дешифрации результата m-тактного преобразователя интервала времени в цифровой код.

Наиболее близким к предлагаемому по технической сущности и схемному

15 построению является дешифратор, содержащий (q-1) элементов И, где q =

1og>mfa, Недостаток данного дешифратора также заключается в его сложности, связанной с реализацией сложных логических уравнений при дешифрировании результата преобразования интервала времени в цифровой код.

Целью изобретения является упрощени е у с1 ройст ва.

Поставленная цел ь обе спечи вает ся тем, что дешифратор, содержащий (q-1) элементов И, где q = 1ос1 и), дополнительно содержит q суммирующих блоков, причем i-ий суммирующий блок (i=i-q) содержит 5;п/2п - i +1 сумматоров, объединенных в К ярусов, где К равно числу итераций выполнения операции

281-1 ((до полуцение единицы), входы первого яруса сумматоров 1-ого суммирующе го блока соединены сост вет ст венно с выходами переноса сумматоров (i+1)-ого суммирующего блока и с выходом ) -ого элемента И, выходы суммы сумматоров J ol-o яруса соединены со вход а ми су мматоро в ()+1 ) - о го я ру с.з, входы сумматоров первого яруса 0-ого суммирующего блока соединены с входа" ми задания времени дешифратора, а последний ярус в q-oro суммирующего

86

3 8903

5лока выполнен на полусумматора, выходы суммы сумматоров К-ых всех суммиJ рующих блоков являются выходами дешифратора, первые входы всех элементов

И соединены с управляющим входом дешифратора, а вторые входы элементов

И соседнего каскада являются информационными входами дешифратора.

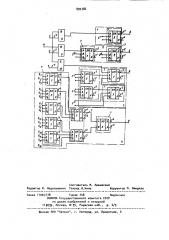

На чертеже представлена функциональная схема предлагаемого дешифра- >0 тора для m-тактного преобразователя интервала времени в цифровой код при

m - =16.

Этот дешифратор имеет q = 1og 16 = 4 выходов. Количество выходов определяет и количество групп, которых также равно m = 4. Предлагаемый дешифратор содержит суммирующие блоки 1-4, состоящие из сумматоров 5. Суммирующий блок 4 содержит также полусумматор 6.

Сумматоры 5 и полусумматор 6 объеди- . нены в ярусы 7, К шестнадцами входам суммирующего блока 4 подключены соответственно выходы Qz, Qz, ..., Q® разрядных триггеров m-тактного счетчи- д ка преобразователи и элеиенты И 8-10.

На выходе суммы выходного сумматора каждого суммирующего блока (кроме последнего) и полусумматора 6 суммирующего блока 4 формируются логические функции выходного двоичного кода:

Ь вЂ” с весом 2 . T с - с весом

2 . Т,, d- ceecoM2 . Т„е-с весом 2" . То. На входах и выходах сумматоров и полусумматора проставлены весовые коэффициенты. На один из входов сумматора каждого, кроме последнего, суммирующего блока через соответствующие элементы И 8-10 подключены соответственно выходы группы соседнего младшего разряда выходного кода. Вторые входы элементов И 8-10 объединены между собой и соединены с выходом A счетчика преобразователя с весом 2 . Т, (где А - логическая функция на выходе счетчика преобразователя, определяющая разрядное число с весом 2 . Tq ). На входы сумматора суммирующего блока 1 поступают импульсы с весом 2 . То с выходов переноса сост вет ст вующих сумматоров вто- рого суммирующего блока второй группы. На входы сумматоров второго суммирующего блока 2 поступают импульсы с весом 2 . То с выхода переноса каждого сумматора суммирующего блока 3. N

На входы сумматоров суммирующего блока 3 поступают импульсы с весом

2 . То с соответствующих выходов переноса сумматоров и полусумматора 6 суммирующего блока 4. Выходы суммы сумматоров каждого суммирующего блока соединены соответственно со входами сумматоров своей группы. Если к сумматору для m-тактного преобразователя интервала времени в цифровой код при m = 16 добавить 16 сумматоров, образовав теи самым пятый суммирующий блок, который формирует на выходе разрядное число с весом 2 .Т„, а на выходе суммирующего блока 4 вместо полусумиатора 6 поставить сумматор, один вход которого соединить через элемент И с выходом пятой группы и с выходом А счетчика преобразователя, то получим дешифратор для тридцатидвухтактного преобразователя интервала времени в цифровой код. При этом шестнадцать входов представленного на чертеже дешифратора необходимо соединить с выходом переноса всех сумматоров пятого суммирующего блока.

Ко входам сумматоров пятого суммирующего блока группы подключаются ( соот ветст вующие выходы т ридцат идвухтактного счетчика преобразователя.

Изъяв из представленной на чертеже схемы четвертый суммирующий блок, получим дешифратор для восьмитактного преобразователя, при этом восемь входов сумматоров третьего суммирующего блока подключаются соответственно к выходаи восьмитактного счетчика преобразователя. Аналогично первый и второй суммирующие блоки образуют дешифратор для четырехтактноro преобразователя интервала времени в цифровой код.

Дешифратор работает следующим образом. а-TBKTHblH счетчик m òàêòíîãî преобразователя интервала времени в цифровой код при любом m всегда имеет четчетное количество состояний, причем половина этих состояний приходится на время, когда А = О, и половина— когда A = 1. Вес единицы младшего разряда m-тактного счетчика равен — а если выбрано кратно степени

Т двух (4, 8, !6, 32 и т,д. ), то

= 2 . То . При А = 0 количество единиц. Д, зафиксированное e m-тактном счетчике, равно количеству логических единиц, записанных в разрядных триггерах m òàêòíîão счетчика (или количеству триггеров m-тактного счетчика, стоящих в состоянии логической едини89038б Ь годаря введению логических элементов !

И 8-10 удалось создать простую схему коммутации устройства с процесса простого суммирования единиц на проу цесс суммирования с одновременным

I преобразованием в дополнительном коде

/ результата в прямой код.

Формула изобретения

5 цы) . Поэтому простое суммирование единиц с выходов разрядных триггеров

m-т актного счет чи ка с помощью сумматоровв определит чи сло, зафи ксиро ванное в данный момент в m-тактном счет чике при Л = О. В случае, когда А = получить искомое число можно также суммированием, но при этом состояние логической единицы разрядных триггеров m-тактного счетчика необходимо принимать равной Ь, а состояние логического нуля 2Ь. Такое построение дешифратора потребует вдвое большее количество сумматоров по сравнению с предлагаемой схемой. Если при

А = 1 суммировать только логические единицы, то на выходе дешифратора, построенного на сумматорах, результат выражается в дополнительном коде. В этом. случае при А = 1 на выходе дешифратора, построенного на сумматорах, необходимо включать в работу преобразователь дополнительного двоичного кода в прямой. Это также значительно усложнит дешифратор.

В предлагаемом дешифраторе в сум" маторах производится сложение единиц, но при А = 1 в работу включаются элементы И 8- 10, с помощью которых выход соседнего младшего разряда соединяется со входом сумматоров старшего разряда, за счет чего значение младшего разряда при А = 1 суммируется со значением старшего разряда, в результате происходит автоматическое преобразование дополнительного двоичного кода (получающегося от суммирования единиц m-тактного счетчика при A = 1) в прямой двоичный код. Когда А = 0„ элементы И 8-10 выключены и не оказывают влияния на оаботу дешифратора.

Применение в дешифраторе сумматоров упрощает дешифратор по сравнению с построением его на логических элементах И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и т. и.) и позволяет производить как операцию сложения, так и операцию преобразования дополнительного кода в прямой на одних и тех же элементах. БлаДешифратор, содержащий (q-1) элементов И, где q = logjam, о т л ич а ю шийся тем, что, с целью !

В упрощения устройства оно содержит q суммирующих блоков, причем >-ый сум,> ирующий блок (i=1 ц) содержит

S " 2 .„ сумматоров, объединенных в

К ярусов (где К равно. числу итераций

2р 1 2$1-1 еипопиеиии операции 1 ((до попу3 чения единицы), входы сумматоров первого яруса i-го суммирующего блока соединены соответственно с выходами

И переноса сумматоров (i+1)-ого суммирующего блока и с выходом I ого элемента И, выходы суммы сумматоров j-го яруса соединены со входами сумматоров

Ц +1)-ого (j=1-К) яруса, входы суммазр торов первого яруса q-го суммирующего блока соединены с входами задания времени дешифратора, а последний ярус q-го суммирующего блока выполнен на полусумматора, выходы суммы сумматоров К-ых всех суммируюЩих блоков являются выходами дешифраторов, пер: вые входы элементов И соединены с управляющим входом дешифратора, а вторые входы элементов И соседнего каскада являются информационными входами дешифратора.

Источники информации, принятые во внимание при экспертизе

1. Алексеенко А.Г. Основы микросхемотехники. M., "Советское радио", 1977, с. 52-88.

2. Трачик В. Дискретные устройства автоматики. М., "Энергия", 1978, с. 92-120 (прототип) .

890386

Составитель M. Аршавский

Редактор М. Недолуженко Техред,И.Нинц Корректор Н. Ивыдкая

Заказ 1 100 7/78 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Ф Ф филиал ППП "Патент", r. Ужгород, ул. Проектная, 4