Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскии

Социалистичеснни

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДИТИЗЬСТВУ

> >892475 (61) Дополнительное к авт. саид-еу (22) Заявлено 08.05.80 (21) 2921479! 18-24 (5.! )Ì. Кл.

G ll С II/00 с присоелииение>и за»вки М

fecyasI>asassb>ll комитет

СССР ао делам изобретений и »ткрытий. (23) Приоритет (53) УДК 681. 327 (088. 8) Опубликовано 23.12.81. Бюллетень р>т 47

Дата опубликования описан»» 23 . 12,81 (72) Авторы изобретения

Г.N.Êàáàåíêîâà, Н.И.Коренев, И.А ховицкийи P.Ï.Éèäëoâñêèé

1

> (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запомина- ющим устройствам и может быть использовано для построения быстродействующих запоминающих устройств больmoro объема.

Известно запоминающее устройство, содержащее накопитель с основными и дополнительными разрядными шинами, адресный регистр, формирователь токов опроса, основные и дополнительные усилители-формирователи, линии задержки и регистр числа, причем для временной селекции используются сигналы, формируемые при помощи дополнительных разрядных шин (1).

Недостатком этого устройства является низкое быстродействие, Наиболее близким к предлагаемому по технической сущности является запоминающее устройство, содержащее накопитель с адресными шинами, основными и дополнительными разрядными шинами, адресный регистр, основные усилители-формирователи .У

Я входы которых подключены к выходам основных разрядных шин, дополнительные усилители-формирователи, входы которых подключены к выходам дополнительных разрядных шин, формирователь токов опроса, элемент задержки, схемы И и регистр числа f2).

Однако устройство имеет низкое быстродействие вследствие большого времени пробега информации от накопителя до регистра числа и нестабильности временного расположения сигналов из-за применения элементов

И временной селекции.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем,что в запоминающее устройство, содержащее регистр адреса, регистр числа, формирователь тока опроса, накопитель, основные и допо»>тительные усилители считывания, причем выходы регистра адреса подключены ко входам формирователя тока опроса, 89247 йЬ=.Ь1+ Я.

2 выходы .которого соединены с адресными шинами накопителя, входы основных усилителей считывания подключены к основным разрядным шинам накопителя, а выходы - к информационным входам регистра числа, входы дополнительных усилителей считывания соединены с дополнительными разрядными шинами накопителя, введены регулируемые элементы задержки, входы 1О которых подключены к выходам дополнительных усилителей считывания, а выходы — к стробирующим входам регистра числа.

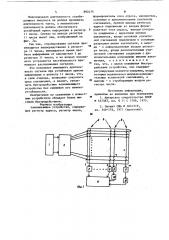

На фиг. 1 изображена структурная схема предлагаемого устройства, на фиг. 2 — временные диаграммы, поясняющие его работу.

Устройство содержит 1 фиг. 17 регистр 1 адреса, формирователь 2 тока

20 опроса, накопитель 3 с адресными шинами 4, основными разрядными шинами

5 и дополнительными разрядными шинами 6, запоминающие элементы 7, основные усилители 8 считывания, дополнительные усилители 9 считывания, регулируемые элементы 1О задержки и регистр 11 числа.

Выходы регистра 1 адреса подключены ко входам формирователя 2 тока

30 опроса, выходы которого соединены с адресными шинами. 4 накопителя А

Входы осндвных усилителей 8 считывания подключены к основным разрядным шинам 5 накопителя 3, а выходы— к информационным входам регистра 11 Зз числа. Входы дополнительных усилителей 9 считывания соединены с дополнительными разрядными шинами 6 накопителя 3. Входы регулируемых элементов 10 задержки подключены к выходам дополнительных усилителей 9 считывания, а выходы — к стробирующим входам регистра 11 числа.

Если регистр 11 числа выполнен на микросхемах, представляющих собой

43 с1 -разрядные универсальные регистры и имеющие один стробирующий вход а

5 — нагрузочная способйость дополнительных усилителей 9 считывания, число дополнительных разрядных шин 50 б, дополнительных усилителей 9 считывания- и регулируемых элементов

10 задержки определяется формулой

Временные диаграммы работы предлагаемого запоминающего устройства, 5 4 обозначают: С1 " ток опроса, 6 сигнал на входе усилителя считывания, 6 — - сигналы на выходах усилителей считывания (сплошной линией изобра-. ражен сигнал, сформировавшийся быстрее всех, пунктирной — сигнал, сформировавшийся медленнее всех), Ч. -стробирующий сигнал, 3 — сигнал на выходе регистра числа.

Устройство работает следующим образом.

На вход регистра 1 адреса пос.упает адрес, по которому необходимо произвести считывания информации из накопителя 3. С выхода регистра 1 адреса информации поступает на формирователь 2 тока опроса, сигналы из которого подаются на адресные шины

4 накопителя 3. Опросный ток (фиг.2а) возбуждает запоминающие элементы 7 на выбранной адресной шине 4, прошитые основными 5 и дополнительными 6 разрядными шинаьж. Считанный сигнал (фиг. 2б) с основных разрядных шин 5 поступает на основные усилители 8 считывания, а с дополнительных разрядных шин 6 — на дополнительные усилители 9 считывания.

Из-за разбросов параметров усилите.лей 8 и 9 считывания сигналы на их выходах появляются неодновременно (фиг. 2в) °

Примем за точку отсчета начало появления входных сигналов на входах основных усилителей 8 считывания. Обозначим через самое позднее время появления сигнала на выходах основных усилителей 8 считывания, через t — самое раннее время окончания сигнала на их выходах, Величины „ и t зависят от длительности входйого сигнала и разброса параметров усилителей 8 считывания.

Фронт стробирующего импульса (фиг. 8г) должен находиться во временном интервале от „ до t . Время задержки зависит также от формы сигнала.

Время задержки определяется по формуле где gt — величина времени задержки, устанавливаемая элементами 10 задержки

Г - величина времени задержки в соответствующем дополнительном усилителе 9 считывания.

5 892475 ь

Максимальная длительность строби- формирователь тока опроса, накопитель,,рующего импульса не должна превышать основные и дополнительные усилители длительность такта, а минимальная считывания, причем выходы регистра цлительность должна обеспечивать устойчивый прием информации в регистр з рователя тока опроса, выходы которо11. числа. Сигнал на выходе регистра го соединены с адресными шинами

11 ет вид изображенный на числа имеет вид, накопителя, входы основных усилителей считывания подключены к основным фиг. 2д.

Так как, стробирование сигнала пРо разрядным шинам накопителя, а выхоизводится непосредственно в регист- 10 ды — к информационным входам регистре 11 числа, уменьшается время про- ра числа, входы дополнительных уси" бега информации от накопителя 3 до лителей считывания соединены с дорегистра числа и на входах послед- полнительными разрядными шинами како

t него устраняется нестабильность вре пителя, о т л и ч а ю щ е е с я менного расположения сигналов. з тем, что, с целью повышения быстроЭто позволяет уменьшить длитель действия устройства, оно содержит ность сигнала при устойчивом приеме регулируемые элементы задержки, входы информации в регистр ll числа, что, которых подключены к выходам дополнив свою очередь, позволяет сократить тельных усилителей считывания, а цикл считывания, а значит, увели- выходы — к стробирующим входам речить быстродействие запоминающего гистра числа. устройства без снижения его помехоустойчивости. Источники информации, Изобретение по сравнению с извест- принятые во внимание при экспертизе ным устройством обладает более вы- 1. Авторское свидетельство СССР

М - 537387, кл. 6 ll С 7/06, 1975.

1 l

Запоминающее устройство, содержа- 2. 11атент США У 364 5 9, щее регистр адреса, регистр числа,, кл. 340-1.74, 1971 (прототип

892475

Составитель В Гордонова

Редактор А.Шишкина Техред Т.Маточка Корректор Н.Стец Заказ 11265 74 Тираж 648 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал НПП Патент", r. Ужгород, ул. Проектная, 4