Реверсивный счетчик абсолютных значений

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ВТВЛЬСТВУ

Сфюэ Соаетскик

Сециалистическик

Республик!

)892734 (61) Дополнительное к авт. саид-ву (51)М. Кл.з (22) Заявлено 07. 04. 80 (21) 2907205/18-21 с присоединением заявки М (23) Г)риоритет

Н 03 К 23/00

ГосударстеенныА комитет

СССР ио делам изобретений и открытиА

Опубликовано 231281. Бюллетень t49 47 (53)УДК 621 374 32 (088.8) Дата опубликования описания 23. 12. 81 (72) Авторы изобретения

Л.Г. Битно, М.Н. Козловский (7! ) Заявитель (54) РЕВЕРСИВНЫЙ СЧЕТЧИК АБСОЛЮТНЫХ ЭНАЧЕНИЙ I

Изобретение относится к импульсной технике и может быть использовано в аппаратуре различного назначения в качестве счетчика импульсов, позволяющего представлять числа с абсолютной величиной и знаком, в частности в устройствах контроля перемещений щаговых приводов технологического оборудования для производства интегральных схем.

Известен реверсивный счетчик импульсов, содержащий две входные шины, триггер знака, реверсивный счетчик импульсов, элементы И, ИЛИ и НЕ и дешифратор нулевого состояния (11. 15

Недостатком известного устройства является его относительная сложность, обусловленная наличием дешифратора нулевого состояния реверсивного счетчика импульсов. 20

Известен TBfcKe реверсивный счетчик абсолютных значений, содержащий Й счетных декад, входную шину, шину управления, шину сброса, элемент НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент

НЕ-.ИЛИ, два элемента И-ЙЕ и триггер, тактовый вход которого соединен с выходом заема последней счетной декады и с первым входом элемента НЕ-ИЛИ, второй вход которого соединен с шиной З0 сброса и со входом сброса триггера, информационный вход которого соединен с прямым выходом триггера и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с шиной управления, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом первого элемента И-НЕ и, чарез элемент НЕ с первым входом второго элемента И-НЕ, входная шина соединена со вторыми входами первого a".вто« рого элементов И-НЕ, выходы которых соединены соответственно с первым и вторым тактовыми входами первой счетной декады, выходы rtepeHoca и заема каждой счетной декады соединены соответственно с первым и вторым тактовыми входами последующей счетной декады, вход сброса каждой счетной декады соединен с выходом элемента НЕ-ИЛИ (2).

Однако устройство имеет относительно малую точность, обусловленная тем, что при переходе реверсивного счетчика через нулевое состояние теряется один входной импульс.

Цель изобретения — повышение точности

Поставленная цель достигается тем, что в реверсивный счетчик аб892734 солютных значений, содержащий и счетных декад, входную шину, шину управления, шину сброса, элемент НЕ,,элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент

HE-ИЛИ, два элемента И-НЕ и триггер, тактовый вход которого соединен с выходом заема последней счетной декады и с первым входом элемента

НЕ-ИЛИ, второй вход которого соединен с шиной сброса и со входом сброса триггера, информационный вход которого соединен с прямым выходом

10 триггера и с первым входом элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с шиной управления, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом первого эле- 15 мента И-НЕ и, через элемент НЕ с первым входом второго элемента И-НЕ, входная шина соединена со вторыми входами первого и второго элементов И-НЕ, выходы которых соединены 20 соответственно с первым и вторым тактовыми входами первой счетной декады, выходы переноса и заема каждой счетной декады соединены соответственно с первым и вторым тактовыми входами последующей счетной декады, вход сброса каждой счетной декады соединен с выходом элемента HE-ИЛИ, введен расширитель импульсов, вход и выход кото рого соединены соответственно с тактовым входом триггера и со входом загрузки первой счетной декады, информационные входы которой соединены с соответствующими генераторами логических уровней. 5

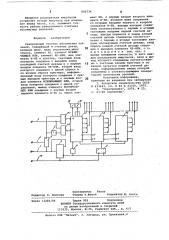

На чертеже приведена электриЧеская З схема реверсивного счетчика абсолютных значений.

Устройство содержит счетные декады

1=1 — 1=3, элементы И-НЕ 2 1 и 2 2, входную шину 3, элемент ИСКЛЮЧАЮ- 4Р

ЩЕЕ ИЛИ 4, элемент НЕ 5, шину управления б, выходную шину 7, триггер .8, элемент HE-ИЛИ 9, шину 10 сброса, расширитель 11,.генераторы 12 и 13 логических уровней соответственно 4 единицы и нуля.

Выходы переноса и заема счетных декад 1=1 и 1=2 соединены соответстI венно с первыми и.вторыми тактовыми входами счетных декад 1=2 и 1=3,вы- ® ход заема последней из которых соединен с первым входом элемента HE-ИЛИ

9, с тактовым входом триггера 8 и через расширитель 11 - co входом загрузки счетной декады 1 1, вход сброса которой соединен со входами сброса счетных декад 1е2 и 1еЗ и с выходом элемента НЕ-ИЛИ 9, второй вход которого соединен с шиной 10 сброса и со входом сброса триггера

8, информационный вход которого соединен с прямым выходом триггера 8 и с первым входом элемента 4 ИСКЛЮЧАЯЦЕЕ ИЛИ, второй вход которого соединен с шиной б управления, выход элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛЙ сое- д динен с первым входом элемента И-НЕ

2=1, и со входом элемента НЕ 5, выход которого соединен с первым входом элемента И-HE 2 2, вторые входы элементов И-НЕ 2=2 и 2=1 соединены со входной шиной 3, выходы элементов И-НЕ 2 1 и 2=2 соединены соот-. ветственно с первым и вторым тактовыми входами счетной декады 1 1,генераторы 12 и 13 логических уровней соединены с соответствующими информационными входами счетной декады 1*1.

Устройство работает следующим образом.

В соответствии с текущими состояниями шины б управления и триггера

8 информация в счетных декадах 1=1

1=3 накапливается или уменьшается.

Когда содержимое счетных декад

1=.1 — 1 3 станет равным нулю, следующий информационный импульс, поступающий со входной шины 3, пройдет на выход заема последней счетной декады 1=3 и переключит триггер 8.При этом, если число, содержащееся в счетных декадах 1=1 — 1=3 положительное, регистр знака инициирует на выходной шине 7 потенциал знака "минус", а если число отрицательное потенциал знака "плюс". Одновременно. этот импульс через элемент ИЛИ-НЕ

9 поступает на входы сброса счетных декад 1=1 - 1»»3, подтверждая их нулевое значение и, на вход расширителя 11, который увеличивает длительность поступающего на н4го импульса по сравнению с длительностью входных информационных импульсов.

Так как длительность импульса на выходе расширителя 11 больше, чем длительность импульса заема, то после окончания последнего,он заносит в первую счетную декаду 1 1 информацию, установленную генераторами 12 и

13 логических уровней на информационных входах этой декады, т.е. код "единица".

Таким образом, состояние реверсивного счетчика абсолютных значений к моменту поступления следующего информационного импульса станет равным

Ô00...1, что соответствует истинному значению информации. Далее процесс повторяется. Длительность импульса, вырабатываемого расширителем 11,выбирается из условий

ИН ЗОН ИН ЗОН Ин ясах где Фин - длительность входных информационных импульсов; „ - длительность импульса, формируемого расширителем импульсов;

Ти„ вЂ” период следования входных. информационных импульсов;

1 „ „- максимальная рабочая частота применяемых микросхем.

892734

Формула изобретения

Составитель Ранов

Техред З.фанта Корректор N. Коста

Редактор Н. Волкова

Тираж 991 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 11284/86

Филиал ППП "Патент", г. ужгород, ул. Проектная,4

Введение расширителя импульсов устраняет потерю импульса при изменении знака числа, т.е. повышает точность работы реверсивного счетчика абсолютных значений.

Реверсивный счетчик абсолютных значений, содержащий N счетных декад, входную шину, шину управления, шину сброса, элемент НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент HE-ИЛИ, два элемента И-НЕ и триггер, тактовый вход которого соединен с выходом заема последней счетной декады и с первым 15 входом элемента НЕ-ИЛИ, второй вход которого соединен с шиной сброса и со входом сброса триггера, информационный вход которого соединен с прямым выходом триггера и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с шиной управления, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом первого элемента И-HE и; через элемент НЕ, с первым входом второго элемента И-НЕ, входная шина соединена со вторыми входами первого и второго элементов И-НЕ, выходы которых соединены соответственно с первым и вторым тактовыми входами первой счетной декады, выходы переноса и заема каждой счетной декады соединены соответственно с первым и вторым тактовыми входами последующей счетной декады, вход сброса каждой счетной декады соединен с выходом элемента HE-ИЛИ, о т" л и ч а ю шийся тем, что, с целью повышения точности, в него введен расширитель импульсов, вход и выход которого соединены соответственно с тактовым входом триггера и со входом загрузки первой счетной декады, информационные входы которой соединены с соответствующими генераторами логических уровней.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 433643, кл. Н 03 К 23/00, 1975.

2. "Электроника", 1978, 9 23, с. 67-68 (прототип).