Цифровой частотомер

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ЫЯ

Х АВТОРСКОМУ СВКДЕТЕЛЬСТВУ

Союз Советскик

Социалистическими

Республик ()894592 (61) Дополнительное к авт. саид-ву (22) За н влено 05. 05,80 (21) 29 194 25/18 2 1 с присоединением заявки ¹ (25) Приоритет

Опубликовано 30.12.81. Бюллетень No. 48

Дата опубликования описания 30. 12.81 (5l)M. Кл.

G01R 23/10

91аударстмнный комитет

СССР ав делам нэобрвтеннй н открытий

ДК 621.317. .76 (088.8) (72) Авторы изобретения

В. Н. Чинков, В.Г. Войтенков и С.A. Кравченко (71) Заявитель (54) ЦИФРОВОЙ ЧАСТОТОМЕР!

Изобретение относится к цифровой электроизмерительной технике, Известен цифровой частотомер, содержащий генератор образцовой частоты, формирователь, вычитающий счетчик, два накапливающих сумматора, блок управления, ключи, схемы совпадения и управляющий триггер. Такой частотомер реализует ме тод измерения частоты, основанный на воспроизведении функции F (Т11) средствами импульсного моделирования с использо- ванием цифровых интеграторов(1).

Известный частотомер характеризуется недостаточно высоким быстродействием, ограниченным переходными процессами в накапливающих сумматорах при параллельном вводе в них чисел, невысокой точностью, обусловленной методическими погрешностями приближенного интегрирова ния и округления чисел в процессе вычисления, а также сравнительно большими емкостями сумматоров, что повышает вероятность сбоев в процессе работы.

Известен цифровой частотомер, в состав которого входят генератор тактовой частоты, два управляемых вентиля, вычи-. тающий счетчик, формирователь, блок уп"равления, система импульсно-потенциаль ных ключей, датчик калиброванных интер валов времени, управляющий триггер, делитель частоты, две схемы логического сложения н суммирующий счетчик 2, Недостатком такого частотомера является большое время измерения, которое заметно превосходит период входного сиг нала на величину калиброванного временного интервала, причем этот интервал должен быть тем больше, чем меньшую погрешность измерения необходимо обеспечивать, Кроме того, к недостаткам частотомера следует отнести методическую погрешность, обусловленную неравномерностью следования импульсов обратной связи, Наиболее близким по технической сущности к предлагаемому является цифровой частотомер, позволяющий измерять

8945 частоту за один период входного сигнала, который содержит формирователь импульсов, генератор эталонной частоты, счетчики периода и частоты, сумматор, две группы вентилей переноса, элемент задержки, вентили управления и триггеры(3)

Указанному частотомеру присуще ограниченное быстродействие, обусловленное наличием переходных процессов в сумма- 0 торе.

Цель изобретения — повышение быстродействия измерений.

Указанная цель достигается тем, что в цифровой частотомер, содержащий сумматор, формирователь импульсов, выход которого подключен к первому входу блока управления, второй вход которого соединен с выходом генератора образцовой частоты, первый выход блока управления соединен со входом счетчика периода, введены перемножитель кодов, шифратор и дешифратор, причем И выходов счетчика периода подключены к первой группе входов перемножитепя кодов, вторая группа 25 входов которого соединена с И«выходами сумматора, управляющий вход перемножителя кодов соединен со вторым выходом блока управления, управляющим входом шифратора, входом реверса суммато(и и (5 + 1) — выходом счетчика периода, остальные выходы которого начиная с (Vl + 2) -го через дешифратор подключены ко входу адреса шифратора, выход которого соединен со. входом сумматора, 35 и младших разрядов которого подключены к выходам перемножителя кодов.

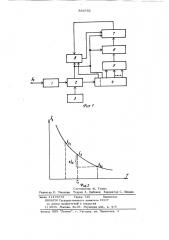

На фиг. 1 приведена блок-схема цифрового частотомера на фиг. 2 - график, Поясняющий его работу.

Устройство coneðæèT формирователь 1 импульсов, блок 2 управления, генератор

3 образцовой частоты, счетчик 4 периода, дешифратор 5, шифратор 6, сумматор

7 и перемножитель 8 колов.

Вход формирователя 1 импульсов яв ляется входом устройства, выход его подключен к одному входу блока 2 управления, другой вход которого соединен с выходом генератора 3 образцовой частоты, Первый выход блока 2 управления под50 ключен к счетчику 4 периода, к выходам разрядов которого начиная с (р + 2)-го подключен дешифратор 5, соединенный выходом со входом адреса шифратора 6.

Шифратор 6 поразрядно подключен к сум- 55 матору 7, который выполнен реверсивным.

Выходы а младших разрядов счетчика 4 периода подключены к первой группе вхо

92 4 дов перемножителя 8 кодов, вторая группа входов которого соединена с abacoaeми сумматора 7. Выходы перемножителя

8 кодов подключены к И младшим разрядам сумматора 7. Управляющие входы перемножителя 8 кодов и шифратора 6, вход реверса сумматора 7 и (М + 1) разряд .счетчика 4 периода обьединены между собой и подключены ко второму выходу блока 2 управления.

Устройство работает следующим образом.

В исходном состоянии счетчик 4 периода и сумматор 7 находятся в нулевом состоянии. Измерение производится и два этапа, На первом этапе производится пре» образование периода Т,< измеряемой чаототы в код путем заполнения периода, Ф который выделяется блоком 2 управления по сигналам формирователя 1 импульсов, соответствующим переходам входного сигнала через нуль, импульсами с генератора 3 образцовой частоты „

На втором этапе по коду Тс определяеюя код частоты $ по методу кусочнолинейной аппроксимации вычисления нелинейных функций. Для этого шифратор 6 схемно выполнен таким, что в зависимости от сигнала на одном из его адресных входов и на его выходах формируется код частоты, соответствующий коду перна да в узлах аппроксимации, Адресный вход шифратора 6, а следовательно, и код частоты задаются дешифр тором 5, KoTopbiff подключен к выходам разрядов счетчика 4 периода начиная с (.И + 2)vo. Это означает, что код периода в общем случае берется с недостатком, если в g младших разрядах счетчика 4 периода имеется код. Пусть, напрмер, этому коду периода соответствует частоте (фиг. 2), которая, очевидно, оказывается больше действительной, т, е. („7 (Код частоты $< по сигналу блока 2 управления записывается в сумматор 7 на суммирование.

Затем это значение указанной частоты уточняется интерполированием. Йля этого в (И + 1)-ый разряд счетчика 4 периода вводится единица по сигналу блока 2 управления, с дешифратора 5 по дается разрешающий потенциал íà сле дующий адресный вход шифратора 6, со-; ответствующий ближайшему меньшему значению частоты, например, (, причем

7 Х, . Сигналом блока 2 управления, подаваемым на вход реверса сумматора 7, последний переводится в режим вычитания, а затем в него с шифратора 6

5 894 вводится код частоты f . В результате в сумматоре 7 образуется код разности частот(% - g> ). Код этой разности подается на первые входы перемножителя 8 кодов, а на вторые входы последнего поступает код, записанный в младших разрядах счетчика 4 пернода. Эти коды перемножаются, и по сигналу блока 2 управления их пронзведенне записывается в Vl младших разрядов сумматора 7, которыми предварительно обнуляется. Код этого йройзведения пропорфащенню частоты и Х с ответствующему неучтенной -частй кода периода И младшях разрядов счетчика 4 периода. для получения действительного значения частоты по сигналу блока 2 управления, поступающему на управляющий вход шифратора 6, в сумматор 7 с шифратора 6 вводится код частоты

В результате в сумматоре 7 записйваеься код частоты = Х + д „, и на етом процесс измерений заканчивается.

Таким образом, в предлагаемом цифровом частотомере обеспечивается более высокое быстродействие, чем в известном устройстве, вследствие того, что в процессе преобразования периода в код производится колько счет импульсов и исключены операции суммирования параллельных кодов, Операция определения кода частоты по zoay периода выполняется после преобразования периода и не налагает ограничений на частоту образцового генератора.

592 d

Формула изобре теglя

Цифровой частотомер, содержащий сум- . матор, формирователь импульсов, выход которого подключен к первому входу блоS ка управления, второй вход которого соединен с выходом генератора образцовой частоты, первый выход блока управления соединен со входом счетчика периода, о т л и ч а ю m и и с я тем, что, с це-!

> матора и (И + 1) -ым выходом счетчика периода, остальные выходы которого начиная с (К Ф 2) -го через дешифратор подключены ко входу адреса шнф- .

pampa, выход которого соединен со вхо2S дом сумматора, Vl младших разрядов которого подключены к выходам перемножителя кодов.

Исгочники информации, принятые во внимание пря экспертизе

S0 1. Авторское свидетельство СССР

Ж 331327, кл /01 Р, 28/10, 1972.

2. Авторское свидетельство СССР

% 370539, кл. 501 Я 23/10, 1973.

3. Авторское свидетельство СССР

3S % 347675, кл, GOl Р, 23/10, 1972.

894592 юг 7

Составитель Ю. Тюпич

Редактор И. Михеева Техред А. Бабинец Корректор С. Шомак

Заказ 11478/72 Тираж 735 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4