Устройство для сдвига информации

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советскнк

Соцнапнстнчесннк

Респу

Ф

3 (61) Дополнительное к авт. сеид-ву (22) Заявлено 240778 (21) 2648449/18-24 (5!)М. КЛ.

G 06 F 7/00 с присоединением заявки Но (23) Приоритет — 2 7.0 9.76

Государственный комитет

СССР ио декан изобретений и открытий

Опубликовано 30.12.81. Бюллетень МЯ 4 8

Дата опубликования описания 30.1281 (53) УДК 681.3 (088.8) (72) Автор изобретения

3.С. Кузин

Ленинградское ордена Октябрьской Революц инженерное морское училище им.адмирала С высш е, .

МЬФар ов а (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СДВИГА ИНФОРМАЦИИ

Изобретение откос ится к цифровой вычислительной технике и может найти применение при построении арифметического устройства цифровой вычислительной машины.

Известны многоярусные параллельные сдвигатели положительных чисел, в которых каждый j-й ярус сдвигает код íà k = 21 разрядов, (j=0,1,2...) что позволяет .набрать с помощью дискретных ступеней любое требуемое число сдвигов (1) .

Однако такие сдвигатели являются неэкономичными по оборудованию, сдвигают только положительные числа и обладают малым быстродействием.

Известен параллельный сдвигатель, содержащий в каждом разряде m последовательно включенных коммутаторов, собранных из логических элементов типа И-ИЛИ, ИЛИ (И-ИЛИ-НЕ, И-НЕ, ИЛИ-НЕ), соединенных по входу в нижнем ярусе с шинами сдвига и кодовыми шинами числа, причем i-й вход числа (i = 1 — n) соединяется с коммутаторами младших разрядов, а в (n-k)-коммутаторах старших разрядов верхнего яруса первый логический элемент И соединен с шиной знака числа, а второй элемент и упомя нутых коммута.30 торов соединен с шиной прямой выда- чи (2 ).

Однако этот сдвигатель имеет низкое быстродействие и является неэкономичным по оборудованию.

Наиболее близким к предлагаемому является устройство для сдвига информации, содержащее несколько групп (ступеней) по и логических коммутаторов (и — количество разрядов входного слова), причем информационные входы каждого i-ro логического коммутатора первой группы ( к1,...,n) соединены c i-м, (1-1)-п, ...,(i-ki-м разрядными входами устройства (где k> 1 — максимальное значение сдвига, осуществляемое логическими коммутаторами первой группы), управляющие входы каждого i-ro логического коммутатора первой груп" пы соединены с управляющими шинами сдвига на 0,1,...,k разрядов устройства, информационные входы каждого

i-го логического коммутатора последующей группы. соединены с выходами соответственным образом сгруппированных коммутаторов предыдущей группы, а управляющие входы логических коммутаторов последующих групп сое,динены с управлякщими входами сдни894 700 га на кратное числу k число разрядов устройства (3).

Недостатком известного устройства является возможность осуществления только логического сдвига и ненозможность осущестнления арифметического сдвига. Цель изобретения - расширение функциональных возможностей устройства за счет возможности арифметического сдвига. 10

Поставленная цель достигается тем, что, устройство для сдвига информации, ббдержащее две группы по п логических коммутаторов (п — количество разрядов входного слова), причем информационные входы каждого

1-ro логического коммутатора печной группы .(i=1 n) соединены с i-м (i-1)-м,...,(i-k)-м разрядными входами устройства (где k Ъ 1 — максималь" ное значение сдвига, осуществляемое 20 логическими коммутаторами первой группы), упранлякщие входы каждого i-го логического коммутатора первой группы соединены с управляющими шинами сдвига на О,l,...,k разрядов устройства, информационные входы каждого

i-ro логического коммуаттора второй группы соединены с выходЬм i-ro, (i k-1)-ro,..., (i m+(1+(„) ) (k+1)-ro логических коммутаторов первой груп- $9 пы (где m - максимальное значение сдвига, осуществляемое устройством, (х) значение целой части рационального числа х), управлянщие входы каждого

i-ro логического коммутатора второй 35 группы соединены соответственно с уцравляющими шинами сдвига на О,..., („:„-„ — )(k+1) разрядов устройства, управлякщие входы логических коммутаторов второй группы с ()(k+1)-+ 40 го по (m-k)-й соединены соответственно с управляющей шиной сдвига на (m †)с) разрядов устройства, выход i-ro логического коммутатора второй группы соединен с i-м разрядным выхо дом устройства, содержит(@)-(элемен- 45 тов ИЛИ, управлякщие входы логических коммутаторов второй группы с .((3-1) (k+1)+1| -й по j(k+1) -й соединены с

3-го элемента ИЛИ (j=l,...,(„+„ )-1), входы которого соединены с управляю- 50 щими шинами сдвига на j(k+1) (m-k) разрядов устройства, информационные .,входы логических коммутаторов первой

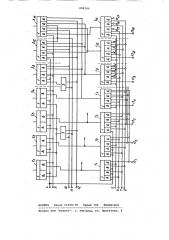

- 1 руппы с первого по k-й и логических коммутаторов второй группы с первого 55 по (m-k)-й соединены со знаковой шиной устройства, На чертеже представлено 16-ти разрядное устройство для сдвига информации, Функциональная схема. бО

Устройство содержит логические коммутаторы 1 и 2, выполненные, например, в виде мультиплексоров (инаеас i при обозначении позиции 1

2 указывает номер разряда устрой- е5 ства), элементы ИЛИ 3, знаконую шину 4, управлякщие шины 8 — 12 сдвига соответственно на 0,1,2,3,0,4,8, 12 разрядов и разрядные нходы 13.

Как в группе коммутаторов l,так и в группе коммутаторов 2 происходит разветвление каждого i-ro входа на соответствукщее количество младших разрядов с определенным. шагом. На чертеже шаг группы коммутаторов 1 равен единице,а группы коммутаторов 2 - четырем.

Пример 1. Отрицательное число 1,1100001100000000, записанное н обратном коде, сдвинем вправо на десять разрядов. В этом случае разрешающие потенциалы будут на шинах

4, 7 и 11. Проследим, как проходит сигнал сдвига только второго старшего разряда. От входа 13 сигнал проходит через коммутатор 14, с выхода которого поступает на вход коммутатора 2 0 . Поскольку число отрицательное, то с помощью коммутаторов 1, 1 и коммутаторов 14 — 18 будут сфоРмиронаны коды единиц н первых десяти старших разрядах, причем разрешающие сигналы для коммутаторов 2 формируют два элемента ИЛИ 3. На выходе коммутаторов 2 будет код

1,111111111111000.

Пример 2. Положительное число 0,1100110011001100 сдвинем вправо на дна разряда, В этом случае, разрешакщие потенциалы будут на шинах

7 и 9. Сдвиг на два разряда осуществляется коммутаторами 1, а коммутаторы 2 выдают код числа без сдвига.

На выходе устройства будет код

Оi0011001100110011.

По сравнению с известным предлагаемое устройство позволяет осуществлять не только логический сдвиг (что эквиналентно арифметическому сдвигу положительных чисел) но и арифметическии сдвиг (т.е. позволяет осуществлять сдвиг отрицательных чисел с сохранением знака). Устройство может быть. легко приспособлено для сдвига не только вправо, но и влево. Количество групп коммутаторов может быть увеличено, что хотя несколько и ухудшает быстродействие устройства, но зато позволяет дать некоторую экономию в используемом оборудовании.

Формула изобретения

Устройство,.для сдвига информации, содержащее две группы по и логических коммутаторов (п — количество разрядов входного слова), причем.информационные входы каждого i-го логического коммутатора первой группы (i=1. ..n) соединены с i-м, (i-1)-м, . ° ., (i-Е)-м разрядными нходами устройства (где k91 — максимальное значе894700 ние сдвига, осуществляемое логическими коммутаторами первой группы), управляющие входы каждого i-го логическoro коммутатора первой группы соединены с управляющими шинами сдвига на 0,1,...,k РазРядов УстРойства, информационные входы каждого i-ro логического коммутатора второй группы соединены с выходами i-го, (i-k-1)-го, ..., (i-пн- (1+ () ) (k+ 1) ) -го логических коммутаторов перв ой группы (где m — максимальное значение сдвига осуществляемое устрой ств ом; (х) эначе ние целой части рационального числа х), управляющие входы каждого

i-ro логического коммутатора второй группы соединены соответственно с управляющими шинами сдвига на О,..., (ф»)(k+1) разрядов устройства, управляющие входы логиче ских коммутаторов второй группы с j () (k+1) -k)ro по (m-)с) -й соединены" соответст - 20 венно с управляющей шиной сдвига на (m-k) pa зрядов устройства, выход

i-ro логиче ского коммутатора в торой группы соединен с i-м разрядным выходом устройтсва, о т л и ч а ю щ е е- р5 с я тем, что, с целью расширения функциональных воэможностей устройства, заключакще гося в воэможности арифметического сдвига, устройство содержит (— „. „7-1 злеме нтов ИЛИ, упф Ъ равляющие входы логиче ских коммутаторов второй группы с ((j 1) (k+1)+1)é по j (k+1) -й соединены с выходом

j -го элеме нта ИЛИ (j =1 (— „,„) -1, входы которого соединены с управляющими шинами сдвига на j (k+1),..., (m-k) разрядов устройства, информацноннье входы логических коммутаторов первой группы с первого по k-й .и логических коммутаторов второй группы с первого по (m — k) -й соединены оо знаковой шиной устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 410388, кл. G 06 F 7/00, 1974.

2. Авторское свидетельство СССР

М 595794, кл. G 11 С 19/00, 1975.

3. Патент CLIA II 3747070, кл. 340-172.5, опублик. 1973 (прототип) °