Устройство выборки микрокоманд

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистически1

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (22) заявлено 1505.78 (21) 2619487 18-24 (51) М. Кл.

G 06 F 9/36 с присоединением заявки М (23) Приоритет

Государственный комитет

СССР но делам изобретений н открытий

Опубликовано 30.1281. Бюллетень т4к48

Дата опубликования описания 30. 12. 81 (53) УДК 681. 32 5 (088. 8) (72) Авторы изобретения

Л.Я.Карпман и. A.À.ßêóáà

1

Ордена Ленина институт кибернетики АН-Украинской CCP (71) Заяв итель (5 4 ) УСТРОЙСТВО ВЫБОРКИ ИИ КРОКОМАНД

Изобретение относится. к вычислительной технике и может быть применено в цифровых вычислительных машинах с микропрограммным управлением.

Известен микропрограммный процессор, использующий общую дисковую

`амять для хранения микропрограмм и данных, причем память разбита на две самостоятельные области с регулируемой границей, предназначенные для раздельного хранения отдеЛьных подпрограмм (макрокоманд) и последовательностей отдельных микрокоманд (микропрограмм) (1).

Недостаток данного процессора состоит в том, что выбор дисковой памяти в качестве единственной памяти процессора ограничивает возможности его производительности.

Наиболее близким к предлагаемому является устройство выборки микрокоманд, содержащее блок управления, регистр микрокоманд, два блока сравнения, регистр границы управляющей памяти, регистр границы оперативной памяти, блок выделения поля, адресный сумматор, регистр адреса микрокоманды, регистр базы оперативной памяти.

В известном устройстве байтовая организация оперативной памяти. Обращение в оперативную память за очередной микрокомандой происходит только в случае ее отсутствия в управляющей памяти. Иикрокоманда, выделяемая из управляющей или опера-. тивной памяти, заносится непосредственно в регистр микрокоманд (2).

Недостатком известного устройства является существенное замедление его работы при выборке микрокоманд из оперативной памяти.

Цель изобретения — повышение

15 быстродечствия.

Поставленная цель достигается тем, что в устройство, содержащее регистр микрокоманд, первый вход которого соединен с первым входом уст20 ройства, первый вход первого блока сравнения соединен с первым выходом регистра адреса микрокоманды, а второй вход — с выходом регистра границы управляющей памяти, первый

25 вход второго блока сравнения соеди" нен с первым выходом адресного сумматора, а второй вход — с выходом регистра границы оперативной памяти, вход регистра границы оперативной

SO памяти соединен со вторым входом

894709 устройства, первый вход дешифратора поля соединен с третьим входом устройства, второй выход адресного сумматора соединен с первым входом регистра адреса микрокоманды, третий выход — с первым выходом устройства, первый вход — со вторым выходом регистра адреса микрокоманды, à ВТорой вход - с первым выходом регистра базы оперативной памяти, третий выход регистра адреса микрокоманды соединен со вторым выходом устройства, выход и первый вход блока управления, выходы двух блоков сравнения, второй вход дешифратора поля соединены c Кодовой шиной управления, выход и второй вход регистра микрокоманд, вход регистра границы управляющий памяти, первый выход дешифратора поля, второй вход адресного сумматора, четвертый выход регистра адреса микрокоманды, а также вход и второй выход регистра базы оперативной памяти соединены с кодовой шиной данных, введены триггер и регистр хранения микрокоманд, причем выход триггера соединен со вторым входом блока управления, а вход — с кодовой шиной управления, вход регистра хранения микрокоманд соединен со вторым выходом дешифратора поля, первый выход регистра хранения микрокоманд соединен со вторым входом регистра микрокоманд, а второй выход — с кодовой ши-, ной данных.

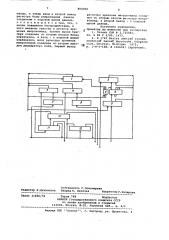

На чертеже представлена блок-схема устройства выборки микрокоманд.

Устройство выборки микрокоманд содержкт блок 1 управления, регистр

2 микрокоманд, первый блок 3 сравнения, второй блок 4 сравнения, регистр 5 хранения микрокоманд, триггер б, регистр 7 границы Управляющей памяти, регистр 8 границы оперативной памяти, дешифратор 9 поля, адресный сумматор 10, регистр 11 адреса микрокоманды, регистр 12 базы оперативной памяти.

Триггер б предназначен для хранения управляющего признака, а регистр

5 хранения микрокоманд — для предварительного хранения микрокоманды или константы, автоматически выбираемых из оперативной памяти вместе с очередной выполняемой микрокомандой.

Работа устройства выборки микрокоманд синхронизируется блоком 1 управления, который управляет выборкой микрокоманд иэ управляющей или оперативной памяти и занесением очередной выполняемой микрокоманды в регистю 2 микрокоманд.

Информация о местоположении очередной выполняемой микрокоманды - в оперативной или управляющей памяти вырабатывается двумя блоками 3 и 4 сравнения соответственно и поступает на кодовую шину управления.

gg При обнаружении признака наличия очередной выполняемой микрокоманды в управляющей памяти блок 1 управления инициирует выборку очередной микрокоманды из управляющей памяти по

45 .адресу, передаваемому из регистра 11 адреса микрокоманды через второй выход устройства. При отсутствии . указанного признака блок 1 управления анализирует признак наличия

5О очередной выполняемой микрокоманды в оперативной памяти. Исходными данными, поступающими на входы блока 4 сравнения для выработки данного признака, являются граничное значение выделенной области оперативной.памяти, хранящееся в регистре 8 границы оперативной памяти, а также адрес микрокоманды, формируемый ад- ресным сумматором 10 по содержимому регистра 11 адреса микрокоманды Щ и значению базового адреса опера-, тивной памяти, хранящемуся в регистре 12 базы .оперативной памяти. Содержимое регистра 8 границы оперативной памяти устанавливается через второй вход устройства, содержимое

1Î

ЭО

В пеРвую очередь блоком 1 управления анализируется признак наличия очередной выполняемой микрокоманды в управляющей памяти. Исходили данными, поступающими на входы блока 3 сравнения для выработки указанного признака, являются граничное значение выделенной области управляющей памяти, хранящееся в регистре 7 границы управляющей памяти, а также адрес микрокоманды, хранящийся в регистре 11 адреса микрокоманды.

Содержимое регистра 7 границы управляющей памяти устанавливается через кодовую шину данных, содержимое регистра 11 адреса микрокомакды формируется непосредственно в данном регистре, либо заносится в него из адресного сумматора 10 или через кодовую шину данных. При линейном следовании микрокоманд отсчет очередной микрокоманды выполняется непосредственно в регистре 11 адреса микрокоманды, выступающем в роли счетчика. При нарушении такого следования, вызываемом микрокомандами условного или безусловного перехода, а также обращения к подпрограмме, адрес очередной мккрокоманды формируется в регистре ll адреса микрокоманды адресным сумматором 10 по адресу текущей микрокоманды, содержащемуся в регистре 11 адреса микрокоманды, и относительному смещению, поступающему на вход адресного сумматора 10 из регистра 2 мккрокоманд через кодовую шину данных. При выполнении микрокоманд, изменяющих содержимое регистра 11 адреса микрокоманд, новое значение заносится в него через кодовую шику данных.

89 4709

t0

30

Формула изобретения

45 ройства, первый вход дешифратора поля соединен с третьим входом устрой- ства, второй выход адресного сумматора соединен с первым входом регистра адреса микрокоманды, третий выход - с первым выходом устройства, первый вход - со вторым выходом регистра адреса микрокоманды, а второй вход — с первым выходом регистра базы оперативной памяти, третий выход регистра адреса микрокоманды соединен со вторым выходом устройства, выход и пер вый вход блока управления, выходы двух блоков сравнения, второй вход дешифратора поля соединены с кодовой

60.шиной управления, выход и второй вход регистра микрокоманд, вход регистра границы управляющей памяти, первый выход дешифратора поля, второй вход адресного сумматора, четвер65 тый выход регистра адреса микрокорегистра 12 базы оперативнои памяти — через кодовую шину данных.

Наличие данного признака указывает на возможное обращение эа очередной микрокомандой в оперативную память по адресу, передаваемому иэ адресного сумматора 10 через первый выход устройства, отсутствие данного признака — на аварийное обращение.

Микрокоманда, считываемая из управляющей памяти, через первый вход устройства поступает непосредственно в регистр 2 микрокоманд. Микрокоманды, считываемые в составе слова иэ оперативной памяти, через третий вход устройства поступают на вход дешифратора 9 поля, который выполняет выделение поля каждой микрокоманды из данного слова. Очередная выполняемая микрокоманда через второй выход дешифратора 9 поля и кодовую шину данных также поступает в регистр 2 микрокоманд, а микрокоманда, автоматически выбираемая вместе с очередной выполняемой микрокомандой, через вход 13 регистра 5 хранения микрокоманд заносится в регистр 5 хранения микрокоманд.

Дешифратор 9 поля имеет универсальное назначение и используется при обработке полей переменной длины в ходе выполнения микрокоманд, описывающих работу с полем оперативной памяти. Данная обработка предполагает выделение или занесение поля переменной длины в слове оперативной памяти, а также сдвиг поля на требуемую величину. Управляющая информация, задающая размер поля и необходимую величину его сдвига., поступает в дешифратор поля с кодовой шины управления.

Цикл выполнения каждой микрокоманды начинается с занесения ее в регистр 2 микрокоманд через один из трех его входов, а также с анализа местоположения и запуска цикла выборки микрокоманды,следующей в.микропрограмме за выполняемой. Если.в результате анализа такая микрокоманда обнаружена в управляющей памяти, то укаэанный запуск выполняется безусловно. Если в результате анализа такая микрокоманда обнаружена в оперативной памяти, то наличие регистра 5 хранения микрокоманд и триггера 6 позволяет не выполнять указанный запуск, если в составе слова оперативной памяти данная микрокоманда уже была выбрана из оперативной памяти на предыдущем цикле обращения к ней.

При необходимости выполнения такой микрокоманды обращение за ней в оперативную память заменяется пересылкой данной микрокоманды иэ регистра 5 хранения микрокоманд в регистр 2 микрокоманд через выход 14.

Признак наличия требуемой микрокоманды фиксируется в триггере б. В ходе работы устройства этот, признак постоянно анализируется и корректируется блоком 1 управления соответственно через выход 15 и вход 16 блока. Занесение микрокоманды из оперативной памяти в регистр 5 хранения микрокоманд сопровождается установкой триггера б в 1, а пересылкой этой микрокоманды в регистр 2 микрокоманд - установкой этого триггера в 0

Регистр 5 хранения микрокоманд с выхода 17 выдает на кодовую шину данных константу, автоматически считанную из оперативной памяти вместе с очередной выполняемой микрокомандой.

Информация о наличии такой кон- станты аналогичным образом фиксируется в триггере 6.

Таким образом, включение регистра

5 хранения микрокоманд и триггера б в устройство выборки микрокоманд

1 обеспечит 50%-ную экономию числа обращений в оперативную память при выполнении линейной последовательности микрокоманд, расположенных в оперативной памяти, что повышает производительность процессора.

Устройство выборки микрокоманд, содержащее регистр микрокоманд, первый вход которого соединен с первым входом устройства, первый вход пер- вого блока сравнения соединен с пепвым выходом регистра адреса микрокоманды, а второй вход — с выходом регистра границы управляющей памяти, первый вход второго блока сравнения соединен с первым выходом адресного сумматора, а второй вход — с выходом регистра границы оперативной памяти, вход регистра границы оперативной памяти соединен со вторым входом уст894709

Сост ав и тель Г. По н омаре ва

Редактор Е.Дичинская Техред T. Маточка Корректор Г.Назарова

Тираж 748 Подписное

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 11490/78

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 манды, а также вход н второй выход регистра базы оперативной памяти соединены с кодовой шиной данных, о т л и ч а ю ш е е с я тем, что, с целью повышения быстродействия, в него, введены триггер и регистр хранения микрокоманд, причем выход триггера соединен со вторым входом блока управления, а вход — с кодовой шиной управления, вход регистра хранения микрокоманд соединен со вторым выходом дешифратора поля, первый выход

) регистра хранения микрокоманд соединен со вторым входом регистра микрокоманд, а второй выход — с кодовой шиной данных.

Источники информации, принятые во внимание при экспертизе

1. Патент CIJA 9 3.725862, кл. G 06 F 3/00, 1973.

2. В 1720 Series central system, technical manual Burroughe. corparation, Detroit, Michigan 1975, 1-4-1-108 9 1066941 (прототип) °