Дифференцирующее устройство

Иллюстрации

Показать всеРеферат

Союз Соыетсник

Социапистические

Респубпии

ИСАНИЕ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свид-ву (22)Заявлено 110130 (21) 2868896/18-24 с присоединением заявки РЙ(23)Приорнтет(51) М. Кл.

6 06 G 7/18

3есударственный квинтет

Опубликовано 30.1231. Бюллетень Рй 48

Дата опубликования описания 30.12Я1 (53) УДК 681. 335 (088.8) по делаи нзабретеннй н открытнй

В.Ф.Ермаков

1

Новочеркасский ордена Трудового Красного Знамени политехнический институт им. Серго Орджоникидзе (72) Автор изобретения (7l ) Заявитель (54) ДИФФЕРЕНЦИРУЮЦЕЕ УСТРОЙСТВО

Изобретение относится к аналоговой вычислительной технике и может быть использовано, в частности, в электроэнергетике.

Известное устройство, предназначенное для определения уровня производной напрлжения, содержит блок выделения модуля приращений напряжения, пороговое устройство, триггеры, генератор прямоугольных импульсов, элемент И, элемент задержки (1).

Недостатком данного устройства является возможность фиксации с его помощью только определенного уровня производной напряжения.

Наиболее близок к предлагаемому дифференциатор напряжений, содержащий операционные усилители, диодноемкостные запоминающие ячейки, генератор прямоугольных импульсов, триггер, инвертор НЕ, элементы задержки (2).

Недостатком известного дифференциатора является возможность получе:ния с его помощью только первой про

1 изводной исследуемого напряжения.

Цель изобретения — расширение функциональных возможностей за счет получения производных выше первого порядка.

Поставленная цель достигается тем, что дифференцирующее устройство, содержащее две пары операционных усилителей, первые неинвертирующие вхото ды которых соединены со входом устройства, два запоминающих конденсато ра, четыре разделительных диода и генератор прямоугольных импульсов, выход которого соединен с единичным

15 входом триггера, при этом выходы операционных усилителей первой пары через соответствующие разделительные диоды, включенные встречно-параллель20 но соединены с первой обкладкой первого запоминающего конденсатора и первыми инвертирующими входами опера ционных усилителей второй пары, вы,ходы которых через соответствующие

894728

Зо

35 ю формула изобретения

55 разделительные диоды, включенные встречно-параллельно, соединены с первой обкладкой второго запоминающего конденсатора, вторые обкладки запоминающих конденсаторов соединены . с шиной нулевого потенциала, содержит дополнительно второй генератор прямоугольных импульсов, (п 1)-канальный распределитель уровней (где

n - максимальный порядок производной), .(n-1) пар операционных усилителей, 2(п-1) разделительных диодов и (и-1) запоминающих конденсаторов, причем первые неинвертирующие входы операционных усилителей каждой из ,(n-1) пары соединены со входом устройства, выходы операционных усилителей каждой из (и-1) пары соединены через соответствующие разделительные диоды, включенные встречно-параллельно,с первой обкладкой соответствующего запоминающего конденсатора, первая обкладка каждого i-ro запоминающего конденсатора (1 «Л 1 и+1), соединенная с соответствующим выходом устройства, соединены с соответствующими инвертирующими входами операционных усилителей каждой j-ой пары (1+1 «j «» и+1), в каждой i -ой паре операционных усилителей соответствующий инвертирующий вход первого и BTQ рой неинвертирующий вход второго связаны с (n â€, i + 2)-ым выходом распределителя уровней, выход второго генератора прямоугольных импульсов соединен со счетным входом распредегителя уровней, (n+1)-ый выход которого соединен с нулевым входом триггера, инверсный выхоц которого соединен со входом установки нуля распределителя уровней.

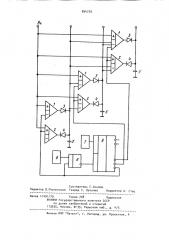

На чертеже представлена схема устройства (для случая двухкратного дифференцирования).

Устройство содержит операционные усилители 1и 2, разделительные диоды 3 и 4, запоминающие конденсаторы

5, генераторы б и 7 прямоугольных импульсов, распределитель 8 уровней и триггер 9.

Предлагаемое устройство работает следующим образом.

При нулевом состоянии триггера 9 единичное напряжение с его инверсного выхода приложено ко входу установки нуля распределителя уровней 8, что удерживает последний также в нулевом состоянии несмотря на то, что на его счетный вход поступают импульсы генератора 7. При этом единичное напряжение с выходов распределиTeJlR .3 приложено ко входам смещения усилителей 1 и 2, в результате напряжение на конденсаторах 5 поддерживается постоянным и равным для каждого конденсатора значению, накопленному в предыдущем такте работы устройства.

Появление очередного импульса генератора 6 приводи к срабатыванию триггера 9, который снимает единичное напряжение со входа установки нуля распределителя 8 и на его выходах поочередно с частотой R генератора 7 2 и Г„ появляются нулевые потенциалы. Нри этом происходит поочередное обновление информации, зар0 .поминаемой на конденсаторах 5.

Напряжение, запоминаемое на конденсаторах 5, представляет собой приращение соответствующего порядка, которое является, как известно, линейной композицией входного сигнала и приращений более низкого порядка.

При появлении сигнала на последнем, (n+1)-ом, выходе распределителя 8 триггер 9 снова переводится в нулевое состояние, распределитель 8 остается в нулевом состоянии и все диоды снова оказываются закрытыми до начала следующего такта.

Устройство работает аналогично как при отрицательных, так и при положительных производных, а также при отрицательных значениях входного сигнала. При его запуске переходный процесс в вычислении i-ой производной заканчивается через i тактов.

Технико-экономический эффект от использования предлагаемого устройства определяется использованием простой элементной базы и возможностью микроминиатюризации при расширенных функциональных возможностях. дифференцирующее устройство, содержащее две пары операционных усилителей, первые неинвертирующие входы которых соединены со входом устройства, два запоминающих конденсатора, четыре разделительных диода и генератор прямоугольных импульсов, выход которого соединен с единичным входом триггера, при этом выходы операцион5 8 ных усилителей первой пары через соответствующие разделительные диоды, включенные встречно-параллельно, соединены с первой обкладкой первого запоминающего конденсатора и первыми инвертирующими входами операционных усилителей второй пары, выходы которых через соответствующие разделительные диоды, включенные встречно-параллельно, соединены с первой обкладкой второго запоминающего конденсатора, вторые обкладки запоминаю" щих конденсаторов соединены с шиной нулевого потенциала, о т л и ч а ю— щ е е с я тем, что, с целью расширения функциональных возможностей эа счет получения производных выше первого порядка, устройство содержит дополнительно второй генератор прямоугольных импульсов, (и + 1)-канальный распределитель уровней, где и - максимальный порядок производнои, (n — 1) пар операционных усилителей, 2 n - 1) разделительных диодов и (n — 1) запоминающих конденсаторов, причем первые неинвертирующие входы операционных усилителей каждой из (n - 1) пары соединены со входом устройства, выходы операционных усилителей каждой из (и — 1) пары соединены через соответствующие разделительИсточники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N 524189 кл. G 06 G 7/12, 1975.

2. Авторское свидетельство СССР

30 591371, кл. G 06 G 7/18, 1976 (прототип).

94728 4 ные диоды, включенные встречно-параллельно, с первой обкладкой соответствующего запоминающего конденсатора, первая обкладка каждого i-го запомиS:Hàþùåãî конденсатора (1 1 и+1), соединенная с соответствующим выходом устройства, соединена с соответствующими инвертирующими входами операционных усилителей каждой j-ой

l0 пары (i+16 j< n+1}, в каждой i-ой . паре операционных усилителей соответствующий инвертирующий вход первого и второй неинвертирующий вход второго связаны с (n - i + 2)-ым выходом

t5 распределителя уровней, выход вторЬго генератора прямоугольных импульсов соединен со счетным входом распределителя уровней, (и + 1)-ый выход которого соединен с нулевым входом триггера, инверсный выход которого соединен со входом установки нуля распределителя уровней.

894728

Составитель Г.Осипов

Редактор Л.Пчелинская Техред Т. Маточка Корректор H. Стец

Заказ 11491/79 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35; Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4