Интегратор

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистическик

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

«ii 894730 (6I ) Дополнительное к авт. саид-ву (22) Задавлено 040480 (21) 2904345/18-24 (5l)M. Кл.

G 06 G 7/186 с присоединением заявки МГааударстеаиный камитет (23) Приоритет— па делам иэааретеиий и аткрытий

Опубликовано 30,1 281. Бюллетень № 48

Дата опубликования описания 30.1281 (53) УД1 681 335 (088.8У (72) Авторы изобретения

8. Н. Лапенко и И. К. Герасин

Московский институт электронной тех (71) Заявитель (г4) ИНТЕГРАТОР

Изобретение относится к вычислительной технике и может быть использовано в устройствах автоматики и измерительной техники, в частности в устройствах сжатия динамического диапазона и других функциональных преобразователях.

Известны матеграторы, в которых логарифмическое сжатие осуществлено путем подключения к выходу интегратора комплементарных логарифмических преобразователей (1).

Недостаток известных интеграторов с логарифмическим сжатием результата интегрирования заключается в их сложности, так как в интегратор вводятся дополнительные операционные усилители.

Кроме того, ухудшается отношение сигнал/шум, особенно для слабых сигналов. Это вызвано наличием шумовой составляющей во входном каскаде логарифматора,а также воздействием наводок на проинтегрированный сигнал до лога рифмического преобразования его, несмотря на непосредственную близость интегратора и логарифматора.

Наиболее близок к предлагаемому по технической сущности интегратор, содержащий токоэадающую цепь, выходом связанную с одним из концов конденсаторов и входом операционного усилителя (2j.

Недостатком данного интегратора

10 является невозможность выполнения логарифмического сжатия одновременно с интегрированием, т.е. он имеет or" раниченные функциональные возможности.

Цель изобретения - расширение функциональных воэможностей интегратора за счет логарифмического сжатия проинтегрированного сигнала.

Поставленная цель достигается

20 тем, что в интегратор, содержащии токозадающую цепь, выход которой соединен с .одним из выводов интегрирующего конденсатора и входом операционного усилителя, а вход является входом интегратора, введены дополнитель ные интегрирующие конденсаторы и двусторонние ограничители, причем дополнительные интегрирующие конденсаторы, соединены последовательно и включены между другим выводом интегрирующего конденсатора и выходом операционного усилителя, а параллельно каждому интегрирующему конденсатору поДключен двусторонний ограничитель.

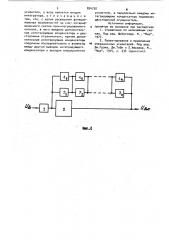

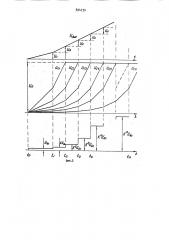

На фиг. 1 представлена схема интегратора; на фиг. 2 и 3 - временные диаграммы работы интегратора.

Интегратор содержит токозадающую цепь 1, операционный усилитель 2, в цепи отрицательной обратной связи которого включены и последовательно соединенных интегрирующих конденсаторов 3,...,3„ и п двусторонних ограничителей 44,...,41,, каждый из которых параллельно подключен к соответствующему конденсатору.

Интегратор работает следующим образом.

П-ри появлении в момент времени (Фиг. 2) на входе интегратора минймально возможного напряжвния 0 < начинается процесс интегрирования (усреднения). Постоянная интегрирования выбирается таким образом, что минимальному среднему значению 0 х соответствует напряжение U< на выходе интегратора. При увеличении вход,ного напряжения от величины 0> до ,,kU < a момент времени и скорость заряда конденсаторов также возрастает в К раз. В момент времени t. напЙ ряжение на конденсаторе 3 достигает уровня ограничения 0 и в дальнейшем не меняется, при этом напряжения, до которых заряжаются остальные n"1 конденсаторы, при условии CggCp С:

C4<... C> (где С - емкость конденсаторов) меньше U . При дальнейшем увеличении входного напряжения от величины 1(0 до k 0Вх {момент времени и

g ) скорость заряда остальных .и-1 конденсаторов дополнительно возрастает в К раз. В момент времени t уровня ограничения Uo достигает найряжение на конденсаторе 3 и так далее.

Выходное напряжение интегратора определяется суммой напряжений, на которре заряжаются каждый из конденса" торов эа время интегрирования, при этом максимальное напряжение, до которого может зарядиться каждый кон9.4730, 4 денсатор, определяется уровнем ограничения U соответствующего ограничителя.

Таким образом,. напряжение на выходе интегратора 0ь и уровень, их ограничения U при условии, что о

25 формула изобретения

55 Интегратор, содержащий токоэадающую цепь, выход которой соединен с одним иэ выводов интегрирующего конденсатора и входом операционного р

08Х " т " 0в>(С4 ° Си4

10 и все ограничители имеют один уро.вень. ограничения 0ю, а 1()) 1, соответственно равны

К +2. К + ъ

0%1Х С 458 + С J 15®+ С 13Ж+"

15 "tO 14

К +>>.

° "— Х,а

С1 6>>-1 (t+ (tq g u

U = — Ж= — jii>%= -= ) 4>sB<

20 141 С1 1Я С1 tnгде t - t< ... t< - t> "время, за которое соответствующий конденсатор заряжается до уровня 0О, > - величина тока токозадающей цепи, Из (1) и (2) видно, что при увеличении уровня входного сигнала в К раз, выходное напряжение интегратора в точках, соответствующих переходу ограничителей в режим ограничения, получает постоянное приращение U

Ю

Следовательно, требования, предьявляемые к логарифмическому сжатию, удовлетворяются.

На фиг. 3 представлена временная диаграмма работы интегратора при наличии на его входе скачка напряжения с постоянной амплитудой.

Таким образом, введение в интег40 ратор и последовательно соединенных емкостей и и двусторонних ограничителей, каждый из которых подключен параллельно к соответствующему конденсатору, позволяет одновременно с

45 процессом интегрирования (усреднения) выполнять операцию логарифмического сжатия, т.е. расширяет функциональные воэможности интегратора.

Кроме того, предлагаемый интегратор улучшает отношение сигнал/шум.

894730 усилителя, а вход является входом интегратора, отличающийся тем, что, с целью расширения функциональных возможностей за счет логарифмического сжатия проинтегрированного сигнала, в него введены дополнительные интегрирующие конденсаторы и двусторонние ограничители, причем дополнительные интегрирующие конденсаторы соединены последовательно и включены между другим выводом интегрирующего конденсатора и выходом операционного

d усилителя, а параллельно каждому интегрирующему конденсатору подключен двусторонний ограничитель.

Источники информации, принятые во внимание при экспертизе

1. Справочник по нелинейным схемам. Под ред. Юейнголда. М., "Иир", 1977.

2. Проектирование и применение

10 операционных усилителей, Под ред.

Дж.Грэма, Дж.Тоби и Л.Хюсмана. M., "Мир", 1974, с. 234 (прототип).

Составитель С.Белан

Редактор Л.Пчелинская Техред 3. Фанта )(орректор "А. Ференц

Заказ 11491/79 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, ))1-35, Раушская наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4