Устройство для контроля блоков оперативной памяти

Иллюстрации

Показать всеРеферат

(22) Автор изобретения

В. Г. Рябцев

3 с

1 Д вычислительных машин (7!) Заявитель

Научно-исследовательский институт уцравляющи (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ

ОПЕРАТИВНОЙ ПАМЯТИ

Изобретение относится к запоминающим устройствам и может быть использовано для контроля интегральных полупроводниковых оперативных запоминающих устройств.

Известно устройство для контроля блоков памяти, содержащее элементы ИЛИ, регистры, 5 блоки сверток по модулю два, схему сравнения, блок управления (11.

Недостатком устройства являются большие аппаратурные затраты.

1а

Наиболее близким по технической сущности к предлагаемому является устройство для контроля блоков оперативной памяти, содержащее накопители, формирователь адресных сигналов, Схему сравнения,, блок управления (2), В известном устройстве несимметричность

-информационного кода обеспечивает обнаружение только константных ошибок дешифратора адреса блока памяти при считывании и проверке информации, например, наличие постоянного уровня нуля или единицы на адресных

20 шинах, и не позволяет обнаружить динамические неисправности, связанные с увеличением времени задержки включения дешифраторов адреса, так как строки и столбцы матрицы памяти, имеющие одинаковое дополнение до четности содержат одинаковую информацию, что снижает надежность устройства. Также уст. ройство характеризуется большими аппаратурными затратами.

Цель изобретения — упрощение и повышение надежности устройства.

Поставленная цель достигается тем, что в устройство для контроля блоков оперативной памяти, содержащее микропрограммный блок управления, первый выход которого подключен ко входу адресного блока, второй выход — к первому входу блока хранения контрольных данных, выход которого соединен с первым входом схемы сравнения и является первым выходом устройства, вход которого подключен ко входу блока хранения считанных данных,. выход которого соединен со вторым входом схемы сравнения, выход которого подключен ко входу микропрограммного блока. управления, введены преобразователь кодов, счетчик, коммутатор и сумматор по модулю лва, причем третий выход микропрограммного блока управления соединен со входом счетчика, выход которого подключен к первому входу коммутатора, выход адресного блока соединен со входом преобразователя кодов . и вторым входом коммутатора и является вторым выходом устройства, выходы преобразователя кодов и .коммутатора подключены ко входам сумматора по модулю два, выход которого соединен со вторым входом блока хранения контрольных данных, 10

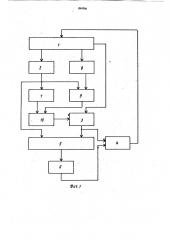

При этом целесообразно преобразователь кодов выполнить в виде блока, содержащего элементы И, входы которых являются входами преобразователя кодов, а выходы подключены ко входам сумматора по модулю два, выход которого является выходом преобразователя кодов, На фиг. 1 приведена структурная схема устройства для контроля блоков оперативной памяти; на фиг. 2 — структурная схема пре» 20 образователя кодов.

Устройство содержит микропрограммный блок 1 управления, первый выход которого подключен ко входу адресного блока 2, а второй выход — к первому входу блока 3 25 хранения контрольных данных, выход которого подключен к первому входу схемы 4 сравнения и является первым выходом устройства.

К первому и второму выходам и входу устройства подключаются соответственно входы и 30 выходы контролируемого блока 5 паьйти.

Устройство также содержит блок 6 хранения считанйых данных преобразователь 7 кб., дов, счетчик 8, коммутатор 9 и сумматор.10 по модулю два. Третий выход блока 1 соединен со входом счетчика 8, выход которого подключен к первому входу коммутатора 9.

Выход блока 2 соединен со входом нреобразователя 7 и вторым входом коммутатора 9 и является вторым выходом устройства. Вы- 40 ходы преобразователя 7 и коммутатора 9 подключены ко входам сумматора 10, выход которого соединен со вторым входом блока 3.

894796

На выходе сумматора 12 формируется код матрицы Адамара, элементы которой образуются. путем преобразования кода адреса при помощи уравнения

h х у = (Б х .у) mod 2.

s-! !

Логические функции столбцов матрицы Адамара имеют вид:

= О, f2 = @

Таким образом, коды столбцов матрицы Адамара образуют как результат проверки .!а четность разрядов Кода адреса -строк, при этом перебираются проверки всех разрядов кода адреса строк во всех сочетаниях.

Устройство работает следующим образом.

При использовании устройства дяя контроля полупроводникового блока памяти емкостью

16кбит,собранного из четырех микросхем памяти емкостью 4 кбит, для выбора конкретной микросхемы памяти используют, разряды кода адреса аз и а2. Контроль осуществляют в два этапа. Вначале в проверяемый блок 5 записывают код, полученный путем преобразования младших разрядов кода адреса в код матрицы Адамара, сложенный по модулю два с первым старшим разрядом кода адреса а!.

По программе блока 1 блок 2 формирует код адреса, который поступает на вход бло:ка 5, на второй вход коммутатора 9 и вход преобразователя 7. При помощй сумматора 10 по модулю два осуществляется сложение ко. да матрицы Адамара и первого старшего разряда кода адреса а>, полученная сумма заносится в блок хранения контрольных данных 3 по команде- блока l.

Контрольные данные записывают в проверяемый блок 5. В циклах считывания информации с блока 5 запоминается блоком хранения считанных данных 6. Сравнение считанных и контрольных данных осуществляется схемой

4 сравнения. Результаты сравнения поступают на вход блока 1.

Преобразователь кодов 7, представляюший собой формирователь элементов матрицы Адамара, составленной из элементов +1 и — 1, со- держит (фиг. 1) элементы И 11, входы которых являются входами преобразователя 7, а выходы подключены ко входам сумматора 12 по модулю два, выход которого является выходом преобразователя 7. На первые входы элементов И 13 с выходов блока 2 поступают коды адреса хз, х2, ..., х, которые используются дня выбора строк микросхем памяти е . проверяемого блока памяти, на вторые входы элементов И с выходов блока 2 поступают коды адреса уз, у2, ..., у„, которые использу- . ются для выбора столбцов микросхем памяти.

Во время второго этапа проверки содержимое счетчика 8 увеличивается на единицу и через коммутатор 9 на вход сумматора 10 по модулю два поступает код второго разряда адреса а2.

Операции записи, считывания и сравнения повторяются, при этом в проверяемый блок 5 записывают код, полученный путем преобразо. вания кода адреса в код матрицы Адамара и, сложенный по модулю два со вторым разрядом кода адреса а2, Во время первого этапа проверки инфор. мация в микросхемах памяти принимает еле. дующее значение: Н, Н, Н, Н, во время второго этапа проверки получают следующее зна1. Устройство для контроля блоков оперативнои памяти, содержащее микропрограм- 2я иный блок управления, первый выход которого подключен ко входу адресного блока, второй выход — к первому входу блока хранвния;контрольных данных, выход которого соединен с первым входом схемы сравнения н является первым выходом устройства, вход которого подключен ко входу блока хранения считанных данных, выход которого соединен со вторым входом схемы сравнения, выход которой подключен ко входу мнкропрограмнение распределение информации в микросхемах памяти: Н, Н, Й, Й. . Таким образом получают все возможные сочетания, когда информация данной микросхемы памяти отличается от информации в других микросхемах памяти. Данная тестовая последовательность позволяет обнаружить неиспрйвпости.не только микросхем памяти, но и деннфраторов выбора микросхем памяти, Технико-экономический эффект от внедрения предлагаемого устройства достигается за счет сокращения времени контроля и уменьшения емкости памяти микропрограммного блока команд.

Формула изобретения

94796 Ь много блока управления, о т л и ч а ю щ е- .

- е с я тем, что, с целью упрощения и повыщения надежности устройства, оно содержит преобразователь кодов, счетчик, коммутатор

S и сумматор по модулю два, причем третий выход микропрограммного блока управления соединен со входом -счетчика, выход которого подключен к первому входу коммутатора, выход адресного блока соединен со входом преобразователя кодов и вторым входом коммутатора и является вторым выходом устройства,эыходы преобразователя кодов и коммутатора подключены ко входам сумматора по модулю два, выход которого соединен со вторым входом блока хранения контрольных данных.

2. Устройство по и. 1, о т л и ч а ющ е е с я тем, что..преобразователь кодов содержйт элементы И,. входы которых являютса входами преобразователя кодов, а выходы подключены ко входам сумматора по модулю два, выход которого является выходом преобразователя кодов.

2S Источники информации, принятые во внимание при экспертизе

1. Harem GllA Р 4012033, кл. 340 — 146Л, опублнк. 1977.

2. "Известия вузов. Радиоэлектроника", зо 1977, У 1, с. 41-44 (прототип). 894796

Х212

Xg 3

Хд

Ъ

Состааитель В. РИрков

Редактор В. Пилипенко Техред А;Бабинец .. Корректор С. Комак

Заказ 11500/83 Тираж 648 Подписпое

ВНИИПИ Государственного комитета СССР по делам изобретений и открыпй

113035, Москва, Ж-35, Раушскан наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. ПроЬктная, 4