Умножитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических т еслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 0805.80 (21) 2922512/18-21 (5 ) М с присоединением заявки Но

Н 03 К 5/156

Государственный комитет

СССР но делам изобретений и открытий (23) Приоритет

Опубликовано301281 Бюллетень МВ 48

Дата опубликования описания 30.1281 (З) УДК 621. З74. . 4 (088. 8) (72) Авторы изобретения

В.Н.Лебедев, В.Н.Попов, В.И.Карпов и М.М.Макаров (71) Заявитель

Пензенский политехнический институт (54) УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ

ИМПУЛЬСОВ

Изобретение относится к автоматике и измерительной технике и может найти применение в различных информационно-измерительных систе5 мах.

Известно устройство для умножения частоты следования периодических импульсов, содержащее входной и выходной формирователи, управляющий блок. делитель частоты, два счетчика .импульсов, запоминающий регистр и блоки переноса (1).

Недостаток данного умножителя частоты — невысокая точность умножения, так как период выходного сигнала не равен периоду входного сигнала, поделенного на коэффициент умножения.

Наиболее близким по технической сущности к изобретению является 20 устройство для умножения частоты следования импульсов, содержащее последовательно соединенные генератор опорной частоты, первый делитель частоты и счетчик импульсов, выходы которого соединены с информационными входами регистра, синхровход которого соединен с вторым входом первого делиТеля частоты, с входной ши. ной и через элемент задержки с уста. 30 новочным входом счетчика импульсов, выходы старших разрядов с управляющими входами второго делителя час тоты, в выходы всех разрядов — с соответствующими входами третьего делителя частоты, счетный вход которого соединен с выходом генератора опорной частоты и со счетным входом второго делителя частоты, установочный вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом третьего делителя частоты, а второй вход — с установочным входом третьего делителя частоты и вторым входом первого делителя частоты (2).

Недостаток известного устройстваневысокая точность умножения, обусловленная неравномерной расстановкой импульсов выходной последовательности.

Цель изобретения — повышение точности умножения.

Для достижения этой цели в умножитель частоты следования импульсов, содержащий последовательно соединенные генератор опорной частоты, первый делитель частоты и счетчик импульсов, выходы которого соединены с инФормационными входами регистра, 894847 вход синхронизации которого соединен с вторым входом первого делителя частоты, и со входной шиной непосредственно и через элемент задержки с установочным входом счетчика импульсов, а выходы старших разрядов — с управляющими входами второго делителя частоты, введены двоичный умножитель частоты и блок вычитания, первый вход которого соединен с выходом двоичного умножителя частоты, второй вход — с Выходом

10 генератора опорной частоты, а выход-. с входом второго делителя частоты, выход которого соединен со счетным входом двоичного умножителя частоты, управляющие входы которого соеди- 15 .нены с выходами младших разрядов регистра.

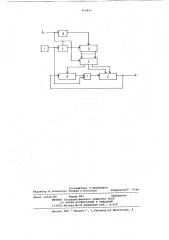

На чертеже представлена структурная схема устройства.

Схема содержит генератор 1 опор- 2О ной частоты, делители 2 и 3 частоты, счетчик 4 импульсов, регистр 5, двоичный умножитель б частоты, блок 7 вычитания, элемент 8 задержки.

Устройство работает следующим

25 образом.

Импульсы с выхода генератора 1 поступают на вход делителя 2, коэффициент деления которого равен коэффициенту умножения устрой тва М. Импульсы с выхода делителя 2 поступают на вход счетчика 4, где формируется кодовый эквивалент периода входного сигнала fg . Код периода входного сигнала N из счетчика 4, в момент окончания очередного периода Тх переписывается в регистр 5. Число, записанное в регистре 5, можно представить N = а в с, (где а, в, с— число единиц, записанных в старшей, средней и младшей I декадах) . Значе- gg ние периода входного. сигнала при этом . можно записать Тх — — (авс)М "g гдее

М вЂ” коэффициент умножения, о — период следования импульсов опорной частоты.

Код из старших разрядрв регистра

5 переписывается в делитель 3, а из младшего разряда — в двоичный умножитель б. Частота сигнала на выходе блока 7 равна

О 6 где К - частота сигнала на выходе блока 7, f6 - частота сигнала на выходе двоичного умножителя 6.

Если предположить, что з наче н ие кода 55 в младшей декаде регистра 5 равно

0 (т.е. е = 0 ), то частота на выходе двоичного умножителя 6 Г6= О,и частота с генератора 1 через блок

7 проходит на вход делителя 3. Пе- 4() риод сигнала на выходе устройства прн этом равен, = (;,р)-..., коэффициент умножения х («о) +" к = о р„, ььiх («)

При с ф 0 на вход делителя 3 поступает переменная частота, так как на каждый импульс с выхода двоичноного умножителя б исключается один импульс из последовательности импульсов, поступающих с генератора 1.

При этом увеличение одного периода сигнала на входе делителя 3 составит д . В результате период сигнала на выходе устройства также увеличивается на, и составит C .= (ав+1) г (Ивх

i,ãäå И6,„ - длительность скорректированного периода. Введение в умножитель частоты следования импульсов двоичного умножителя, блока вычитания и новых связей позволяет уменьшить погрешность от неравномерности расстановки импульсов выходного сигнала, т.е. повысить точность умно1 жения,что дает возможность измерято частоту, начиная с любого момента и .за необходимый промежуток времени.

Формула изобретения

Умножитель частоты следования импульсов, содержащий последовательно соединенные генератор опорной частоты, первый делитель частоты и счетчик импульсов, выходы которого соединены с информационными входами регистра, вход синхронизации, которого соединен с вторым входом первого делителя частоты и со входной шиной непосредственно и через элемент задержки — с установочным входом счетчика импульсов, а выходы старших „ разрядов — с управляющими входами второго делителя частоты, о т л и ч а ю шийся тем, что, с целью повышения точности умножения, в него введены двоичный умножитель частоты и блок вычитания, первый вход которого соединен с выходом двоичного умножителя частоты, второй вход — с выходом генератора опорной частоты,а выход — с входом второго делителя частоты, выход которого соединен со счетным входом двоичного умножителя частоты, управляющие входы которого соединены с выходами младших разрядов регистра.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

У 357668,кл.Н 03 К 5/01, 09.03.71.

2. Авторское свидетельство СССР

Р 660228, кл. Н 03 К 5/156, 10.11.76.

8 .Э 484 7

Составитель О.Кружилина

Редактор И.Ковальчук Техред С.Мигунова Корректор ° Ог P Г. Ога

Заказ 11506/85 Тираж 991 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035,Москва,Ж-35,Раушская наб., д.4/5

Филиал ППП Патент, r.Óæãîðoä,óë.Ïðîåêòíàÿ, 4