Одновходовый многозначный универсальный элемент

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (»)894868 (61) Дополнительное к авт. свид-ву(22)Заявлено 26.11. 79 (21) 2867235/18-21 с присоединением заявки М— (23) Приоритет— (51)M. Кл.

H 03 K 19/08

Ваударетаеааый кеннтет

СССР во делам нзебретеинй и атхрытнй

Опубликовано 30.12.81. Бюллетень J% 48

Дата опубликования описания 30 . 12 .81 (53) УДК 621 ° 374 (088.8) (72) Авторы изобретения

А. Е.Бобров, В.В.Григорьев и В.A.журкин

Ленинградский ордена Ленина институт инженеров: железнодорожного транспорта им. акад. В.Н.Образцова (7I) Заявитель (54) ОДНОВХОДОВОЙ МНОГОЗНАЧНЫЙ УНИВЕРСАЛЬНЫЙ

ЭЛЕМЕНТ

h (x) Изобретение относится к импульсной технике и может быть использовано в схемах цифровой автоматики как базовый элемент, выполненный в виде интегральной схемы на основе современной технологии производства.

Известно устройство, которое позволяет реализовать произвольную функцию многозначной логики, содержащее входы настройки от источника базовых напряжений, h-дешифратор и

10 ключи "Минимум". Многозначные универсальные схемы с одним информационным входом содержат h-дешифратор, состоящий. из k устройств, реали13 зующих характеристические функции

К-1, X =oL

4 (Х О,Х1Ы d.ЬЕк= о,ф >Фг> " К- мнргозначной логики. Выходы этих устройств соединяются с первыми входами ключей "Минимум", вторые входы ко2 торых соединены с выходами источника базисных напряжений. Выходы ключей "Минимум" с помощью схемы "Максимум" соединяются с выходом многозначного элемента, Реализация произвол ь ной функции многозначной логики осуществляется при соответствующем подключении выходов источника базисных напряжений ко вторым входам многозначных ключей

»Минимум >1 1 ).

Недостаток устройства - большая рассеиваемая мощность.

Наиболее близким к предлагаемому является устройство, содержащее

h-дешифратор, т.е. устройство реализующее k" 1 схему функций многозначной логики hg(x) и содержащее

2(k-1)+1 транзистора, а также k+I транзистора схемы формирования произвольной функции многозначной логи(2).

Недостаток устройства - большая рассеиваемая мощность.

89486

40

Цель изобретения - уменьшение рассеиваемой мощности.

Поставленная цель достигается тем, что в одновходовой многозначный универсальный элемент, содержащий

h-дешифратор, устройство формирования произвольной функции, введены двухвходовые элементы объединения, устройства вычитания, второй h-дешифратор, соединенный ортогонально с >0 первым й-дешифратором, выходы которого соединены со входом устройства квантования сигнала, выход которого соединен с первым входом устройства вычитания, вход универсального элемента со вторым входом устройства вычитания, выход которого соединен с рходом второго h-дешифратора, выходы которого попарно с выходами первого

h-дешифратора соединены со входами двухвходовых элементов объединения, выходы которых соединены с первыми входами, а шины сигнала настройки со вторыми входами схем формирования произвольнои функции, выходы которых соединены с выходом универсального элемента.

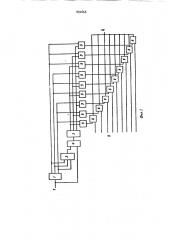

На фиг. 1 представлена функциональная схема устройства; на фиг,2конкретная электрическая схема на

30 элементах, выполненных на U Я. - технологии, промышленное изготовление которых налажено отечественной промышленностью s виде ИС или БИС (пунктиром выделены соответствующие узлы функциональной схемы устройства), на фиг.3 - материал, поясняющий работу устройства.

Устройство 1 реализуют hy функции многозначной логики со значностью (h-дешифратор на k выходов), f устройство 2 реализует функции многозначной логики со значностью (h-дешифратор на Г выходов), устИ ройство 3 формирует дискретные значения входной величины, устройство 4 вычитает из входного значения его квантованное значение, устройство 5 суммирует токи выходов h-дешифраторов, устройство 6 формирует реализуемую произвольную функцию, схема содер- S0 жит вход 7 элемента, выход 8 элемента, настроечные входы 9 элемента °

Устройство функционирует следующим образом.

Входной сигнал, поступающий на ss вход элем лта 7 передается на вход

h-gee @pa pa 1 с числом дискретных состояний k (как бы грубых) с

8 4

k -1 выходами и одновременно на один из входов устройства вычитания 4, в котором из входного значения сигнала выполняется вычитание его квантованного значения, полученного в устройстве 3 формирования дискретного квантованного значения входной величины, выход устройства 4 вычитания подсоединен к входу h-дешифратора 2 с числом дискретных значений k" и k - 1 выходами (фиг.1); на одtf ном из выходов каждого из h-дешифраторов выходные сигналы совпадают на одном из устройств 5 объединения выходов (или устройств совпадения), который подсоединен на один из двух входов устройства 6 формирования реализуемой производной функции, другой вход которой является настроечным входом 9 и формирует значение этой функции, соответствующее сочетанию значения сигнала в квантованных диапазонах k u k ; выбранное значение

I /л настроечного входа подается на выход

8 элемента.

Конкретная электрическая схема (фиг.2) функционирует следующим образом.

Входной сигнал на первом транзисто ре разветвляется на два канала, один

1 из которых подсоединен на h-дешифратор с дискретным значением А и выпол ненный по U R технологии по известной схеме. По одному коллектору средл них транзисторов h-дешифратора выведены и подсоединены к устройству 3 формирования квантованного сигнала.

Сумма токов транзисторов на выходе устройства 3 всегда соответствует грубому значению квантованного сигнала и на устройстве 4 вычитается из значения тока, равного входному сигналу, Это переводит оставшееся значение тока по второму каналу в диапазон изменения k и дискретным значе l ниям Ьс ; вычитание значений тока

tl поступает на h-дешифратор (нижняя часть фиг.2), выполненный по известной аналогичной h-дешифратору схеме, в верхней части фиг.2 происходит объединение выходов и-дешифратоtt ра и h-дешифраторр, Причем входному сигналу соответствует то единственное устройство 5, на выходе которого значение вытекающего тока будет равно О; выбранный выход устройства 5 подсоединен к соответствующему входу схемы устройства 6 формирова5 894868 ния реализуемой произвольной функции (фи г. 2, 3) . Ток по выбранному выходу устройства 5 равен i=O, а ток вектора настройки i=ify. Схема формирования, реализованная с помощью тран- З зистора с замкнутым коллектором, формирует ток выхода устройства i, =1fy.

На остальных выходах устройства 6 коллекторный ток равен О.

Предлагаемое устройство позволяет уменьшить число транзисторов, используемых для реализации, что приво- дит к значительному уменьшению рассеиваемой мощности.

4 вания сигнала, выход которого соединен с первым входом устройства вычитания, вход элемента - со вторым входом устройства вычитания, выход которого соединен с входом второго

h-дешифратора, выходы которого попарно с выходами первого h-дешифратора соединены со входами двухвходовых рлементов объединения, выходы которых соединены с первыми входами, а дины сигнала настройки со вторыми входами схем формирования произвольной функции, выходы которых соединены с выходом универсального элемента.

Формула изобретения

Одновходовой многозначный универсальный элемент, содержащий h-дешифратор схему формирования произволь" ной функции, отличающийся тем, что, с целью снижения рассеиваемой мощности, введены двухвхо- довые элементы объединения, устройство вычитания, второй Ь-дешифратор, соединенный ортогонально с первым

h"äåøèôðàòîðîì, выходы которого соединены со входом устройства квантоИсточники информации, принятые во внимание при экспертизе

1. Кметь А.Б., Раков M.A., 20

Ланцов А.И.нВопросы построения и организации многозначных элементов и структур". Сб. "Июгозначные элементы и структуры". Киев, "Наукова думка", 1975, с. 10, рис. 6.

2. IEEE Transactions on Computers„

voi. С"26, No12, december 1977

Т.Т1ch, Dao, Edward, i. Иа!usky, dewis, К.Визге! Hu it ivalued inject i-q, on, Logic, р. 1233, fig 8.