N-разрядный двоичный счетчик

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 261279. (21) 2882415/18-21

<и>894876 ©е (Я)м. кл.з с присоединением заявки М—

Н 03 К 23/00

Государственный комитет

СССР ио делам изобретений и открытий (23) Приоритет

Опубликовано 3012.81 бюллетень М 4 8 (S3) УДК 6 2 1. 374 .. 32 (088. 8) Дата опубликования описания 30.12.81 (72) Авторы изобретения

Г.C.Áðàéëoâcêèé, И.М.Лазер, П.И.Ов ищер и, О.g, рьщов (71) Заявитель

ВИЬАИ,:"" (54) N-РАЭРЯДНЫИ ДВОИЧНЫИ СЧЕТЧИК

Изобретение относится к устройст вам импульсной техники и может быть использовано при построении измерительных приборов и узлов цифровой вычислительной техники.

Известен двоичный счетчик, содержащий счетных вход и и разрядов, каждый из которых содержит RSтриггер на логических элементах

И-НЕ(ИЛИ-HE), и три логических элемента И-НЕ(ИЛИ-НЕ), кроме того, и раэряд содержит четвертый элемент

И-НЕ(ИЛИ-НЕ), причем выход первого элемента каждого разряда соединен с

S-входом триггера и входом третьего 15 элемента этого разряда, R-входами триггеров и входами первых элементов предшествующих разрядов, выход второго элемента каждого разряда, кроме n-ro соединен со входами перво- 20 го и третьего элементов последующего разряда, выход второго элемента

n-ro разряда соединен со входом четвертого элемента п-.ãî разряда, выход третьего элемента каждого разряда соединен со входами первого и второго элементов этого разряда, выход четвертого элемента и-го разряда соединен с R-входами триггеров и входами первых элементов всех разрядов, 30 а счетный вход соединен со входами первых элементов всех разрядов и четвертого элемента и-го разряда)1).

Недостатком этого двоичного счетчика является сравнительно низкое быстродействие.

Известен также N-разрядный двоичный счетчик, содержащий N RS-триггеров, многоустойчивый элемент и йе-1 дополнительных элементов

И-НЕ(ИЛИ-НЕ), каждый RS-триггер содержит первый и вторсй элементы

И-НЕ.(ИЛИ-НЕ), входы которых соединены с выходами соответственно второго и первого элементов И-НЕ(ИЛИ-НЕ) того же RS-триггера, многоустойчивый элемент содержит Nt.1 вспомогательных элементов И-НЕ(ИЛИ-НЕ), выход каждого из которых соединен с входами всех остальных вспомогательных. элементов И-НЕ(ИЛИ-НЕ), выход каждого 1-oro вспомогательного элемента И-НЕ(ИЛИ-НЕ) соединен с входом первого элемента И-НЕ(ИЛИ-НЕ)

i-oro RS-триггера и входами вторых элементов И-HE(ИЛИ-НЕ) предыдущих RS-триггеров, входы вспомогательных элементов И-НЕ(ИЛИ-НЕ) соединены с входом й-разрядного двоичного счетчика, выход второго эле894876 мента И-НЕ(ИЛИ-HE) каждого i-ого

RS-триггера соединен с входом i-ого дополнительного элемента И-НЕ(ИЛИ-НЕ) а выход первого элемента И-НЕ(ИЛИ-НЕ)

М-ого разряда соединен с входом М+1ого дополнительного элемента

И-НЕ(ИЛИ-НЕ) (2) .

Недостатком этого N. — ðàçðÿäíîãî двоичного счетчика является срав— нительно низкое быстродействие.

Цель изобретения — повЫшение быстродействия.

Поставленная цель достигается тем, что в М-разрядном двоичном счетчике, содержащем М RS-триггеров, многоустойчивый элемент и М+1 дополнительных элементов И-НЕ(ИЛИ-НЕ},. каждый

RS-триггер содержит первый и второй элементы И-НЕ(ИЛИ-HE), входы которых соединены с выходами соответственно второго и первого элементов

И-НЕ(ИЛИ-НЕ) того же RS-триггера, многоустойчивый элемент содержит

М 1 вспомогательных элементов

И.-НЕ(ИЛИ-НЕ), выход каящого иэ которых соединен с входами всех остальных вспомогательных элементов

И-НЕ(ИЛИ-НЕ), выход каждого I-ого вспомогательного элемента И-НЕ(ИЛИ-НЕ соединен с входом первого элемента

И-НЕ(ИЛИ-ИЕ) !-oro RS-триггера и входами вторых элементов И-НЕ(ИЛИ-НЕ) предыдущих RS-триггеров, входы вспомогательных элементов И-НЕ(ИЛИ-НЕ) соединены с входом N-разрядного,, двоичного счетчика, выход второго элемента И-НЕ(ИЛИ-НЕ) каждого i-oro

RS-триггера соединен с входом i-ого дополнительного элемента И-НЕ(ИЛИ-НЕ) а выход первого элемента И-НЕ(ИЛИ-НЕ)

М-ого разряда соединен с входом

М+1-ого дополнительного элемента

И-НЕ(ИЛИ-НЕ), выход каждого i-ого дополнительного элемента И-НЕ(ИЛИ-НЕ) соединен с входами всех вспомогательных элементов И-НЕ(ИЛИ-НЕ),кроме

1-ого, выход каждого .i -ого вспомогательного элемента И-НЕ(ИЛИ-НЕ) соединен с входами всех дополнительных элементов И-НЕ(ИЛИ-НЕ),кроме l-ого, а выход первого элемента И-НЕ(ИЛИ-НЕ) каждого i-ого RS-триггера соединен с входами дополнительных логических элементов И-НЕ(ИЛИ-НЕ), начиная с

1+1-ro.

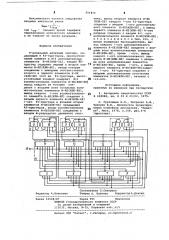

На чертеже показана структурная схема первых трех разрядов М-разрядного двоичного счетчика.

Двоичный счетчик содержит RS-триггеры 1-3, многоустойчивый элемент

4 и четыре дополнительных элемента

5-8 И-НЕ(ИЛИ-НЕ), каждый М-триггер содержит первый 9 и второй 10 элементы И-НЕ(ИЛИ-HE), входы которых соединены с выходами соответственно второго 10 первого 9 элементов

И-НЕ(ИЛИ-НЕ)того же RS-триггера, многоустойчивый элемент содЕржит четыре вспомогательных элемента 1114 И-НЕ(ИЛИ-НЕ), выход каждого иэ которых соединен с входами всех остальных вспомогательных элементов И-НЕ(ИЛИ-НЕ), выход каждого

i-ого вспомогательного элемента .И-НЕ(ИЛИ-НЕ) соединен с входом первого элемента И-НЕ(ИЛИ-НЕ)1-ого

RS-триггера и входами вторых 10 элементов И-НЕ(ИЛИ-НЕ) предЫдущих

RS-триггеров, входы вспомогатель®О ных элементов 11-14 И-, НЕ(ИЛИ-НЕ) соединены с входом 15 двоичного счетчика, а выход второго элемента 10 И-НЕ(ИЛИ-НЕ) каждого i-oro

RS-триггера соединен с входом 1-oro .дополнительного элемента И-HE (ИЛИ-HE), а выход первого элемента 9 И-HE (ИЛИ-НЕ)последнего разряда соединен с входом последнего дополнительного элемента И-НЕ(ИЛИ+НЕ), выход каждого 1.-ого дополнительного элеменЩ та И-НЕ(ИЛИ-НЕ) соединен с входами всех вспомогательных элементов И-НЕ

I (ИЛИ-НЕ), кроме С-ого, выход каждого t-ого вспомогательного элемента И-НЕ(ИЛИ-НЕ) соединен с входа 5 ми всех дополнительных элементов

И-НЕ(ИЛИ-НЕ), кроме 1-oro, а выход

) первого элемента И-НЕ(ИЛИ-ЙЕ) каждого 1-ого RS-триггера соединен с входами дополнительных логических элементов И-НЕ(ИЛИ-НЕ), начиная с

+1-ого.

Двоичный счетчик работает следующим образом.

При состоянии логического нуля на входе 15 в зависимости от состояния RS-триггеров 1,2 или 3 один кз элементов 5-8 установлен в нулевое логическое состояние, а все остальные установлены в состояние логической единицы. Так, если элемент

10 И-НЕ(ИЛИ НЕ) первого й5-триггера установлен в состояние логического нуля, а в единичное состояние установлен элемент 5 И-НЕ(ИЛИ-НЕ). Фронт счетного импульса на входе 15 вызы45 вает переключение в нулевое логическое состояние одного из элементов

11-14 И-НЕ{ИЛИ-НЕ), после чего происходит переключение RS-триггеров разрядов таким образом, что в едияп ничное состояние устанавливается

RS-триггер соответствующего разряда, а все RS-триггеры младших разрядов устанавливаются в состояние логического нуля. Затем один из элементов 5-8 И-НЕ(ИЛИ-НЕ) переключается из нулевого логического состояния в единичное. Срез счетного импульса на входе 15 вызывает переключение из состояния догического нуля в состояние логической единицы одно60 го из элементов 11-14 И-НЕ(ИЛИ-НЕ), после чего устанавливается состояние логического нуля на выходе одного из элементов 5-7 или 14 И-НЕ(ИЛИ-HE)

Далее процесс счета повторяется

65 аналогичным образом.

894 876

Формула изобретения.15

Составитель О.Скворцов

Техред A. Бабинец Корректор А.Дзятко

Редактор А.Власенко

Заказ 11508/87 Тираж 991 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб.,4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная,4

Максимальная частота следования входных импульсов равна

4 чакс = кс -5t + где tq< - среднее время задержки переключения логического элемента и не зависит от числа разрядов. й-разрядный двоичный счетчик, содержащий М RS-триггеров, многоустойчивый элемент и И+1 дополнительных элементов И-НЕ(ИЛИ-НЕ), каждый RSтриггер содержит первый и второй эле- 1 менты И-НЕ(ИЛИ-HE), входы которых соединены с выходами соответственно второго и первого элементов И-НЕ (ИЛИ-НЕ).того же RS-триггера, многоустойчивый элемент содержит й+1 20 вспомогательных элементов И-НЕ (ИЛИ-НЕ) выход каждого из которых соединен с входами всех остальных вспомогательных элементов И-НЕ(ИЛИ-НЕ), выход каждого i-ого вспомогательного элемента И-НЕ(ИЛИ-НЕ) соединен с входом первого элемента И-НЕ(ИЛИ-НЕ)

i-oro RS-триггера и входами вторых элементов И-НЕ(ИЛИ-НЕ) предыдущих

RS-триггеров, входы вспомогательных элементов И-НЕ(ИЛИ-НЕ) соединены с входом М-разрядного двоичного счет-, чика, выход второго элемента И-HE (ИЛИ-HE) каждого i-ого RS-триггера соединен с входом i-oro дополнительного элемента И-НЕ(ИЛИ-НЕ), а выход первого элемента И-НЕ(ИЛИ-HE) N -ого разряда соединен с входом й+1 -ого дополнительного элемента И-НЕ(ИЛИ-НЕ), отличающийся тем, что, с целью повышения быстродействия, выход каждого i-ого дополнительного элемента И-НЕ(ИЛИ-НЕ) соединен с входами всех вспомогательных элементов

И-НЕ(ИЛИ-НЕ), кроме i-ого, выход каждого 1-ого вспомогательного элемента И-НЕ(ИЛИ-НЕ) соединен с входами всех дополнительных элементов

И-НЕ(ИЛИ-НЕ), кроме i-oro, а выход первого элемента И-НЕ(ИЛИ-ЙЕ)каждого i-ого RS-триггера соединен с входами дополнительных логических элементов И-НЕ(ИЛИ-НЕ), начиная с

i+1-ого.

Источники инФормации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 418982, кл. Н 03 К 23/02, 1975.

2. Гуртовцев A.Ë., Петренко A.Ô., Чапенко В.П.. Логическое проектирование устройств автоматики, "Зинатне", Рига, 1978, с.148, рис.5-6 (прототип).