Декодер

Иллюстрации

Показать всеРеферат

ОЛИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (»)896614

К АВТОРСКОМУ СВИДИЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 13 278 (21) 2697280/18-21 (51)м, кл.

G 06 F 5/00 с присоединением заявки Ио (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано07р182. Бюллетень Hо 1

Дата опубликования описания 07. 01. 82 (53) УДК 621.317.7 (088.8 }

И.И. Кузнецов, В.A. Зимин, Ф.3. Келлер и В.В. Замятин

1 ., (72) Авторы изобретения

Пермский политехнический институт (71) Заявитель (54 } ДЕКОДЕР

Изобретение относится к импульс. ной технике и предназначено для использования в телемеханике, связи и других системах передачи цифровой информации.

Известны декодирующие устройства, выполненные на базе регистров сдвига с логическими обратными связями, и известны комбинационные дешифраторы, которые выполняют по матричной схеме с применением логических элементов И с различным числом вхо-. дов (1).

Наиболее совершенным является декодер, содержащий последовательно соединенные. синхронизатор, распределитель и дешифратор, регистр, вы.полненный в виде последовательно соединенных первого элемента И, трех триггеров, первого сумматора по мо-. дулю два и второго элемента И,многовходовый элемент И, третий элемент И, элемент ИЛИ, вход которого соединен с выходами распределителя, а выход †-с синхронизирующими входами триггеров регистра, нулевые выходы первого и третьего триггеров и единичный выход второго триггера регистра соединены с соответствующими входами многовходового элемента И, выходом подключенного к первому входу третьего элемента И, выход второго. элемента И соединен с ,выходом первого элемента И, выход. второго триггера регистра подключен к одному из входов сумматора по модулю два, выходы диодной матрицы являются выходами устройства 1 2).

Однако при увеличении разрядности кода и числа минимальных кодовых колец усложнятся построение элементов И, которые дешифрируют кодовые кольца, необходим отдельный регистр сдвига с К-ячейками, предназначен I5 ный только для дешифрации принятого кода. Декодирование принятой кодовой комбинации, т.е. выделение истинных информационных символов, это устройство пройзводить не может, 20 и для этой цели требуется дополнительное оборудование.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что в декодер, содержащий последовательно соединенные синхронизатор, первым входом подключенный к входной шине, распределитель и дешифратор, регистр, выполненный в виде

30 последовательно соединенных первого

896614

)0

d0

65 элемента И, первого, второго и третьего триггеров, первого сумматора по модулю два и второго элемента И, многовходовой элемент И, третий элемент И, элемент ИЛИ, вход которого соединен с выходами распределителя, а выход - с синхронизирующими входа,ми триггеров и регистра, нулевые вы ходы первого и третьего триггеров, а также единичный выход второго триггера регистра соединены с соответствукщими входами многовходового элемеита И, выходом подключенного к первому входу третьего элемента И, выход второго элемента И соединен с выходом первого элемента И, выход второго триггера регистра подключен к одному из входов первого сумматора по модулю два, выход дешифратора является выходом устройства,содержит элемент сравнения, выполненный в виде последовательно соединенных четвертого элемента И, второго сумматора по модулю два и пятого элемента И, два управляющих триггера, прйчем первый .вход первого управляющего триггера соединен с одним из выходов распределителя, другой вход — с первым выходом синхронизатора, а первый и второй выходы - с первыч входом первого элемента И и с объединенньэли первыми входами второго, четвертого и пятого элементов И соответственно, выход последнего соединен с вторым входом синхронизатора, третий вход которого подключен к выходу третьего элемента И и к соответствующим входам дешифратора, один из входов второго сумматора по модулю два подключен к выходу первого триггера регистра, второй выход синхронизатора соединен с вторыми входами первого и.четвертого элементов И, вход второго управляющего триггера соединен с одним из выходов распределителя, а выход триггера подключен к одному из входов третьего элемента И.

Таким образом, упрощается наиболее громоздкая часть декодирующего устройства (дешифратор) за счет использования кольцевых свойств двоичных кодов, Число К входовых элементов И, определяемых в известном устройстве числом дешифрируемых колец, равное вЂ, где К вЂ число информа2 ционных символов кода, в предназначенном устройстве введено до минимума, т.е. до одного.

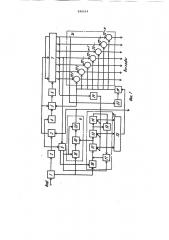

На фиг. 1 представлена схема декодера; на фиг; .2 — временная диаграмма его работы.

Предлагаемый декодер содержит входной блок 1, селектбр 2 пускового элемента, сбФасывакщий узел 3, фазорегулятор 4, пусковой узел 5, генератор 6 импульсов, распределитель 7, первый. управляющий триггер

8, элемент 9 сравнения, в состав которого входит сумматор 10 по модулю два, регистр 11 сдвига с логической обратной связью, выполненный на триггерах 12-14 и сумматоре 15 по модулю два, элементы И 16-20, дешифратор 21 на элементах И 22 (22-1,22-2...22-n), триггер 23,элемент ЙЛИ 24, многовходовый элемент И 25.

Элементы 1-6 составляют схему синхронизатора 26.

После выделения синхронизирующего импульса и подготовки всей схемы к приему информации, которая производится с помощью селектора 2 пускового элемента и сбрасывающего узла 3, регулируется фаза начала работы спускового узла, по сигналу которого начинает работать генератор импульсов 6. При этом распределитель 7 выдает импульсы через элемент ИЛИ 24, которые являются тактовыми импуль- сами для регистра 11 с логической обратной связью. Поскольку первый управляющий триггер 8 подключен к селектору 2 и к распределителю 7, то по сигналу с селектора 2 в начале цикла триггер 8 устанавливается в состояние "1" и открывает элемент И 16, через который в регистр 11 под действием тактовых импульсов, посту-. пающих в распределитель через элемент ИЛИ 24, записываются информационные символы принимаемой. кодовой комбинации. Сигналом с (К+1) ячейки распределителя первый триггер переводится в состояние "0", при этом закрывается вход регистра сдвига (запирается элемент И 16) и открываются вход и выход элемента 9 срав-. нения, т.е. отпираются элементы И 18, 20 и замыкается цепь обратной связи в регистре 11 (открывается элемент

И 17).

Начиная с (К+1) такта работы распределителя,в регистре образуются проверочные символы, вычисляемые по принятым информационным. Эти символы с выхода первого триггера регистра подаются на элемент И 19, на второй вход которого поступают проверочные символы, принимаемые из линии связи.

При.правильном приеме кодовой комбинации проверочные символы,вычисленные и принятые, совпадают, и сигнала защитного отказа не последует.

На такте работы распределителя сигналом с последней ячейки распределителя второй управляющий триггер

23 устанавливается в состояние "1", т.е. открывается элемент И 19. При дальнейшей работе регистра сдвига на определенном такте, номер которого зависит от положения символов кодовой комбинации в кодовом кольце, происходит срабатывание много896614 входового.элемента И 25, настроенного на опорную комбинацию кольца.Распределитель 7 импульсов при этом за (n-K+N) тактов, где n — длина кода, К - число информационных символов и и — номер информационной части кодовой комбинации в кольце, производит выбор выходной шины дешифратора 21.

Выходная шина дешифратора 21 возбуждается, так как на входах выбранного элемента И 22 = i матрицы присутствуют два сигнала — один с распределителя 7, другой - с элемента И 19. .. Следовательно, весь процесс декодирования и дешифрирования зани-мает (n- K+N) тактов, плюс К тактов на прием информационной части. В итоге на обработку всей информации тратится (и+И) тактов работы устройства.

При приеме кодовой комбинации с ошибкой принятые и вычисленные проверочные символы не совпадают, и элемент сравнения выдает сигнал защитного отказа, по которому происходит сброс всех триггеров в исходное состояние и формируется запрос по обратному каналу системы.

На чертеже приведена схема декодера, выполненного для циклического кода (7,3) с проверочным полиномом

n(x) = 1+x +x-. Связи в регистре сдвига соответствуют виду этого полинома.

Многовходовый элемент И 25 настроен на опорную кодовую комбинацию — 010-. Регистр 11 сдвига генерирует кодовое множество (см.таблицу).

15

25

2 011 6

5 45

3 . 001

4 100 4

010

101

110

Работа устройства (фиг.2) поясняется временными диаграммами, где для примера выбран случай правильного приема кодовой комбинации100101, в которой первые три символа являются информационными, а последующие — проверочными.

Такты работы устройства обозначены на временной диаграмме генератора импульсов.

3а первые три такта происходит прием информационных символов в ре55

Состояние Код Номера комбирегистра наций в кольце

1 111 0 гистр сдвига, а за последующие дегчть тактов — сдвиг принятой информации до опорной комбинации.

Таким образом, за 12 тактов работы устройства информация декодируется и дешифрируется.

Формула изобретения

Декодер, содержащий последовательно соединенные синхронизатор, первым входом подключенный к входной шине, распределитель и дешифратор, регистр, выполненный в виде последовательно соединенных первого элемента И, первого, второго и третьего триггеров, первого сумматора по модулю два и второго элемента И, многовходовой элемент И, третий элемент И, элемент ИЛИ, вход которого соединен с выходами распределителя, а выход.— с синхронизирующими входами триггеров регистра, нулевые выходы первого и третьего триггеров, а также единичный выход второго триггера регистра соединены с соответствующими входами многовходового элемента И,выходом подключенного к первому входу третьего элемента И,выход второго элемента И соединен с выходом первого элемента И,выход второго триггера регистра подключен к одному из входов первого сумматора по модулю два, выход дешифратора.является выходом устройства, отличающийся тем, что, с целью упрощения декодера, он содержит элемент сравнения, выполненный в виде последовательно соединенных четвертого элемента И, второго сумматора по глодулю два и пятого элемента И, два управляющих триггера, причем первый вход первого управляющего триггера соединен с одним из выходов распределителя,другой вход - с первым выходом синхронизатора, а первый и второй выходы— .с первым входом первого элемента И и с обьединенныгли первыми входами второго, четвертого и пятого элементов И соответственно, выход последнего соединен с вторым входом синхронизатора, третий вход которого подключен к выходу третьего элемента И и к cooTветствующим входам дешифратора, один из входов второго сумматора по модулю два подключен к выходу первого триггера регистра, второй выход синхронизатора соединен с вторыми входами первого и четвертого элементов .И, вход второго управляющего триггера соединен с одним из выходов распределителя, выход триггера подключен к одному из входов третьего элемента И.

Источники информации, принятые во внимание при экспертизе

1. Шляпоберский B.È. Основы техники, передачи дискретных сообщений. М., "Связь", 1973, с. 142.

2. Авторское свидетельство СССР г.. 263994, кл. G 06. F 5/00, 1969.

896614 !

7ф

7J . ° 7 д

fu4

1uf

У1

1f

fZ

111

Составитель В. Баганов

Редактор Е. Папп Техред T. Маточка Корректор О. Билак т

Заказ 11699/37 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. ужгород, ул.,Проектная,4