Двухнаправленный преобразователь табличных кодов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ (ii} 896615

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (5!)ФА. Кл. (22) Заявлено 11.02.80 (24) 2913506/18-24 с присоединением заявки Но (23) Приоритет

Опубликована 070182 Бюллетень NB 1

Дата опубликования описания 07. 01.82

Государственный комитет

СССР по делам изобретений я открытий

G 06 F 5/02 (53) УДК 681. 325

- (088.8) г

ЗьИОтФФ р; Я

В.Ф. Евдокимов, M.À. Шевченко, P.Þ. Мор зовсяьй

A.È. Стасюк, Ю.A. Плющ и H.Þ. Пивень %

TF ХНЫ .! АЫАЯ (72) Авторы изобретения

6Н фк т .„е, i

Институт электродинамики АН Украинской CCP (71) Заявитель (54) ДВУНАПРАВЛЕННЫИ ПРЕОБРАЗОВАТЕЛЬ ТАБЛИЧНЫХ

КОДОВ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей для стыковки вычисли5 тельных MBLIHH различных систем.

Известно устройство для преобразования табличных кодов, содержащее первый логический блок, второй логический блок, генератор импульсов,кодирующее устройство. Известное устройство предназначено для преобразования кода буквы или цифры, сформированного в виде двоичных разрядов заранее определенного первого вида, в код буквы или цифры заранее определенного второго вида и наоборот.

В известном устройстве первый логический блок решает, к какому коду относится код первого вида — к буквенному или цифровому, второй логический блок решает обратную задачу,, т.е. определяет, какой код, цифровой или буквенный, представлен кодом второго вида, генератор выходных импульсов выдает первый или второй управляющий сигнал в зависимости от выходных сигналов первого и второго логических блоков, кодирующее устройство при приеме первого управляющего сигнала преобразует код первого ЗО вида в код второго вида, а при приеме второго управляющсго сигнала осуществляет обратное преобразование(1).

Недостатки устройства состоят в невозможности осуществления преобразования машинных кодов без уплотнения информации, а также в отсутствии обратимости.

Наиболее близким к предлагаемому по технической сущности является двунаправленный преобразователь табличных кодов, содержащий первый дешифратор и блок памяти, а также два входных и два выходных регистра,буферные регистры и блоки управления приемом и выдачей j2 ). Недостаток известного устройства заключается в его относительной слож. ности, связанной с тем, что блок памяти должен хранить эквиваленты для прямого и обратного преобразования.

Целью изобретения является упрощение преобразователя.

Поставленная цель достигается тем, что двунаправленный преобразователь табличных кодов, содержащий первый дешифратор и блок памяти, дополнительно содержит второй дешифратор, группу элементов ИЛИ и обрати896615 мый сумматор по модулю два, первая и вторая группы информационных вводов которого соединены с группами входов первого и второго дешифраторов соответственно и с первыми и вторыми группами вводов преобразователя соответственно, а группа входов обратимого сумматора по модулю два соединена с группой выходов блока памяти, входы которого соединены с выходами элементов ИЛИ группы, перб вые и вторые входы которых соединены соответственно с группами выходов первого и второго дешифраторов.

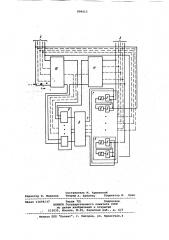

Блок-схема двунаправленного преобразователя кодов приведена на чертеже. 15

Преобразователь кодов содержит обратимый сумматор 1 по модулю два с двумя одинаковыми совершенно равноправными группами 2 и 3 вводов.

Обратимый сумматор по модулю два мо-, 20 жет быть выполнен различным образом f3).

Обратимый сумматор по модулю два содержит одноразрядные обратимые сумматоры 4 по модулю два по коли- 25 честву разрядов кодов (в данном случае восемь), каждый из которых, в свою очередь, содержит по два однонаправленных сумматора 5 по модулю пва, выход каждого из которых через элемент 6 задержки соединен с другим.

Обратимый сумматор 1 по модулю два содержит также одну однонаправленную группу 7 вводов, соединенную с блоком 8 памяти, выходы которого

35 соединены с группой 9 элементов ИЛИ.

Равноправные группы 2 и 3 вводов соединены соответственно с однонаправленными группами входов дешифраторов 10 и 11, которые преобразуют коды символов в пространственный код, 40 где каждому символу соответствует свой полюс. Выходы блоков 10 и 11, соответствующие попарно одноименным символам, соединены с соответствую-. щими входами элементов ИЛИ группы 9. 4

Преобразователь кодов работает следующим образом.

Предварительно определяется сумма по модулю два двух заранее определенных видов, сформированных из двоичных разрядов кодов одних и тех же символов. Далее преобразование кодов сводится к суммированию по модулю два полученной суммы с кодом первого вида при прямом преобразовании и полученной суммы с кодом второго вида при обратном преобразовании.

Работу устройства иллюстрирует пример преобразования кодов КОИ-8 и

ГОСТ 10859-64, которые используются в машинах серий ЕС и Минск-32 соот- 40 ветственно:

Код символа А в КОИ-8 Хд = 01000001

Код символа А в, ГОСТ 10859-.64 Y„

00100000

Сумма по модулю два 2„ = Хд + Y> .

2д, = 01100001

Код ХА поступает поразрядно на группу 2 вводов. На выходе дешифратора 10 появляется единица на полюсе, соответствующем символу A (при этом на остальных полюсах нули),ко» торая через элемент ИЛИ группы 9 поступает на вход блока 8 памяти,на выходе которого появляется код, соответствующий сумме по модулю два

X A u YA Z A Z A поразрядно поступает на группу вводов обратимого сумматора 1 по модулю два, на вторую группу вводов которого поразрядно поступает код XA. После окончания переходного процесса на группе 3 вводов получается код

YA = XA Q ZA или YA 01000001Q+01100001=00100000.

Этот код, поступая на вход дешифратора 11, преобразуется в единицу на выходе, соответствующем символу

А, которая поступает на тот же элемент ИЛИ, что и единица, соответствующая символу Д с дешифратора

10, что не меняет состояния элемента ИЛИ. Таким образом, осуществляется преобразование кода символа А из кода КОИ-8 в код ГОСТ 10859-54.

Аналогично осуществляется преобразование кодов, соответствующих дру- гим символам.

При необходимости осуществления преобразования из кода ГОСТ 10859-64 в код КОИ-8 информация подается на группу 3 вводов. Например, при поступлении кода УА на группу 3 вводов на выходе дешифратора 11, соответствующем символу А, появляется единица, которая поступает через элемент ИЛИ группы 9 на вход блока

8 памяти, на остальных входах которого нули и на группе 7 вводов которого появляется двоичный код 2Д.

Обратимый сумматор 1 суммирует по модулю два двоичные коды, т.е.

ХД У ® ZA

XA-OO1OnOOO е O11OOOO1=O1OOOOO1.

Функционирование дешифраторов

10 и 11 для преобразования кодов

КОИ-8 и ГОСТ 1058-64 приведечо в табл. 1 и 2 соответственно. Содержимое блока 8 памяти приведено в табл.3.

Таблицы приведены для четырех символов из существунщих 44,которые являются общими для машин серий ЕС и Минск-32.

При соответствующем построении дешифратора 10 и 11 и блока 8 памяти преобразователь осуществляет другие, преобразования кодов.

896615

Преобразователь кодов реализует

А А А

При задании кода Х на соответствующих вводах образуется код Y,а прн

Таблица 1

Входы

i Выходы

Х Х Х Х Х Х6 Х Х8 А 8 1 2

О 1 0 0 О О О 1 1 О О О

О 1 О О 0 О 1 О О 1 О О

О О 1 1 О О О 1 О О 1 О

0 О 1 1 0 О 1 О 0 О О 1

Таблица 2

Входы

i Выходы

У4 У2 YЪ У4 чь У6 Yт Yв А в 1 2

0 О 1 О

О 0 0 О 1 0 О О О 0 1 О . О О 1 О О 1 О О

0. 0 О 1 О 0 1 0

1 О 0 0

О О О О 1 0 О О О 1

О О

Таблица 3

Входы Выходы

А В 1 2 . Z< 2z 13 24 2 Еg 27 Еg

О О 1 1 0 О 0 О 1

1 О О

0 1 0 0 О 1 1 О 0 0 О 0

О О 1

0 О 0

0 О О

О О О

О О 1 1 О О

1 О 1 1 О О

Формула изобретения

Двунаправленный преобразователь табличных кодов, содержащий первый дешифратор и блок памяти; о т л ич а ю щ и и с .я тем, что, с целью упрощения преобразователя, он содержит второй дешифратор, группу элементов ИЛИ и обратимый сумматор по модулю два, первая и вторая группы информационных вводов которого соединены с группами входов первого и второго дешифраторов соответственно и с первыми и вторыми. группами вводов преобразователя соответственно, а группа входов обратимого суье атора задании Y на соответствующих вводах образуется Х, т.е. преобразователь осуществляет прямое и обратное преобразование кодов. по модулю два соединена с группой выходов блока памяти, входы которого соединены с выходами элементов ИЛИ группы, первые и вторые входы которых соединены соответственно с группами выходов первого и второго дешифраторов.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии В 49-47969, 60 кл 97(7) E 21, 1974..

2. Патент; Сщй М 3461432, кл, 340-172. 5, опублик. 1966.

3. Авторское свидетельство СССР по заявке 9 2461912/18-24, ф5 кл. G 06 F 7/50 1977

Составитель М. Аршавский

Редактор И. Михеева Техред A. Бабинец Корректор М. Помо

Закаэ 11699/37 Тираж 731 Подписное.

ВНИИПИ Государственного, комитета СССР

: по делам .иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. ужгород, ул. Проектная,4