Устройство для вычисления экспоненциальной функции

Иллюстрации

Показать всеРеферат

Союз Советсник

Социалистическик

Республик

ОПИСАНИЕ,щ

ИЗОБРЕТЕНИЯ (61) Дополнительное к авт. сеид-ау (22) Заявленс 29. 04 ° 80 (21) 2918682/18-24 (51)м с присоединением заявкм М— (23) Приоритет

G F 7/544

Государственный комитет

СССР ио делам изобретений н открытий

Опубликовано 070182 Бюллетень М 1

Дата опубликования описания 07. 01. 82 (53) УДК 681. 3 (088.8) (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭКСПОНЕНЦИАЛЬНОЙ

ФУНКЦИИ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных устройствах и устройствах дискретной автоматики для вычисления экспоненциальной функции у = е

Известно устройство для вычисления экспоненциальной функции,содержащее накопительные регистры, выходы которых соединены со своими входами через соответствующие однородные сумматоры-вычитатели,блок управления, блок памяти, блок определения знака псевдочастотного,блок повторения итераций, блок. сброса, блок анализа сходимости и вентили11).

Недостатком такого устройства для вычисления экспоненциальной функции

I является сложность его реализации.

Наиболее близким к предлагаемому .является устройство для вычисления экспоненциальной функции, содержащее два регистра сдвига, сумматор, первый выход которого соединен через первый регистр сдвига с его первым входом, первый триггер, вход установки и прямой выход которого соединены соответственно со входной шиной устройства и с первым входом первого элемента И, выход которого соединен со вторым входом сумматора, второй выход которого соединен с первым входом второго элемента И, второй вход которого соединен со входом сброса первого триггера и с шиной сброса устройства (2 1.

Недостаток известного устройства заключается в сложности его реализации.

Цель изобретения — упрощение устройства для вычисления экспоненциальной зависимости.

Поставленная цель достигается тем, что в устройство, содержащее два регистра сдвига, сумматор, первый триггер и два элемента И, причем первый выход сумматора через первый регистр сдвига подключен к первому входу сумматора, второй вход которого

2О соединен с выходом первого элемента И, первый вход которого соединен с прямым выходом первого триггера, вход сброса которого является входом сброса устройства и первым входом второго элемента И, второй вход которого соединен со вторым выходом сумматора, установленный вход первого триггера соединен с информационным входом устройства, введены второй триггер, третий элемент И, 896619

Такое техническое решение уст- ° ройства для вычисления экспоненциальной функции позволяет по сравнению с известным исключить из состава устройства второй сумматор и счетчик.

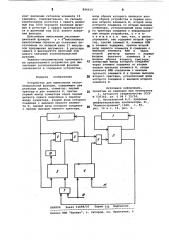

На чертеже изображена структурная схема устройства для вычисления экспоненциальной функции.

Устройство для вычисления экспонейциальной функции содержит два регистра 1 и 2, сдвига, сумматор 3, два триггера 4 и 5, три элемента И

6, 7 и 8, элемент ИЛИ 9, элемент 10 задержки, вход 11 устройства и вход

12 сброса.

Устройство для вычисления экспоненциальной функции работает следующим образом.

В исходном состоянии регистр 1 сдвига очищен, триггеры 4 и 5 находятся. в нулевом состоянии. На вход

12 сброса поступает " последовательность импульсов частоты f/n, где частота тактовых импульсов; n - количество разрядов регистров 1 и 2 сдвига.

В регистр 2 сдвига записывается двоичный код начального значения функции у е ",На вход 11 устройства подается последовательность импульсов, представляющая собой поток приращений аргумента.

Первый входной импульс, поступающий по входу 11, устанавливает триггер 4 в единичное состояние, в котором сигнал его прямого выхода открывает элемент И 6, подключая второй вход сумматора 3 к выходу элемента ИЛИ 9. Двоичный код начального значения функции сдвигается с выхода регистра 2 через элемент И 8, открытый сигналом инверсного выхода триггера 5, элемент ИЛИ 9 и элемент

И 6 на второй вход сумматора 3, на первом выходе которого формируется последовательный двоичный код суммы, сдвигаемый в регистр 1, начиная с младших разрядов.

Двоичный код начального значения функции сдвигается с выхода регистра

2 на его вход без изменения через элементы И 8, ИЛИ 9 при нулевом состоянии триггера 5. элемент ИЛИ и элемент задержки,причем второй вход первого элемента И соединен с выходом элемента ИЛИ и через второй регистр сдвига с первым входом третьего элемента И и входом сброса второго триггера,инверсный выход которого соединен через элемент задержки со вторым входом третьего элемента И, входы элемента ИЛИ соединены с выходом третьего элемента И и прямым выходом второго триггера, установочный вход которого соединен с выходом второго элемента И.

$0

5S

Спустя и тактов триггер 4 сбрасывается в нулевое состояние, в котором сигнал прямого выхода триггера 4 закрывает элемент И 6 °

Второй входной импульс, поступающий ко входу 11, вновь устанавливает триггер 4 в единичное состояние, в котором сигнал его прямого выхода открывает элемент И б.

В этом случае на первый вход сумматора 3 с выхода регистра 1 сдвинутый, начиная с младших разрядов,дво1 ичный код суммы предыдущего шага вы-1 чнслений, а на второй вход сумматора

3 с выхода элемента ИЛИ 9 через элемент И б поступает двоичный код текущего значения функции.

В результате суммирования, выполняемого сумматором 3, может произойти переполнение регистра 1 сдвига,в который записывается только и разрядов суммы, а сигнал переполнения в виде переноса из n""ro разряда поступает со второго выхода сумматора

3 через элемент И 7 на вход триггера 5, устанавливая его в единичное состояние.

В единичном состоянии триггер 5. находится до появления с выхода регистра 2 первой, начиная с младшего разряда, единицы двоичного кода текущего значения функции. Если с выхода регистра 2 сдвига в младших разрядах появляются нулевые сигналы, то на вход регистра 2 сдвига и второй вход элемента И б поступают через элемент ИЛИ 7 единичные сигналы прямого выхода триггера 5. Сигнал первой единицы двоичного кода текущего значения функции, действующий на выходе регистра 2 сдвига, сбрасывает триггер 5 в нулевое состояние, в котором на его прямом выходе устанавливается нулевой .сигнал.

Элемент 10 задержки обеспечивает стирание первой единицы двоичного кода текущего значения функции,так как поддерживает нулевой сигнал предыдущего состояния триггера 5 на втором входе элемента И 8, который остается в закрытом состоянии до окончания действия сигнала первой единицы на выходе регистра 2 сдвига.

Таким образом, двоичный код текущего значения функции в регистре сдвига 2 уменьшается на единицу младшего разряда по сигналу переполнения регистра 1 сдвига. Например, если в регистре сдвига 2 был код 1000, то по сигналу переполнения регистра 1 сдвига, который устанавливает триггер 5 в единичное состояние, в трех младших разрядах регистра сдвига.2 записываются единичные сигналы прямого выхода триггера

5, действующие через элемент ИЛИ 9 на входе регистра сдвига 2, а единичный сигнал четвертого разряда стирается элементом И 8, который за896619

Формула изобретения

ВНИИПИ Заказ 11699/37 Тираж 731 Подписное, Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 крыт выходным сигналом элемента 10 задержки. Следовательно, по сигналу переполнения регистра 1 сдвига двоичный код 1000 текущего значения функции в регистре 2 сдвига преобразуется в двоичный код 0111 нового значения функции.

Дальнейшие вычисления экспоненциальной функции у е выполняются аналогичным образом до окончания поступления по вхбдной шине 11 импульсов приращения аргумента. В регистре сдвига 2 фиксируется двоичный код

;нового значения экспоненциальной функции..

Технико-экономические преимущества предлагаемого устройства для вы» числения экспоненциальной функции заключаются в упрощении устройства.

Устройство для вычисления экспоненциальной функции, содержащее два регистра сдвига, сумматор, первый триггер и два элемента И, причем первый выход сумматора через первый регистр сдвига подключен к первому входу сумматора, второй вход которого соединен с выходом первого элемента И, первый вход которого соединен с прямым выходом первого триггера, вход сброса которого является входом сброса устройства и первым входом второго элемента И, второй вход которого соединен со вторым выходом сумматора, установленный вход первого триггера соединен с информационным входом устройства, о т л ич а ю щ е е с я тем, что, с целью упрощения, оно содержит второй триггер, третий элемент И, элемент ИЛИ и элемент задержки, причем второй вход первого элемента И соединен с выходом элемента ИЛИ и через второй регистр сдвига с первым, входом третьего элемента И и входом сброса второго триггера, tS инверсный выход которого соединен через элемент задержки со вторым входом третьего элемента И, входы элемента ИЛИ соединены с выходом третьего элемента И и прямым выходом

Я9 второго триггера, установочный вход которого соединен с выходом второго элемента И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 538366, кл. С 06 F 15/34.

2. Неслуховский К.С. Цифровые дифференциальные анализаторы. М., 30 "Машиностроение", 1968, с. 85, рис. 16 и с. 14, рис. 4.