Цифровой экстраполятор

Иллюстрации

Показать всеРеферат

Союз Советснин

Социалистических

Республик

О П И С A H M K < i896632

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, санд-ву ($1) N. Кл. (22) Зая влено 23.04.80 (21) 2916931/18-24 с присоединением заявки ¹

G 06 F 15/353 1веуааретеенный квинтет

СССР

ao aNIaM нзабретеннй и еткрытнй (23) Приоритет

Опубликовано №01.82. Бюллетень № 1

Дата опубликования описания 07.01.82 (53) УДК 6813 (088.8) (72) Авторы изобретения

Ис. Ф. Тихонов, В. В. Тошев и А. Д. всесиии, Военный инженерный Краснознаменный йнститут . нм .о A,:,,4 ..3 Ü4ôñêoãî

" "":Ж (7I) Заявитель

С с (54) ЦИФРОВОЙ ЭКСТРАПОЛЯТОР

Изобретение относится к вычислительной технике и может быть использовано в цифро вых системах автоматического управления.

Известен экстраполятор первого порядка, заполняющий промежутки времени между кодовыми посылками функцией времени, меняющейся по линейному закону, содержащий регистры памяти, сумматоры и счетчики (11.

Недостаток такого устройства — низкая точность экстраполяции.

Наиболее близким к предлагаемому является цифровой экстраполятор, содержащий .регистр памяти, параллельный сумматор, преобразователь код-частота, реверсивный счетчик и элемент И 12).

Недостаток известного цифрового экстраполятора — не учитывается информация на предпоследнем шаге экстраполяции, поэтому точность экстраполяции невысока.

Цель изобретения — повышение точности экстраполяции.

Поставленная цель достигается тем, что в цифровой экстраполятор, содержащий первый регистр, первый элемент И, первый параллельный сумматор, преобразователь код-частота и реверсивный счетчик, причем вход первого регистра и вход текущего значения реверсивного счетчика подключенъ| к информационному входу экстраполятора, выход первого регистра подключен к первому входу элемента

И. второй вход которого подкл|очен к тактовому входу экстраполятора, первый и второй выходы первого параллельного сумматора подключены к вычитающему и суммирующему входам реверсивного счетчика соответственно, третий выход первого параллельного сумматора подключен к входу преобразователя код-частота, выход которого подключен к счетному входу реверсивного счетчика, выход коIS торого является выходом экстраполятора, введены два параллельных сумматора, второй регистр и второй элемент И, при этом первый вход второго параллелъного сумматора под20 ключен к выходу первого элемента И, второй вход второго параллельного сумматора под ключен к информационному входу экстраполятора, выход второго параллельного сумматора подключен к входу второго регистра, к пер896632

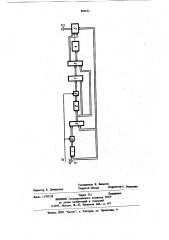

1О вому входу первого параллельного сумматора и к первому входу третьего параллельного сумматора, выход второго регистра подключен к первому входу второго элемента И, второй вход которого подключен к тактовому входу экстраполятора, выход второго элемента И подключен к второму входу третьего параллельного сумматора, выход которого подключен к второму входу первого параллельного сумматора. На чертеже представлена блок-схема цифрового экстраполятора.

Цифровой экстраполятор содержит первый регистр 1, первый элемент И 2, первый парал лельный сумматор 3, преобразователь 4 кодчастота, реверсивный счетчик- 5, второй па.раллельный сумматор 6, третий параллельный сумматор 7, второй регистр 8, второй эле-, мент И 9, тактовый вход 10 экстраполятора, информационный вход 11 экстраполятора, выход 12 экстраполятора.

Цифровой экстраполятор работает следующим образом.

Перед поступлением текущего значения входного кода (и), его предшествующее значение XPe- ) по тактовому импульсу переписывается во второй параллельный сумматор

6, а реверсивный счетчик 5 обнуляется. После этого текущее значение кода х E 5g записывается в первый регистр 1, в ревефсивный . счетчик 5 и подается на второй вход второго параллельного сумматора 6, в котором вычисляется первая конечная разность

q Ê ь)= Xt3- Xt. -"3

Код разности, полученный во втором параллельном сумматоре 6, поступает во второй регистр 8, на первый вход первого параллельного сумматора 3 и на первый вход третьего параллельного сумматора 7, в котором уже находится код 9 N jn- Я х fn-ß -х(@-1), полученный в предыдущем цикле работы экстраполятора д ао тактовому импульсу переписанный иэ второго регистра 8 через второй элемент

И 9. С выхода третьего параллельного сумматора 7 выжсленная вторая разность q М п1

"- q N t NJ - 9 М g т -11 поступает на второй вход первого параллельного сумматова 3, где вычисляется сумма 911hn3 =m÷М ь ч1Ж 3, которая с помощью преобразователя 4 кодчастота преобразуется в частоту следования импульсов. Выходная частота преобразователя

4 код-частота равна. = %, ° q%t ng, где F — опорная частота; Я вЂ” разрядность кода.

Частота с выхода преобразователя 4 кодчастота подается на вход реверсивного счет1S

И

3S

S0

4 чика 5, управляюшне входы которого подключены к выходам знакового разряда первого параллельного сумматора 3. В зависимости от знака кода ч 8 3 реверсивный счетчик 5 производит суммирование или вычитание поступающих на вход счетчика импульсов.

Изобретение позволяет увеличить точность экстранолятора.

Формула изобретения

Цифровой экстраполятор, содержащий пер вый регистр, первый элемент И, первый параллельный сумматор, преобразователь код-частота и реверсивный счетчик, причем вход первого регистра и вход текущего значения реверсивного счетчика подключены к информационному входу экстраполятора, выход первого регистра подключен к первому входу элемента И, второй вход которого подключен к тактовому входу экстраполятора, первый и второй выходы первого параллель- ° ного сумматора подключены к вычитающему и суммирующему входам реверсивного счетчика соответственно, третий выход первого параллельного сумматора подключен к входу преобразователя код-частота, выход которого подключен к счетному входу реверсивного счетчика, выход которого является выходом экстраполятора, отличающийся тем, что, с целью повышения точности экстраполяции, в него введены два параллельных сумматора, второй регистр и второй элемент

И, при этом первый вход второго параллельного сумматора подключен к выходу первого элемента И, второй вход второго яараллельного сумматора подключен к информационному входу экстраполятора, выход второго параллельного сумматора подключен к входу второго регистра, к первому входу первого параллельного сумматора и к первому входу третьего параллельного сумматора, выход второго регистра подключен к первому входу второго элемента И, второй вход которого подключен к тактовому входу экстраполятора, выход второго элемента И подключен к второму входу третьего параллельного сумматора, выход которого подключен к второму входу первого параллельного сумматора.

Источники информации, принятые во внимание при экспертизе

1. Бесекерский В, А. Динамический синтез автоматического регулирования. М., "Наука", 1979.

2. Авторское свидетельство СССР М 694865, кл. 6 06 F 15/20, 1979 (прототип).

896632

Составитель В Вальков

Техред Л. Пекарь Корректор Г. Раактиик

Редактор Е. Дичинская

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Зк 11707/38 Тираж 731: Подписное

ВНИИПИ Государственного комитета СССР по делам наобретений и открытий

113035, Москва, Ж-35, РауШская наб., д. 4/5