Статистический анализатор

Иллюстрации

Показать всеРеферат

Союз Советскиа

Социалмстическми

Республик

ОП ИСДНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<»>896642 (6I ) Дополнительное к авт. саид-ву (22) Заявлено 24.04.80 (23 ) 29! 6940/38-24 с присоединением заявки >чЪ (23) Приоритет (51)>М. Кл.

G 06 G 7/52

Гннуднрстненньй квинтет

СССР ан дннэи нзэбрнтнннн к нткрмтнй

Опубликовано 07.0l.82. бюллетень М 1

Дата опубликования описания 07.01.82 (53) УДК 68!;3 (088.8) (72) Авторы изобретения

В. В. Заходяченко, В. Е. Тырса и А. И

I !

Харьковский автомобильно-дорожный инстит ..К нисомола У райны (71) Заявитель (54) СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для оперативного анализа случайных процессов, а именно для построения плотности распределения максимуS ма и соответствующих им минимумов с разными коэффициентами асимметрии.

Известно устройство для определения плотности вероятностей экстремальных значений случайного процесса, содержащее квантователь входного сигнала, многовходовой блок совпадений, связанный с выходами квантователя, к которым подключены также блок управления, соединенный двумя выходами с управляющим входом блока совпадения, подключенного к блоку регистрирующих счетчиков, и позволяющее определять плотность вероятностей экстремальных значений случайного процесса (1) .

Недостаток этого устройства заключается в том, что по содержимому счетчиков блока памяти нельзя судить о распределении по уровням квантования отдельно как максимумов, так и минимумов, так как содержимое одноro счетчика показывает суммарное количество экстремумов на соответствующем уровне.

Наиболее близким по технической сущности к изобретению является устройство для получения полусумм и полуразностей экстремальных значений случайного процесса, содержащее группу параллельно подключенных ко входу анализатора пороговых устройств, выход каждого из которых соединен со входом двух дифференцирующих усилителей, выходы нечетных силителей подключены ко входам первого элемента ИЛИ, а выходы четных усилителей .— ко входам второго элемента ИЛИ, выходы обоих элементов ИЛИ через первый и второй элемент задержки соответственно соединены с соответствующими входами триг гера управления, первый выход которого подключен к первым входам четных элементов

И группы, а второй выход триггера соединен с первыми входами нечетных элементов И группы, второй вход каждого элемента И груапы подключен к выходу соответствующего дифференцирующего усилителя, группу триггеров, выходы которых соединены с соответ896642

3 ствующим входом дешифратора, каждый выход которого через соответствующий формирователь импульсов подключен ко входу счетчика, первые входы триггеров группы кроме первого и последнего триггера группы соединены с выходом соответствующего элемента ИЛИ, цри этом первые входы первого и последнего триггера группы соединены непосредственно с выходом первого и последнего элемента И группы, ко входам

j-го (i = 2, ..., n — 1) элемента ИЛИ группы подключены выход 2i-го четного элемента И предыдущего канала и выход (2i+1)-го нечетного элемента И последующего канала (2l

Это устройство позволяет определить количество максимумов и соответствующих им минимумов с разными коэффициентами асимметрии.

Недостатки данного устройства — низкая надежность и ограниченность частотного диапазона исследуемых процессов, что объясняется следующими причинами.

Подключение элемента ИЛИ к выходам дешифратора определяет количество входов элемента ИЛИ, равное n(n+1) 2 (количество комбинаций максимумов и минимумов при п уровнях квантования), что ведет к значительному увеличению числа логических связей, ус ложнеиию устройства и снижению его надежности.

Отсутствие задержки на поступление сигнала сброса трип еров с выхода элемента ИЛИ может привести к сбоям в работе устройства, что также снижает надежность работы устройства.

Кроме этого, .время задержки сигнала элементами задержки на входе триггера управления определяется верхней частотой исследуемого процесса, что снижает его быстродействие и ограничивает частотный диапазон исследу емых процессов, если заранее неизвестны частотные характеристики входного сигнала.

Цель изобретения — повышение надежности анализатора за счет его упрощения.

Указанная цель достигается тем, что вторые входы триггеров группы соединены с выходом первого элемента задержки.

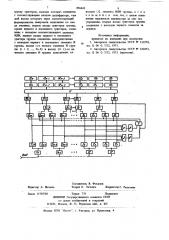

На чертеже приведена структурная схема статического анализатора.

Анализатор содержит группу из пороговых устройств 1,группу из 2п дифференцирующих усилителей 2, элементы ИЛИ 3 и 4, элементы 5 и 6 задержки, триггер 7 управления, группу из 20 элементов И 8, группу из (п — 1) элементов ИЛИ 9, группу из (n+1) триггеров 10, дешифратор 11, группу формирователей 12 импульсов и счетчиков 13.

Статический анализатор работает следующим образом.

Входной сигнал подается на пороговые устройства 1, число которых определяется необходимой точностью обработки. Пороговые устройства разбивают весь диапазон изменения входного сигнала на уровни дискриминации.

При увеличении входного сигнала на выходе пороговых устройств появляется положительный перепад напряжения, а при уменьшении— отрицательный.

Сигнал с выхода пороговых устройств подается на дифференцирующие усилители 2, которые дифференцируют, усиливают однополяриые импульсы по переднему и заднему фронту перепадов напряжения с выхода пороговых устройств. Причем, усилители с нечетными номерами формируют импульсы по переднему фронту перепадов, а усилители с четными номерами — по заднему фронту, 20

Импульсы с выходов нечетных усилителей через элемент ИЛИ 3 и элемент 6 задержки . поступают на единичный вход триггера 7 управления, а импульсы с выхода четных усилителей через элемент ИЛИ 4 и элемент Sз:.а25 держки, поступают на нулевой вход триггера

7 управления.

Элементы задержки предназначены для четкого срабатывания логики устройства и устранения сбоев при записи импульсов в счетчики. 13 и сброса триггеров 10 логики. Время задержки равно сумме времени срабатывания триггера логики, дешифратора, формирователя, счетчика (о@= "тг ди " "сч )

Таким образом, время задержки определяется не верхней частотой исследуемого процесса, а быстродействием элементов анализатора, что позволяет использовать анализатор для нсследования случайных процессов в широком диапазоне частот.

Единичныи выход триггера 7 управления соединен с первыми входами четных элементов И 8,. а нулевой выход — с первыми входами нечетных элементов И 8.

Элементы ИЛИ 9 собирают импульсы, соответствующие экстремальным значениям случайного процесса в пределах каждого иэ интервалов дискриминации.

Триггеры 10 и дешифратор 11 обеспечивают попарное совпадение максимума и последовавшего за ним минимума и последующее попадание импульса, соответствующего этому совпадению через формирователь 12 в соответствующий счетчик 13.

После записи импульса в счетчик происходит сброс триггеров 10 в исходное состояние импульсом, поступившим с выхода первого элемента ИЛИ 3 через элемент 6 задержки иа нулевые установочные входы триггеров 10

6642 6

Статистический анализатор, содержащий группу параллельно подключенных ко входу анализатора пороговых устройств, выход каждого из которых соединен со входом двух дифференцируюших усилителей, выходы нечетных усилителей подключены ко входам первого элемента ИЛИ, а выходы четных усилителей — ко входам второго элемента ИЛИ, выходы первого и второго элементов ИЛИ че45

S0 рез первый и второй элемент задержки соответственно соединены с соответствующими входами триггера управления, первый выход которого подключен к первым входам четных элементов И группы, а второй выход тригге55 ра соединен с первыми входами нечетных элементов И группы, второй вход каждого эле, мента И группы подключен к выходу соот ветствуюшего дифференцирующего усилителя, 5 89

Когда триггеры 10 находятся в исходном нулевом состоянии, а триггер 7 — в единичном, тогда на входы четных и нечетных элементов И 8 подается запрещающий потенциал.

С увеличением входного сигнала срабатывают пороговые устройства и на входы днфференцирующих усилителей подаются положительные перепады напряжения. В результате с выходов соответствующих нечетных усилителей поступают импульсы на вторые входы нечетных элементов И 8 (на первые входы которых подан запрещаюший потенциал с нулевого выхода триггера7 управления) и через элемент ИЛИ 3 и элемент 6 задержки на единичный вход триггера 7 и на нулевые входы триггеров 10.

Эти импульсы не меняют состояние триггера 7 и триггеров 10.

Прн уменьшении входного сигнала (наличие максимума на одном из уровней) с выхода порогового устройства этого уровня отрицательный перепад напряжения после дифференцирования и усиления четным усилителем этого уровня поступает на второй вход соответствующего элемента И 8, на первый вход которого подан разрешающий потенциал с единичного выхода триггера 7, и. проходит через соответствующий элемент ИЛИ 9 на единичный вход соответствующего триггера 10. Триггер 10 срабатывает и подает разрешающий потенциал на соответствующий вход дешифратора 11. Кроме того, импульс с выхода четного усилителя этого уровня через элемент

ИЛИ 4 н элемент 5 задержки поступает на нулевой вход триггера 7. Через время Тзад срабатывает триггер 7, запрещая прохождение . импульсов через четные элементы И 8, если входной сигнал убывает и проходит через нижестоящие пороговые устройства.

Прн последующем нарастании входного сигнала (наличие минимума на данном или одном иэ нижестоящих уровней) срабатывает пороговое устройство этого уровня. В результате импульс с выхода нечетного усилителя этого уровня поступает через соответствующие элементы И 8 и ИЛИ 9 на единичный вход соответствующего триггера 10. Триггер 10 срабатывает и подает разрешающий потенциал на дешифратор 11. При наличии двух разрешающих потенциалов (с триггеров, зафиксировавших максимум и минимум) дешифратор вырабатывает перепад напряжения, который поступает на формирователь. При этом с выхода формирователя поступает импульс в один иэ счетчиков 13. Каждому счетчику соответствует свое значение максимума и последовавшего эа ним минимума. Кроме того, импульс с выхода нечетного усилителя уровня, на

35 котором выделен минимум, через элемент

ИЛИ 3 и элемент 6 задержки поступает иа единичный вход триггера 7 и нулевые входы триггеров 10. Через время Тзад срабатывают триггер 7, запрещая прохождение импульсов через нечетные элементы И 8, если входной сигнал и далее возрастает, и два триггера 10, которые устанавливаются в исходное нулевое состояние. Триггеры 10 сбрасываются только после записи импульса в один из счетчиков.

13, что обеспечивается выбором времени задержки, о чем говорилось выше. Таким об разом, элемент ИЛИ 3 и элемент 6 задержки совмещают в себе функции управления работой триггера 7 и сброса триггеров 10 после записи в соответствующий счетчик 13 импульса, свидетельствующего о регистрации экстремальной пары максимум-минимум. Кро; ме того, такое использование этих элементов устраняет сбой прн записи импульса в счетчик и сброса триггеров логики.

При дальнейшем увеличении входного сиг-, нала анализатор работает аналогично.

Применение предлагаемого изобретения позволяет совместить несколько функций управления работой анализатора и упрощает его, что приводит к повышению надежности работы.

Использование элемента задержки совместно с элементом ИЛИ в цепи сброса трнгге. ров логики позволяет избежать сбоев при сбросе триггеров логики и записи импульсов в счетчики, что также повышает надежность работы анализатора.

Кроме того, дополнительный положительный эффект от использования изобретения заключается в расширении частотного диапазона исследуемых случайных процессов. формула изобретения

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР No 312274, кл. G 06 G 7/52, 1971.

2, Авторское свидетельство СССР М 332472, кл. G 06 G 7/52, 1972 (прототип).

Составитель В, Фукалов

Техред Л. Пекарь Корректор Г, Решетник

Редактор А. Мотыль

Заказ 11707/38

Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4

7 896642 8 группу триггеров, выходы которых соединены входам i/2. элемента ИЛИ группы, о т л и с соответствующим входом дешифратора, каж ч а ю шийся тем, что, с целью повыдый выход которого через соответствующий шения надежности анализатора за счет его формирователь импульсов подключен ко вхо. упрощения, вторые входы триггеров группы ду счетчика, первые входы триггеров группы, соединены с выходом первого элемента закроме первого и последнего триггеров, соедн держки. иены с выходом соответствуюшего элемента

ИЛИ, первые входы первого и последнего триггера грутпты соединены непосредственно с выходом первого н последнего элемента И группы, выход i-го четного элемента И группы (i. 2, ..., 2n-l) и выход (i+ 1)-го нечетного элемента И группы подключены ко.