Формирователь управляющих сигналов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Совет сник

Социаписткческмк

Республик

Н 04 Х 3/02

Н 03 К 17/00 (оеударствкиный комитет (23 ) П риоритет ао делам изобретений и открытий

Опубликовано 07.0 1.82. Бюллетень М 1

Дата опубликования описания 07.01.82 (53) УЮ 625.394.. 14(088.8) (72) Автор изобретения

И. В. Мареев

t !

Г

Г

Г (71) Заявитель

Г! -Г

Г аГГ

k (54) ФОРМИРОВАТЕЛЬ УПРАВЛЯЮШИХ СИГНАЛОВ

Устройство относится к передаче и обработке информации в многоканальных цифровых системах с цикловой синхронизацией, в которых синхросигнал паредаеъ ся в виде последовательности чередующихся маркерных синхрогрупп двух видов, когда длина цикла во всех каналах одинакова, однако маркеры различных каналов смещены во времени относительно друг друга, т. е..преимущественно в многоканальных цифровых системах связи, телеизмерения, передачи изображения, а также в многоканальных цифровых магнитофонах с высокой плотностью записи, когда имеет место взаимный перекос каналов движущегося носителя записи.

Известно устройство, содержащее по следовательно соединенные первый ревер сивный счетчик, интерполятор, второй реверсивный счетчик, коммутатор и генератор (1 )

Недостатком устройства является невозможность работы с многоканальным входным потоком. Кроме того, устройство не может быть использовано для работы с входным потоком в виде после довательности откликов на маркерные синхрогруппы, так как в этом случае точность регулирования, определяемая длительностью цикла, т. е . интервалом между двумя маркерами, окажется недостаточной для подстройки символьной частоты. При этом недопустимо большим будет время подстройки частоты генера. ! О тора

Бель изобретения — повьпаение помехоустойчивости.

Для достижения цели в формирователь управляющих сигналов, содержащий последовательно соединенные первый реверсивный счетчик, интерполятор, второй реверсивный счетчик, коммутатор и генератор, введены последовательно со единенные преобразователь код-напряжэ ниа, компаратор и счетный триггер, первый выход которого через первый вход первого элемента И непосредственно, а через последовательно соединенные !

896774 формирователь установочных импульсов, делитель частоты на 2К, триггер интервала и второй вход первого элемента

И подсоединен ко входу "добавление" первого реверсивного счетчика, ко входу, вычитание которого через второй элемент И подсоединен второй выход счет. ного триггера, третий вход первого. элемента И и второй вход второго элемента

И обьединены и подключены к первому входу третьего элемента И, второй вход которого объединен с третьим входом второго элемента И и вторым выходом . триггера интервала, второй вход которого обьединен со входом делителя àî тоты на 2К, второй вход которого подключен к выходу третьего элемента И; выход генератора подсоединен ко входу делителя частоты на;К и первому входу третьего элемента И, а выходы интер» полятора через элемент ИЛИ подсоединены к дополнительному входу первого реверсивного счетчика.

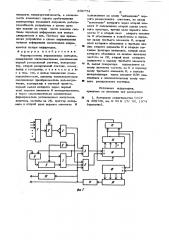

На фиг, 1 представлена структурноэлектрическая схема формирователя управляющих сигналов, на фиг, 2- — эпюры, поясняющие работу устройства.

Формирователь управляющих сигналов содержит преобразователь 1 код-напряжение, компаратор 2, счетный триггер 3 первый элемент И 4, второй элемент

И 5, формирователь 6 установочных им пульсов, триггер 7 интервала, третий элемент И 8, делитель 9 на 2К, делитель 10 на к, генератор 11, элемент

ИЛИ 12, интерполятор 13, первый реверсивный счетчик 14, второй реверсивный счетчик, 15 и коммутатор 16.

30

Структура и взаимное расположение информационных последовательностей в каналах показаны на эпюрах (фиг. 2 строки 1-4а). В каждом канале с помощью чередующихся маркеров М1 и М2 образованы циклы длиной К символов.

Хотя длина циклов во всех каналах одинакова, цикловые стробы (фиг. 2. строки 5-8Ю), соответствующие строкам 1-4g.

Устройство работает следующим обра- 40 зом.

B информационной цифровой последовательности каждого канала содержатся циклически расположенные чередующиеся маркерные синхрогруппы двух видов. Или- 4 нв информационного цикла во всех каналах одинакова, однако маркеры различйых . каналов смещены во времени друг от» носительно друга. смещень двуг относительно друга, как за счет смещения маркеров, так и изза наличия холостых" слоев, длиной и символов.

Очевиднц что нельзя использовать для управления частотой считывания цикловые стробы какого-либо одного канала, так как их длительность и положение во времени существенно изменчивы, кроме того при выходе из строя выбранного канала устройство в целом окажется неработоспособным. Поэтому для управления частотой необходимо сформировать обобщенный цикловой строб по всем каналам. Ътя этого цикловые стробы с первых входов 2 -21,1 устройства поступв.4 ют на входы преобразователя 1 код-напряжение, на выходе которого начинает нарастать напряжение (фиг. 2 строка Ос ).

Выход преобразователя 1 код-напряжение соединен с первым входом компарвтора

2, на второй вход которого подан опорный сигнал Е со второго входа устройства. Импульс на выходе компаратора 2 появляется в момент (фиг. 2, стрс ка 1ОО), когда на входы преобразовате, . ля 1 код-напряжение поступает некоторое наперед заданное число положительных цикловых стробов любых каналов и напряжение нв его выходе превышает опорный сигнал Ео . Это число предпочтительно выбирать равным половине числа каналов, так как тогда работоспособнссть устройства в целом сохраняет« ся при выходе из строя до половины каналов или потере синхронизма в них.

Импульсная последовательность с выхода компаратора 2 (фиг. 2, строки 1О или 10с1 ) поступает на вход счетного триггера 3, на выходе которого образуется в общем случае несимметричный .и непостоянный по периоду меандр (фиг. 2, строки 2О и 3О).

Несимметричность вызывается смешением маркеров в каналах от цикла к циклу, а изменения периода вызываются, например при магнитной записи, вариа циями скорости носителя записи и по явления за счет этого "холостых" слоев в цикле, Несимметричность и непостоян, ство периода выходного сигнала счетного триггера 3 являются первичными управляющими воздействиями для управления частотой считывания.

Положительным перепадом второго выхода счетного триггера 3 с помощью формирователя 6 установочных импульсов (фиг. 2, строка 4с1) триггер 7 ин896774 терввла и делитель 9 на 2К устанавливаются в начальное состояние, в резуль- тате чего открывается третий элемент

И 8 и на счетный вход делителя 9 на

2К начинают поступать импульсы символьной частоты с выхода генератора 11 (фиг. 2, строки 5о и 7с1). После этого как делитель 9 на 2К отсчитает 2К импульсов, он формирует сигнал (фиг. 2, строка 80), который перебрасывает триггер 7 интервала, который закрывает третий элемент И 8, до прихода следующего импульса с выхода формирователя 6 установочных импульсов.

При работе устройстьа возможны три случая регулирования.

1. Частота генератора 11 выше средней скорости поступления информации в схему выравнивания.

В этом случае длительность положительного строба со второго выхода счетного триггера 3 (фиг. 2, строка 35) больше длительности отрицательного строба со второго выхода триггера 7 интервала (фиг. 2, строка 60}, определяемого временем счета 2К импульсов генератора

11 в делителе 9 на 2К. Тогда через второй элемент И 5 на суммирующий вход первого реверсивного счетчика 14 поступает количество импульсов, пропорциональное разности между длительностями стробов счетного триггера 3 и триггера 7 интервала (фиг. 2, строки 104 ), Если в результате суммирования состояние первого реверсивного счетчика

14 достигает некоторого числа N > то на первом выходе интерполятора 13 появляется импульс (фиг. 2, строка 11с ), который поступает на вычитающий вход второго реверсивного счетчика 15 и уменьшает его состояние на единицу, в результате чего коммутатор 16 .уменьшает частоту генератора 11.

Одновременно импульс с первого выхода интерполятора 13, пройдя через элемент ИЛИ 12 (фиг. 2, строка 13с)) устанавливает первый реверсивныя счетчик

14 в начальное состояние, равное некоторому йср, которое выбрано междуй „-, m N g .

Qanee процесс подстройки частоты генератора 11 продолжается аналогично писанному до тех пор,, пока длительность строба триггера интервала 7 станет равной длитель ности строба счетного триггера 3.

2. Частота генератора 1 1 ниже сред ней скорости поступления информации в схему выравнивания.

В этом случае (фиг. 2, строки 2, 5, 9g) через первый элемент И 4 на вычитающий вход первого реверсивного счетчика 14 поступает количество импульсов пропорциональное разности между длительностями положительного строба первого выхода триггера 7 интервала и отрицательного строба первого выхода счетного триггера 3.

Если в результате вычитания состояние первого реверсивного счетчика 14 достигает некоторого числа 8 и н, то на втором выходе интерполятора 13 появляется импульс (фиг. 2, строки 12a), 1 который поступает на суммирующий вход второго реверсивного счетчика 15 и увеличивает его. состояние .на единицу, в результате чего коммутатор 16 увеличивает частоту генератора 11.

Одновременно импульс со второго выхода интерпопятора 13, пройдя чеоез элемент ИЛИ 12 (фиг. 2, строка 130), устанавливает первый реверсивныя счетчик

14 в начальное состояние, равное некоторому Nqp, которое выбрано между ((пт и NAQX

Палее процесс подстройки частоты генератора 11 продолжается аналогично описанному до тех пор, пока .длительность строба триггера 7 интервала станет равной длительности строба счетного триггера 3.

3. Частота генератора 11 соответствует средней скорости поступления информации в схему выравнивания.

В этом случае стробы счетного триггера 3 и триггера 7 интервала равны, поэтому первый и второй элементы И 4 и 5 закрыты для прохождения через их третьи входы. импульсов генератора 11 нв входы первого реверсивного счетчика 14.

В результате состояния первого и второго реверсивных счетчиков 14 и 15 остаются неизменными и коммутатор 16 не изменяет . частоту генератора 11, символьная частота которого поступает на первый выход устройства, а цикловая частота считывания, получаемая делением символьной в К раз на делителе 10 на К, поступает ыа второй выход устройства.

Таким образом, устройство осуществляет слежения за средней скоростъю поступления информации и через каждые четыре канальных цикла производят .подстройку частоты генератора.

Предлагаемый формирователь управляющих сигналов позволяет существенно . повысить помехоустойчивость, а возможность изменения порога срабатывания компаратора позволяет сохранить работоспособность устройства в целом даже при выходе из строя части каналов сиотемы передачи информации или потере синхронизма в них. Поэтому при применении устройства в схеме выравнивания потоков информации значительно сокращаются потери информации.

Формула изобретения

Формирователь gfù)èÂëÿþøèõ сигналову содержащий последовательно соединенные первый реверсивный счетчик, интерпопятор, второй реверсивный счетчик, комму, татар и генератор, о т л и ч а ю ш и йс я тем, что, с целью повьпнения помехоустойчивости, введены последовательно соединенные преобразователь код-нагряжение, компаратор и счетный триггер, первый выход которого через первый вход первого элемента И непосредственно, а через последовательно соединенные формирователь установочных импульсов, делитель частоты на 2К, триггер интер.вала и второй вход первого элемента И

6774 8 подсоединен ко входу добавление первого реверсивного счетчика, ко входу вычитание" которого через второй эльмент И подсоединен второй выход счеъ5 ного триггера, третий вход первого элемента И и второй вход второго элемента И объединены и подключены к первому входу третьего элемента И, второй . вход которого объединен с третьим вхо; ® дом второго элемента И и вторым выходом триггера интервала, второй вход которого объединен со входом делителя частоты на 2К, второй. вход которого подключен к выходу .третье о элемента

И, выход генератора подсоединен ко входу делителя частоть на К и первому входу третъего элемента И, а выходы интерполятора через элемент ИЛИ подсоединен к дополнительному входу перЗ® вого реверсивного счетчика.

Источники ицформацяи, принятые во внимание при экспертизе

Ж 2.. Авторское свидетельство СССР

Ne 498738, кл. Н 03 К 17/ 00, 1974

4 прототип).

896774

ВНИИПИ

Филиал ППП "Патент, r. Ужгород, ул. Проектная, 4

Ъ ф ь

33 ь ф

1 ф

М

Ъ

3 ф ф ь ф ь ф ф ф ф

Заказ 1 1 726/45 Тираж 684 Подписное