Устройство тактовой синхронизации

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

Q.Ñ.Èöêîâè÷ и И.Н.Титова (7!) Заявитель (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к импульсной технике в части передачи и приема дискретных сообщений, предназначено для подстройки фазы тактовых импульсов по кодовым информационным посылкам, поступающим на вход устройства из канала связи, и может быть применено в системах с жестко установленной длительностью кодовых посылок равной периоду сле10 дования тактовых импульсов.

Известно устройство тактовой синхронизации, содержащее последовательно соединенные задающий генератор и управляемый делитель, а так1$ же последовательно соединенные первый интегратор и пороговый блок, выходы которого подключены к управляющим входам управляемого делителя (1).

Однако известное устройство обладает низкой помехоустойчивостью и большим временем вхождения в синхронизм.

Цель изобретения — повышение помехоустойчивости и уменьшение времени вхождения в синхронизм.

Для достижения. цели в устройства тактовой синхронизации, содержащее последовательно соединенные sapaющий генератор и управляемый делитель, а также последовательно сое диненные первый интегратор и пороговый блок, выходы которого подключены к управлянщим входам управляемого делителя, введены последовательно соединенные формирователь сиг" нала весовой функции, первый умножитель, второй интегратор и второй умножитель, а также элемент ИЛИ и последовательно соединенные третий интегратор и пороговый элемент, вы" ход которого подключен к второму входу второго умножителя, выход которого подключен к первому входу первого интегратора, к второму входу которого через элемент ИЛИ подключены выходы порогового блока, при

896779

4 этом выход задающего генератора подключен к первому входу формирователя сигнала весовой функции, к второму входу которого, а также к второму входу второго интегратора и первому входу третьего интегратора подключен выход управляемого делителя, причем вторые входы первого умножителя и третьего интегратора объединены и являются входом устройства.

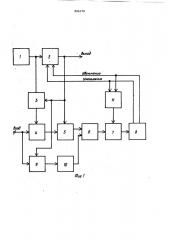

На фиг. 1 приведена структурная электрическая схема предлагаемого устройства, на фиг. 2 — временные диаграммы, поясняющие работу устройства.

Устройство содержит задающий генератор l управляемый делитель 2, формирователь 3 сигнала весовой функции, первый умножитель 4, второй интегратор 5, второй умножитель 6, первый интегратор 7, пороговый блок 8, третий интегратор 9, пороговый элемент 10, элемент ИЛИ 11.

Устройство работает следующим образом.

Частота импульсов задающего генератора l делится в управляемом делителе 2 на выходе которого при этом формируются тактовые импульсы 12 (фиг. 2), которые вместе с импульсами задающего генератора 1 поступают на формирователь 3 сигнала весовой функции, выполненный, например, в виде счетчика с логическими элементами, считающего импульсы задающего генератора 1 и устанавливаемого в начальное состояние тактовыми импульсами 12 управляемого делителя

2. На выходе формирователя 3 сигнала весовой функции формируется сигнал знакопеременной весовой функции

13 (фиг. 2), повторяющийся в каждом такте (интервале между двумя соседними тактовыми импульсами 12) и имеющий максимальные абсолютные значения на границах такта.

На вход устройства из канала свя зи поступает входной сигнал 14, представляющий собой смесь кодовой посылки и помехи. Кодовая посылка 15 в канале связи имеет одно из двух возможных значений "0" или "1", изменяющихся во времени с дискретностью в один такт. В начальный момент работы устройства фронты изменения кодовой посылки 15 в канале связи обычно не совпадают с тактовыми импульсами 12 и имеют некото5

1О !

55 рое случайное смещение фазы. Входной сигнал 14 интегрируется в третьем интеграторе 9 в течение времени между соседними тактовыми импульсами, поступающими на его вход обнуления. Сигнал 16 с выхода третьего интегратора 9 поступает на пороговый элемент 10, на выходе которого в конце каждого такта вырабатывается сигнал 17 равный "0", если выходной сигнал 16 третьего интегратора 9 не превышает пороговый уровень 18, и равный "1", если превышает. Одновременно входной сигнал поступает на первый умножитель

4, где умножается на значение весовой функции 13, поступающее с выхода формирователя 3 сигнала весовой функции, при этом единичное значение входного сигнала соответствует умножению значения весовой функции 13 на +1, а нулевое значение — на — 1.

Выходной сигнал первого умножителя

4 интегрируется во втором интеграторе 5 в течение времени между соседними тактовыми импульсами, поступающими на его вход обнуления. Выходной сигнал 19 интегратора 5 в конце каждого такта поступает на второй умножитель 6, где умножается на значение выходного сигнала 17 порогового элемента 10, причем превышение на выходе порогового элемента 10 соответствует сомножителю +1, а непревышение — сомножителю — 1. Выходной сигнал второго умножителя 6, который формируется в конце каждого такта и является результатом внутриимпульсной обработки входного сигнала, поступает на первый интегратор 7, где накапливается в виде сигнала 20 в течение некоторого количества тактов до тех пор, пока не превзойдет одного из порогов 21 (положительного или отрицательного) порогового блока 8. При пересечении выходным сигналом 20 первого интегратора 7 значения положительного порога 21 порогового блока 8, на выходе последнего вырабатывается сигнал уменьшения коэффициента деления управляемого делителя 2, поступающий на его соответствующий управляющий вход. Такой сигнал возникает как следствие систематического отставания тактовых импульсов . от фронтов полезного сигнала в канале связи и приводит к смещению фазы тактовых импульсов 12 в сторону опережения, т.е. уменьшает их отставание. 11ри пересечении выходным сигналом 20 первого интегратора 7 значения отрицательного порога 21 порогового блока 8, на выходе последнего вырабатывается сигнал увеличения коэффициента деления управляемого делителя 2, что приводит к противоположному смещению фазы тактовых импульсов 12.

Любой из двух выходных сигналов порогового блока 8 через элемент

ИЛИ 11 поступает на вход обнуления первого интегратора 7, после чего накопление сигнала в первом интеграторе 7 начинается снова.

Ири совпадении фазы тактовых импульсов управляемого делителя 2 с фронтами полезного сигнала на входе устройства сигнал на выходе первого интегратора 7 поддерживается вблизи нулевого значения и фаза тактовых импульсов не изменяется.

Эффективность предлагаемого устройства проявляется при высоком уровне помех в канале связи, что осуществляется за счет весовой обработки входного сигнала, его двойного интегрирования в пределах каждого такта и последующего межцуимпульсного накопления результатов внутриимпульсной обработки, при этом существенно снижается вероятность сбоя синхронизации и, тем самым, повышается помехоустойчивость устройства. Вместе с тем, выбор весовой функции, имеющей максимальные абсолютные значения на границах такта и проходящей через ноль в середи.не такта, обусловливает высокую чувствительность устройства даже к небольшим смещениям фазы тактовых импульсов относительно границ кодовых посылок и, как следствие, вы96779 б сокую скорость ввода устройства в синхронизм.

Формула изобретения

Устройство тактовой синхронизации, содержащее последовательно соединенные задающий генератор и управляемый делитель, а также последовательно соединенные первый интегратор и пороговый блок, выходы которого подключены к управляющим входам управляемого делителя, о т л и ч а— ю щ е е с я тем, что, с целью повышения помехоустойчивости и уменьшения времени вхождения в синхронизм, введены последовательно соединенные формирователь сигнала весовой функции, первый умножитель, второй

)y интегратор и второй умножитель, а также элемент ИЛИ и последовательно соединенные третий интегратор и пороговый элемент, выход которого подключен к второму входу второго уу умножителя, выход которого подключен к первому входу первого интегратора, к второму входу которого через элемент ИЛИ подклвчены выходы порогового блока, при этом выход задаюш щего генератора подключен к первому входу формирователя сигнала весовой функции, к второму входу которого, а также к второму входу второго интегратора и первому входу третьего интегратора подключен выход управляемого делителя, причем вторые входы первого умножителя и третьего интегратора объединены и являются входом устройства.

Источники информации, принятые во внимание при экспертизе

Аы opcrое свидетельство СССР

Р 390676, кл. Н 04 J 3/06, 1971 (прототип).

896779

Составитель Г;Лерантович

Редактор С.Юско Техред Т.Иаточка Корректор А.Дзятко

Заказ 11726 45 Тираж 684 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4