Устройство для умножения и деления

Иллюстрации

Показать всеРеферат

Союз Соеетсинк

Соцнарнстнчесина

Ресиубпни

Oll ИСЛНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<,898424 (61) Дополнительное к авт. свид-ву (22) Заявлено ) 5.04.80 (21) 2уц р) 8 2g с присоединением заявки М (23) ПриоритетОпубликовано >5.0) ..82. Бюллетень .% 2

Дата опубликования описания ) 5 .0 t . 8р (5I)M. Кл.

G 06 Р 7/52

Веудерстаекявй кеиктет

СССР ге делан иаебретеквк к етарытке (53) УДК 68).325 (088. 8) б (72) Авторы изобретения

Ю.П. Барметов и Ю.И. Евтее (71) Заявитель

Воронежский технологический (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ И ДЕЛЕНИЯ

Недостатком данного устройства является сложность его и его блоков, так как, в частности, блоки логарифмического и атилогарифмического пре- образования помимо элементов собственного логарифмирования и атилогарифми- 2о рования содержат также пороговые элементы, масштабные элементы, делители, сумматоры, источники опорного на- пряжения.

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и специализированных вычислительных устройствах, Известно логарифмическое вычисМ лительное устройство для линейных преобразований аналоговых сигналов, содержащее логарифмические преобразователи, блок линейных преобразова10 ний, антилогарифмический преобразователь, блок формирования выходных масштабных коэффициентов (11.

Наиболее близким по техническому решению к изобретению является устройство умножения и деления, содержащее логарифмирующие функциональные преобразователи,потенцирующий функциональный преобразователь,алгебраический сумматор, причем входы логарифмирующих функциональных преобразователей соединены со входами операндов устройства, выходы логарифмирующих преобразователей соединены со входами алгебраического сумматора, выходы которого соединены со входами потенцирующего функционального преобразователя, выход которого соединен с выходом устройства t.23 .

Недостатком этого устройства являются достаточно высокие затраты оборудования, в частности, для реализации потенцирующего функциональяого преобразователя.

Цель изобретения - сокращение затрат оборудования.

898424 эанное старшими разрядами выхода сум матора.

Такое построение устройства позволяет сократить объем оборудования известного устройства беэ уменьшения

его быстродействия эа счет использования в устройстве функционального преобразователя, осуществляющего потенцирование младших разрядов мантиссы. Функциональные преобразователи, используемые в устройстве, имеют одинаковую структуру и могут выполняться на постоянных запоминающих устрой ствах. Алгебраический сумматор в отличие от простого сумматора содержит дополнительно, две линейки переключателей прямого или инверсного кода, а блок сдвига может выполняться на широко распространенных схемах мультиплексирования. Таким образом, вновь вводимые блоки и связи не являются более сложными и аппаратуроемкими.

Формула изобретения

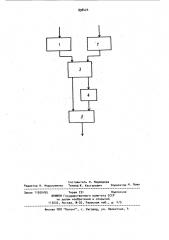

Приведение результата к форме с фиксированной запятой осуществляется. блоком сдвига 5 путем сдвига выхода потенцирующего функционального преобразователя 4 относительно выхода устройства вправо или влево в зависимости от знака на выходе алгебраическо" го сумматора 3 на число разрядов, ука55

Поставленная цель достигается тем, что в устройство введен блок сдвига, причем входы логарифмирующих функциональных преобразователей соединены со входами операндов устройства, выходы логарифмических преобразова:телей соединены со входами алгебраического сумматора, выходы младших разрядов которого соединены со входами потенцирующего функционального пре образователя, выходы которого подключены к информационным входам блока сдвига, управляющие входы которого подключены к выходам старших разрядов алгебраического сумматора, а выходы блока сдвига являются выходами устрой ства.

На чертеже представлена структур ная схема устройства.

Устройство содержит логарифмирующие функциональные преобразователи 1 и 2, алгебраический сумматор 3, петен цирующий функциональный преобразователь 4, осуществляющий потенцирование младших разрядов мантиссы, блок сдвига 5.

Устройство работает следующим образом.

Умножение и деление чисел, представленных в форме с фиксированной запятой, в данном устройстве реализуется по следующему алгоритму:

1Е Р,.Е0, 4),. а 2 (mega. — 8оРЬ).

Логарифмы чисел а и Ь подаются на вход алгебраического сумматора 3, где над ними производят операции суммирования или вычитания и затем младшие разряды, соответствующие мантиссе числа с, и знак поступают в потенцирующий функциональный преобразователь 4, выполненный аналогично логарифмическим функциональным преобразователям 1 и 2 и реализующий операцию потенцирования младших разрядов мантиссы, 30

Устройство для умножения и деления, содержащее логарифмирующие функциональные преобразователи, потенцирующий функциональный преобразователь, алгебраический сумматор, причем, входы логарифмирующйх функциональных преобразователей соединены со входами операндов устройства, выходы логарифмирующих преобразователей соединены со входами алгебраического сумматора, выходы младших разрядов которого соединены со входами потенцирующего функционального преобразователя, о т л и ч а ю щ е е с я тем, что, с целью сокращения затрат оборудования, в неге введен блок сдвига, причем выходы старших разрядов алгебраического сумматора подключены к управляющим входам блока сдвига, информационные входы которого соединены с выходами потенцирующего функционального преобразователя, а выходы блока сдвига являются выходами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР и 650082, кл. G 06 G. 7/24, 1976.

2. Бузунов Ю.А., Вавилов Е.Н-. Принципы построения цифровых вычислительных машин. Киев, "Техника", 1972 (прототип).

898424

Составитель Л. Иедведева

Редактор И. Недолуженко Техред N. Кастелевич Корректор И Пожо

Заказ 11950/65 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий I13035, Москва, N-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4