Устройство для деления

Иллюстрации

Показать всеРеферат

М.В. Черкасский, А.А. Мельник и В.В. Чер крсскаи

l6 аь

У (72) Авторы изобретения (21) Заявитель (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

Изобретение относится к вычислительной технике и может быть исполь« зовано в арифметических устройствах для деления большого массива многоразрядных чисел.

Известно устройство .для деления чисел беэ восстановления остатка, в котором при отрицательном остатке очередного вычитания не производится восстановление положительного остатка, а вместо вычитания делителя s следующем такте. осуществляется его сложение f13

Как правило, эа один такт образуется один очередной остаток и одна цифра частного, поэтому при делении большого массива многоразрядных чисел эти устройства характеризуются недостаточным быстродействием.

Наиболее близким по техническому решению к изобретению является у тройство, содержащее и вычислительных блоков (где n - -разрядность обрабатываемых чисел), каждый иэ которых содержит регистры делимого, делителя, частного и сумматор, входы первой группы которого соединены с вы" ходами регистра делимого, выходы i-x разрядов (где 11,..., и ) регистра делителя каждого вычислительного блока, подключены ко входам i"x разрядов регистра делителя последующего вычислительного в ока, выходы )""х разрядов регистра частного каждого вычислительного блока, подключены ко входам i-х разрядов регистра делителя последующего вычислительн©га блока, выходы i-х разрядов регистра частного каждого вычислительного бло» ка подключены ко входам (i-1)-х разрядов регистра частного последующего вычислительного блока Г23 °

Недостатком этого устройства является выполнение деления в двй полутакта в одном вычислительном блоке, что замедляет обработку и усложняет устройство.

898425 4

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство введена группа weментов НЕ, а в каждый вычислительный блок, кроме последнего, введен коммутатор, причем выходы регистра де» лимого подключены к информационным входам первой группы коммутатора, информационные входы второй группы сумматора подключены к выходам регистра делителя, входы регистра делителя первого вычислительного блока соединены с выходами элементов НЕ группы, yn" равляющие входы коммутатора соединены с прямым и инверсным выходами знакового разряда сумматора, инверсный выход знакового разряда сумматора соединен со входом младшего разряда регистра частного, выход i-ro разряда коммутатора каждого вычислительного блока соединен со входом {i-1)-го разряда регистра делимого последующего вычислительного блока.

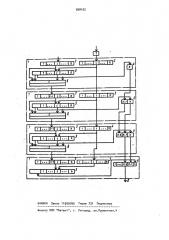

На чертеже представлена функциональная схема устройства для деления.

Устройство содержит и вычислитель" ных блоков 1, каждый из которых со" держит регистры делимого 2, делителя

3 и частного 4, сумматор 5, коммутатор 6, который содержит две группы элементов И íà и входов, объединенных элементом ИЛИ, инвертор 7, вы" ход 8.

Устройство работает следующим образом.

Деление выполняется с восстановлением остатка за и этапов.

В первом такте в регистр 2 первого вычислительного блока .1 записывает первое делимое co ñäâèãîì влево на один разряд, а в регистр 3 " первый делитель, предварительно проинвертированный в инверторе 7. На сумматоре

5 производится вычитание из делимого делителя. Если остаток получился положительный, разряд частного равен единице и информация с выходов сумматора 5 проходит в коммутатор 6. Если остаток отрицательный, разряд частного равен нулю и в коммутатор 6 tlpoxG дит первоначальное значение делимого из регистра 2, т.е. происходит восстановление остатка.

Во втором такте производится запись результатов вычислений первого

,вычислительного блока 1 во второй: запись содержимого коммутатора 6 в регистр 2 со сдвигом влево, передача о

ЭО

Э5 ю

55 значения первого делителя в регистр 3, запись первой цифры частного с выхода знакового разряда сумматора 5 в и-й разряд регистра 4 {первого вычислительного блока). Одновременно в регистры 2 и 3 поступают значения второй пары чисел, В первом вычислительном блоке производят деление второй пары чи" сел, а во втором получают второй результат деления первой пары чисел.

В третьем такте результаты вычислений, полученные во втором вычислительном блоке 1, записывают в третий вычислительный блок, а результаты первого вычислительного блока - во второй. В освободившиеся регистры 2 и 3 nepsoro блока поступает третья пара чисел. Первая цифра частного от деления второй пары чисел записывает" ся с регистра 4 первого вычислительного блока 1 в регистр 4 второго вычислительного блока со сдвигом влево в {и-1)-й разряд.

Результат деления каждой пары чисел образуется на и тактов, при этом результат деления первой пары чисел получен на выходе 8 устройства через и тактов, а каждого следующего числа - через один такт. Знак частного определяется путем сложения по моду" лю два знаковых разрядов. делимого и делителя (на чертеже не показаны).

Быстродействие устройства определяет-. ся длительностью одного такта обработки данных в одном вычислительном блоке, которая равна

Т = TetlH + TUAu, где Тс м - время суммирования на сумматоре 5, Т„ ц - задержка информации схемой И-ИЛИ 6.

При построении устройства на элементах серии 155 для 16-разрядных чисел Т н = 60 нс Т„q = 20 нс и Т =

= 80 нс.

П р и м е.р. Разделитель.+0,70312, на "0,34375, Допустим, в устройстве обрабатываются двоичные числа с разрядностью п=6. Тогда в двоичной,сисФ теме эти числа представлены кодами

0,101101 и 1,010110.

Код знака частного в устройстве определяется следующим образом.

199=1. Дальше в устройство числа поступают с положительными знаками.

Делимое поступает в регистр делимого

2 со сдвигом влево на один разряд, а делитель поступает в регистр делите5 d разрядность обрабатываемых чисел), каждый из которых содержит регистры делимого, делителя; частного и сумматор, входы первой группы которого соединены с выходами регистра делимого, выхоцы 1-х разрядов (где 1=1,..., n) регистра делителя каждого вычислительного блока, подключены ко входам

i-x разрядов регистра делителя последующего вычислительного блока, выходы i-x разрядов регистра, частного каждого вычислительного блока подключены ко входам (i-1)-х разрядов регистра частного последующего вычислительного блока, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия в устройство введена группа элементов НЕ, а в каждый вычислительный блок, кроме последнего, 20 введен коммутатор, причем выходы регистра делимого подключены к информационным входам первой группы коммутатора, информационные. входы второй группы сумматора подключены к выходам регистра делителя, входы регистра делителя первого вычислительного блока соединены с выходами элементов НЕ группы, управляющие входы коммутатора соединены с прямым и инверсным выходами знакового разряда сумматора, ин" версный выход знакового разряда сумматора соединен со входом младшего разряда регистра частного, выход i-го разряда коммутатора каждого вычислительного блока соединен со входом (1-1)-oro разряда регистра делимого последующего вычислительного блока.

1-й 1 010010 Pr 3

1,И1111 СИ 5

Pr 2 Pr 4 011

3-й 1,010110

1 0100!О

° Ф1 «ю«

О, 101001

СИ 5

4-й 1,010010

1 010010

«««««е«

О, 100101

Pr 2 Pr 4

Рг 3

СИ 5

5 89842 ля 3, .предварительно инвертируясь в инверторе 7. Знаковый разряд регистра делимого используется для запоминания сдвигаемого левого разряда. Сложение в сумматорах производится в до- у полнительном коде путем добавления единицы в младший разряд

Блок О, t01100 Pr 2 Pr 4 0

2"й 1,011000 Рг 2 Pr 4 01

1 010010 Рг 3

6,101011 СИ 5 !Ф

5-и 19001010 Pr 2 Pr 4 01111 И

1д0100 1 0 Рг 3

0 611101 СИ 5 б-й 0,11 I010 Рг 2 Pr 4 011111

1д010010 Pr 3 3О

0,001101 СИ- 5 1аким образом, устройство для деления является однородным по структуре высокопроизводительным при обработке больших массивов многоразрядных чисел, простым по исполнению, обладает большим быстродействием за счет уменьшения времени одного такта обработки данных.По сравнению с известным быстродействие данного устройства © повышается примерно в два раза. формула изобретения

Устройство для деления, содержащее.п вычислительных блоков (где пИсточники информации, принятые во внимание при экспертизе

1. Патент СВА М 3.492.468, кл. G 06 Г 7/39, 1970.

2. Авторское свидетельство СССР

i1 705447, кл. G 06 F 7/39, 1976 (прототип).