Устройство для сопряжения процессора с памятью

Иллюстрации

Показать всеРеферат

Союз Советсмик

Социалистических

Республик

ОЛ ИСАНИИ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЮТВЛЬСТВУ

Ii i ) 898437 (Bl ) Дополнительное и ввт. саид-ву— (22)Заявлено 21.04.80 (21) 2911294/18-24 с присоединением заявки М— (23)ПриоритетОпубликовано 15.01.82. Ькмлетень М 2

Дата опубликования описания 17, 01. 82 (5! )М. Кл.

G 06 F 3/04

С 06 Г 13/06

Гоеударстесниый квинтет

СССР вв делам изебрвтеиий и атнрытий (53) УДК 681 325 (088. 8) (72) Авторы изобретения

А. П. Кондратьев, Н. А. Беляева и С. В. (71) Заявитель (54 ) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С ПАМЯТЬЮ

IO ния (1 ).

Изобретение относится к вычисли« тельной технике и может быть использовано в ЭВМ для сопряжения процессора с модулями памяти, имеющими различную длительность цикла.

Известны устройства управления обращением к памяти, содержащие генератор, распределитель, узел управления пуска распределителя, узел пусков памяти, узел задержки, узлы индикации зоны и запросов к свободной зоне, узел подготовки обращения к свободной зоне и блока управлеНедостаток этих устройств заключается в ограниченных функциональных возможностях.

Наиболее близким к предлагаемому техническим решением является устройство для сопряжения, содержащее два триггера, синхронизатор, включаю" щий задающий генератор и узел выработки тактовых импульсов, два элемента

И и два элемента ИЛИ, формирователь импульса, элемент задержки, схему сравнения, элемент И-ИЛИ, регистр, счетчик, дешифратор, сумматор, при" чем вход запроса устройства соединен с первыми входами первогo и второго триггеров и первыми входами первого и второго элементов И, первый выход первого триггера соединен со вторым входом первого элемента И, выходом подключенного к первому входу первого элемента 3МПФ, выход которого соединен со вторым входом второго триггера 1,2).

Недостаток этого устроиства зак" лючается в больших аппаратурных затратах.

Цель изобретения - сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в устройство, содержащее триггер ожидания, входы которого подключены ко входам "Запрос" устройства, а выход - к первому входу первого элемент

3 89843 та И, выходом соединенного с первым входом первого элемента ИЛИ, вторые элементы И и ИЛИ, триггер пуска, соединенный первым входом с выходом первого элемента ИЛИ, и задающий генератор, подключенный выходом к первому входу узла выработки тактовых импульсов, введены два элемента НЕ, причем второй вход первого элемента И подключен ко входу "Чтение" устройст- Я ва, второй вход первого элемента ИЛИ соединен с выходом второго элемента

И, первый вход которого является входом "Зались" устройства, второй вход соединен с выходом триггера ожида- 1 ния, а третий вход - через первый элемент НЕ со входом "Данные приняты" устройства и первым входом второго элемента ИЛИ, второй вход которого соединен со входом Данные 36 готовы" устройства и через второй элемент НЕ - с третьим входом пер.вого элемента И, а выход - со вторым входом триггера пуска, третий и четвертый входы и выход которого ,подключены соответственно к выходу и первому и второму входам узла выработки тактовых импульсов, выход которого является тактовым выходом устройства, 36

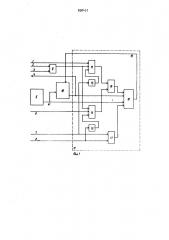

На фиг. 1 представлена блок-схема устройства; на фиг. 2 — функциональная схема узла выработки тактовых импульсов.

Устройство содержит (см.фиг.11 И вход 1 "Чтение" и входы 2 и 3 "Запрос" устройства, тактовый выход 4 устройства, задающий генератор 5, вход б "Запись", вход 7 "Данные го" товы" и вход 8 "Данные приняты" уст- 46 ройства, триггер 9 ожидания, узел

10 выработки тактовых импульсов, узел 11 пуска-останова, состоящий из элементов И 12 и 14,. элементов

HE l3 и l5, элементов ИЛИ 16 и 17 43 и триггера 18 пуска, имеющего выход

19

Узел 10 выработки тактовых импульсов может быть реализован в аиде коль цевого счетчика (в данном примере четырехразрядного ), состоящего из триггеров 20-23, элементов И 24-31, элементов HE 32-36, выход 37-40 узла, образованного выходами эле ментов И 24-27, входа 41 узла, соединенного с задающим генератором 5, входа 19 пуска узла, соединенного с выходом триггера пуска и входом 42 на7 4 чального сброса узла (на фиг. 1 не показан) .

Устройство работает следующим образом.

Если триггер 18 установлен в "1" то сигнал с его выхода, поступая по

7 вине 19, разрешает запуск кольцевого счетчика. Коммутация триггеров согласно фиг.2 обеспечивает выработку последовательных сигналов двойной длительности по отношению к импуль сам задающего генератора и перекрывающихся между собой. Сигналы с выхода триггеров поступают на элементы

И 24-27, с выхода которых и выдаются тактовые импульсы. В рассматриваемом ниже примере в течение такта необходимо выработать четыре импульса, что требует наличие четырехразрядного кольцевого счетчика. При рассмот" рении работы устройства предполагается, что оно используется с процессором с микропрограммным управлением и триггер 9 ожидания является разрядом микрокоманды и устанавливается при считывании последней. Так как микрокоманда,управляющая действиями в текущем такте, считывается в конце предыдущего такта г то триггер 9 указывающий на то, что данные, считываемые из основной памяти, будут нужны для обработки (или данные, записываемые в память, будут изменены! в данном такте, установится в конце предыдущего, такта. Пусть в

i-ом такте процессор выдает сигнал

"Чтение" на вход 1 {или "Запись" на вход б)(см. фиг. 1),. а данные из памяти потребуются процессору (или данные для записи изменяются) в (i+2)-ом такте, на что будет указывать единичное состояние триггера 9 в конце (i+1)-ого такта. Если при установке триггера 9 в "1" информация еще не будет считана из основной памяти, на что указывает отсутствие сигнала на входе 7 "Данные готовы" (либо нельзя изменять информацию, которая еще нужна основной памяти для выполнения заданной в i-ом такте операции "Запись", на что указывает отсутствие сигнала на входе 8), то сигнал с выхода элемента И 12 (элемента И 14) сбросит в конце (i+1) -ого такта триггер l8 (см.фиг.1). Нулевое состояние триггера 18, поступая на вход 19 узла выработки тактовых импульсов (см.фиг,2) заблокирует выработку оче5 89843 редной серии тактовых импульсов, а следовательно, и выполнение (i+2) -ого такта процессора до появления сигнала "Данные готовы" на входе 7 ("Данные приняты" на входе 8), Появление сигнала "Данные готовы" (или "Данные приняты") через элемент ИЛИ 17 по импульсу задающего генератора 5 установит триггер 18 в "1" (см.фиг.1}, Единичный сигнал с выхода триггера 10

18,поступая на вход узла выработки тактовых импульсов,а значит и выполнение (i+2)-ого такта. Если сигналы "Данные готовы" "Данные приняты" ) приходят до установки в "1" триггера 9 И ожидания, то процессор работает без остановки.

Таким образом, устройство с мень" вим объемом оборудования обеспечивает возможность перекрытия работы 30 процессора и основной памяти. Процессор запускает память (например, на чтение операнда), но не останавлива" ется в ожидании данных, а продолжает свою работу (например, формирует или модифицирует адрес другого операнда) и только тогда, когда дальнейшая работа процессора невозможна без данных из памяти, процесор останавли- вается, если же к этому моменту данные уже готовы, то процесор работает без останова. Кроме того, устройство обеспечивает воэможность при многомодульной организации основной памяти подключение к процессору модулей па- В5 мяти с разным быстродействием,так как, при асинхронной работе процессора и памяти, быстродействие подключенных модулей памяти может быть учтено.

Формула изобретения 4р

Устройство для сопряжения процессора с памятью, содержащее триггер ожидания, входы которого подключены ко входам "Запрос" устройства, а выход -. к первому входу первого элемента И, выходом соединенного с первым входом первого элемента ИЛИ, вторые элементы И и ИЛИ, триггер пуска, соединенный первым входом с выходом первого элемента ИЛИ, и задающий генератор, подключенный выходом к первому входу узла выработки тактовых импульсов, о т л и ч а а щ е е с я тем, что, с.целью сокращения аппаратурных затрат, в устройство введены два элемента НЕ, причем второй вход пер" вого элемента И подключен ко входу

"Чтение" устройства, второй вход первого элемента ИЛИ соединен с выходом второго элемента И, первый вход которого является входом "Запись устройства, второй вход соединен с выходом триггера ожидания, а третий входчерез первый элемент НЕ со входом

"Данные приняты" устройства и первым входом второго элемента ИЛИ, второй вход которого соединен со входом

"Данные готовы" устройства и через второй элемент НЕ - с третьим входом первого элемента И, а выход - со вторым входом триггера пуска, третий и четвертый входы и выход которого подключены соответственно к выходу и первому и второму входам узла выработ" ки тактовых импульсов, выход которого является тактовым выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

1г Я6444, кл. 6 06 F 13/06, 1975.

2. Авторское свидетельство СССР по заявке N 2889809, кл. G 06 F 3/04, 1980 (прототип).

898437

Составитель В. Вертлиб

Редактор В. Бобков Техред A.Áàáèíåö Корректор С. Шекмар

Заказ 11951/66 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауаская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4