Умножитель частотно-импульсных сигналов

Иллюстрации

Показать всеРеферат

Союз Советск ив

Социапистичесник

Республик

ОП ИСАКИИ

ИЗОВРИтЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (1898445 (6! ) Дополнительное к авт. свид-ву (22)Заявлено 26.03.80 (2!) 2851280/18-21 с присоединением заявки ре (23) П риоритет

Опубликовано 1 5, 01 ° 8 2 ° Бюллетень М 2

Дата опубликования описания 15.0 1.82 (51)M. Кл.

G 06 G 7/16

Государстванный квинтет

СССР

ho делаи изабретенн!! и открытий (53) УДК 681. 325 (088. 8) (72) Авторы изобретения

А.Э;Трифжщ !

Л „д

s! "ëãù

Т.К.Исмаилов, Г.И.Ильканаев, А.М.Самедов и

Особое конструкторское бюро "Каспий"

АН Азербайджанской CCP (7!) Заявитель (54) УИНОЖИТЕЛЪ ЧАСТОТНО-ИМ11УЛЬСНЫХ

СИГНАЛОВ

Изобретение относится к автомати-1 ке и вычислительной технике и может быть использовано при умножении частотно-импульсных сигналов на коэффициент, больший единицы, с целью увеличения статической и динамической точности частотомеров.

Известен умножитель частотно-импульсных сигналов, содержащий управляемый генератор частоты, блок перераспределения, блок выделения разности периодов двух частот, элементы совпадения, счетчик импульсов, преобразователь код-напряжение, триггеры и делитель частоты (! ).

Недостаток этого устройства — ограниченный диапазон умножаемых частот.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее делитель частоты, счетчик импульсов, соединенный через преобразователь код-напряжение с генератором частоты, блок временной раздвижки импульсов, блок задержки, блок выцеления разности периодов, триггер и элементы совпадения, причем выход делителя частоты соединен со входами блока за держки и одним входом триггера, второй вход которого подключен к выходу блока задержки, выход блока временной раздвижки соединен со входом блока задержки и одним входом блока выделения разности периодов, выход триггера подключен к первому входу одного элемента совпадения (? ).

Однако данное устройство характеризуется ограниченным диапазоном

15 умножаемых частот.

Цель изобретения — расширение диапазона умножаемых частот при одновременном упрощении устройства, Поставленная цель достигается

20 тем, что в умножитель частотно-импульсных сигналов, содержащий делитель частоть1, элементы И, первый вход первого из которых соединен

89844 с прямым выходом триггера, счетчик импульсов, генератор опорной частоты и элемент задержки, введен дешифратор, и-ый выход которого соединен с первым входом триггера и первым входом второго элемента И, второй вход которого подключен к входу элемента задержки. второму входу триггера и входной шине, а (и+2)-ой выход — с первым входом третьего элемента И, второй вход которого соединен с инверсным выходом триггера, а выход — с первым управляющим входом делителя частоты, второй управляющий вход которого соединен с выходом второго элемента Л, счетный вход — с выходом генератора опорной частоты, а выход — с вторым входом первого элемента И и входом счетчика импульсов, установочный вход которого соединен с выходом элемента задержки, а выход — со входом дешифратора.

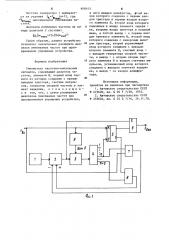

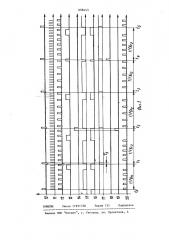

На фиг. 1 представлена структурная схема устройства на фиг. 2— временные диаграммы, поясняющие его работуа

Устройство содержит генератор 1 опорной частоты, делитель 2 частоты с управляемым коэффициентом деления, счетчик 3 импульсов, дешифратор 4, триггер 5, элементы 6-8 И, элемент 9 задержки.

Умножитель частотно-импульсных сигналов работает следующим образом.

В исходном состоянии коэффициент деления делителя 2 установлен таким, что на его выход за один период входной частоты Гцх„(см. фиг. 2 10) проходят (и+1) импульс генератора 1 (см. фиг. 2, 12). На выход умножителя за это же время пройдут и импульсов, так как на прямом выходе триггера 5 формируется импульс длительностью 1/f, где f — частота импульсов на выходе делителя 2. Триггер 5 устанавливается в состояние "1" с поступлением входного импульса и возвращается в исходное состояние с поступлением n-ro импульса с выхода делителя 2, т.е. с п-го выхода дешифратора 4, управляемого счетчиком

3. Таким образом f. =1 „n (см. фиг. 2.20;

Ьы в1

2.15 2.13, время t t ). На инверсном выходе триггера 5 фор- ЭФ мируется импульс, длительность которого равна длительности между поступлением и-го импульса с выхода де5 ф шифратора 4 и ближайшим входным импульсом (см. фиг. 2. !6) . На выходах элементов 7 и 8 установлены уровни логической единицы. С поступлением каждого входного импульса через время Г (см. фиг. 2.!7), определяемым элементом задержки, счетчик 3 и дешифратор 4 возвращаются в исходное состояние.

Частота на выходе делителя 2 частоты может принимать значения f =

=(1/К-К/К) 1б, где f — частота импульсов генератора 1, К вЂ” максимальный коэффициент деления частоты делителя 2.

В исходном состоянии f= —.f =

Ь

Yê С

=(п+1); L принимает значения от l до К.

С уменьшением частоты входных импульсов до f „ т.е, с увеличением У их периода (см. фиг. 2, время С„-с ), на выход делителя 2 при том же коэффициенте деления его L/К за один период входной частоты пройдут (n+2) и более импульсов (см. фиг. 2. 12) .

С появлением импульса на (и+2)-ом выходе дешифратора 4 (см. фиг. 2.14) и совпадении его с импульсом на выходе триггера 5 на выходе элемента 8

I появится импульс (см. фиг. 2. !9), поступающий на первый управляющий вход делителя 2 и изменяющий коэффициент деления его таким образом, что ча выход делителя частоты 2 за один период входной частоты вновь будет проходить (n+1) импульс, т.е.

f- =(и+1) f „, где — дискретность изменения частоты на выходе делителя 2 (см. фиг. 2, время tZ-t ).

С увеличением частоты входных импульсов до ФВ„, т.е. с уменьшенивх ем их периода, при совпадении импульса с n-ro выхода дешифратора

4 и ближайшего входного импульса частоты f>< на выходе элемента 7 (см. фиг. 2,18 ) появится импульс (см. фиг. 2, время -t<), изменяющий коэффициент деления делителя

2 частоты и устанавливающий его теперь уже равным Г =(и+1) ° Г;х (см. фиг. 2, время tg-t<).

Очевидно, в статическом состоянии максимальный период между двумя ближайшими импульсами на выходе устройства может составить два периода текущей частоты на выходе делителя 2 частоты.

898445

Таким образом, данное устройство позволяет значительно расширить диапазон умножаемых частот при одновременном упрощении устройства.

Формула изобретения

Умножитель частотно-импульсных сигналов, содержащий делитель частоты, элементы И, первый вход первого из которых соединен с прямым выходом триггера, счетчик импульсов, генератор опорной частоты и элемент задержки, о т л и ч а ю щ и й— с я тем, что, с целью расширения диапазона умножаемых частот при одновременном упрощении устройства, 20

Частота генератора 1 выбирается из условия f =f (n+l), где

@мсяс — максимальная умножаемая чацх щ, с тота.

Диапазон изменения частоты на вы- S ходе делителя 2 составит

1Ь ф с+" ): (ìé4" в него введен дешифратор, р-ый выход которого соединен с первым входом триггера и первым входом второго элемента И, второй вход которого подключен к входу элемента задерж— ки, второму входу триггера и входной шине, а 0+2-ой выход — с первым вхо» дом третьего элемента И, второй вход которого соединен с инверсным выходом триггера, второй управляющий вход которого соединен с выходом второго элемента И, счетный вход— с выходом генератора опорной частоты, а выход — с вторым входом первого элемента И и входом счетчика импульсов, установочный вход которого соединен с выходом элемента задержки, а выход — со входом дешифратора, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 475620, кл. G Об F 7/39, 1975.

2. Авторское свидетельство СССР

У 355624, кл. G 02 G 7/16, 26.11.70.