Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()898502 (6I ) Дополнительное к авт. свнд-ву (22) Заявлено 24 08,78 (21)2660999/18 24 с присоединением заявки М— (23) Приоритет

Опубликовано 15.01.82. Бюллетень № 2

Дата опубликования описания 18.01.82 (53)M. Кл.

G 1 1 С 9/00 (Ьеударотееииый комитет

СССР по дедки изобретений и открытий (53) УДК 681. .3 27.66 (088.8) "

B. П. Андреев, В. Ф. Семенов, А . Н. Пресняков и A. Н. Поскребышев т (72) Авторы изобретения (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминаю- щим устройствам (ЗУ) .

Известно оперативное запоминающее устройство, содержащее регистры четного и нечетного байта, блок формирования, коммутаторы четного и нечетного байта, блок запоминания П) .

Однако при необходимости работы с переменными форматами слов от байта и до длины большей, чем два байта, аппаратурные затраты становятся больши10 ми.

Наиболее близким по технической сущности к предлагаемому является запоминающее устройство с одновременной выбор!

5 кой переменного массива слов, содержа .щее модули памяти, регистр адреса, разделенный на части - старшую и младшую, коммутаторы входной и выходной информации (кольцевые сдвигатели), шифрато20 ры и дешифраторы, блок добавления единицы (преобразователь кода адреса) (23.

Однако при необходимости использования ЗУ в системах, предполагающих сме2 ну формата ЗУ в пропессе работы на продолжительное время или постоянную работу со словами различного формата при решении какой-либо задачи большая часть коммутирующего оборудования исцользуе ся нецроиэводительно.

Белью изобретения является повышение надежности устройства.

Поставленная цель достигаатся тем, что в запоминающее устройство, содержащее регистр адреса, одни из выходов которого соединены с одними иэ входов эапоминанхпих модулей, другие входы ко торого подключены к выходам регистра входного слова, а выходы запоминающих модулей соединены со входами регистра выходного слова, введен блок анализа формата слова, одни из входов которого соединены с другими выходами регистра адреса, другие входы блока анализа формата слова подключены к шине управления, а выходы - к соответствукипим входам запоминающих модулей, а также блок анализа формата слова, содержащий

02 ф

Таблица

096 х 4 байта

4,096 х 4 байта

16 384 х 1 байт

8,192 х 2 байта

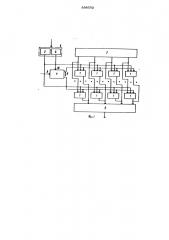

3 8985 элементы И-НЕ, первые и вторые входы первого, второго, третьего и седьмого элементов И-НЕ и вторые и третьи входы четвертого, пятого и шестого элементов И-HE подключены к одним из входов блока анализа формата, а первые входы четвертого, пятого, шестого элементов И-НЕ подключены к выходу второго элемента H HE, выходы первого и седьмого элементов И HE подключены te к первым входам соответственно восьмого, девятого, десятого и одиннадцатого элементов И-НЕ, вторые входы которых подключены к выходам третьего, четвертого, пятого и шестого элементов И-HE„1$ а третьи - к другому входу блока анализа формата, выходы восьмого, девятого, десятого и одиннадцатого элементов И НЕ подключены к выходам блока анализа формата слова. Зе

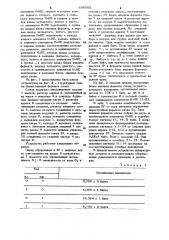

На фиг, 1 представлена блок-схема устройства; на фиг. 2 - структурная схема блока анализа формата слова, Схема содержит запоминающие модули

1 пемяти, регистр адреса 2, разделенный-П на части - младшую 3 и старшую 4,причем выходы младшей части 3 регистра адреса 2 соединены со входами запо. минающих модулей, регистр входного слова 5, выходы которого соединены с дру- ш гимн входами модулей 1, регистр выход» ного слова 6, входы которого соединены с выходами модулей 1, коммутатор формата слова 7, выходы 8 которого совди» иены с третьими входами модупей 1 памяти, входы 9 являются шинами управле» ния сменой формата слова ЗУ, а входы

10 соединены со старшей частью 4 регистра 2.

Устройство работает следующим образом.

Перед обращением к ЗУ с записью или со считыванием на входы 9 коммутатора 7 подается код управляющих потенпиалов В . B зависимости от кода В и старших разрядов адреса, поступающих на входы 10 блока анализа формата слова 7 из старшей части 4 регистра адреса 2, на выходе 8 вырабатываются потенциалы, разрешающие обращение к модулю или группе модулей. Иэ младшей части 3 регистра адреса 4 поступают младшие разряды кода адреса для выбора в модуле или группе модулей ячейки памяти. Один модуль вмещает слов длиной в один байт. Если число модулей равно Т, то организация ЗУ может иэ себя представлять модификации: слов длиной в r байтов; 2 g слов длиной в байтов и т.д. по и. Г слов длиной в один байт, при кратности изменения

k емкости ЗУ и формата слова равной двум.

Можно построить блок анализа формата слова 7 и так, что изменение емкости ЗУ будет происходить с кратностью не равной двум.

На фиг. 2 показан пример построения блока анализа формата слова, осуществляющего изменение организапии накопителя от 16К х 1 байт, до 4К Х 4 байта с кратностью 2 и который содержит одиннадцать элементов И-НЕ 11-21.

B табл. 1 показана зависимость организации ЗУ от кода сигналов управления перестройкой формата слова В, Блок анализа формата слова собран на двух- и трехвходовых элементах И HE и вырабатывает сигналы 1- У4. В табл. 2 показана зависимость формирования потенциальных сигналов у 1- У4 от старших разрядов адреса А12, А13 и организации накопителя ЗУ. Емкость одного модуля

0,5Кх1 бейт. Всего модулей 32. Они организованы в столбцы .У 1- 4; Потенциальные сигналы У1- У4 посгупают на соответствующие столбцы накопителя.

В предлагаемом устройстве аппаратурные затраты в комплектующем оборудовании уменьшаются примерно в десять раз, 898502

Таблица 2

Код старших разрядов адреса А lÇ А12

Организация накопителя

4,096х4 байта 8.192х2 байта 16384хl байт

У> У2УЗУ4 yiy2 93у4 У1V2Y3y 4

Yl У2 3 у 4 У1 У2 3 У4 pl. У2 3 p4

01 1

У 1 У2 УЗ У4 Yl У2 3 4 yl y2 УЗ Y4 . У1Ч 2 УЗЧ4- Yl У2 УЗ У4 ..У1У2УЗ у4

1

Формула изобретения

1. Запоминаюптее устройство, содержащее регистр адреса, одни из выходов которого соединены с одними из входов запоминающих модулей, другие входы кото- рого подключены к выходам регистра входного слова, а выходы запоминаюших модулей соединены со входами регистра вы» ходного слова, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит блок анализа формата слова, одни из входов которого соединены с другими выходами регистра адреса, другие входы блока анализа формата слова подключены к шине управления, а выходы - к соответствующим входам за35 поминакИцих модулей.

2. Устройство по и. l.. о т л и ч аю m е е с я тем, что блок анализа формата слова содержит элементы -HE, первые и вторые входы первого, второго, о третьего и седьмого элементов И HE u вторые и третьи входы четвертого, пятого и шестого элементов И-НЕ подключе ны к одним из входов блока анализа формата, а первые входы четвертого, пято

: го и шестого элементов И-HE подключены к выходу второго элемента Ц-НЕ, выходы первого и седьмого элементов И-НЕ цод ключены к первым входам соответственно восьмого, девятого, десятого и одиннадцатого элементов И-НЕ, вторые входы которых подключены к выходам третьего четвертого, пятого и шестого элементов

; И-НЕ, а третьи к другому входу блока анализа формата, выходы восьмого, девятого, десятого и одиннадцатого элемен тов И-НЕ подключены к выходам блока тнализа формата слова.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 483705, кл. G 11 С 7/00, 1972.

2. Авторское свидетельство СССР

Nq 367456, кл. G 11 С 9/00, 1971 (прототип).

898502

fur.2

Составитель Л. Амусьева

Редактор A. Йолинич Техред С. Мигунова Корректор С. Шомак

Заказ 1 1958/69 Тираж 623 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., n. 4/5

Филиал ППП Патент", r. Ужгород, ул. Проектная, 4