Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советсиик

Соцнаристмчесиик

Республик

ОП ИСАНИЕ

ИЗЬВРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< >898503 (бт ) Дополнительное к авт. саид-ву (22) Заявлено 16.05.80 (2l ) 2925787/18-24 с присоединением заявки М(23 } Приоритет

Опубликовано 15.01.82. Бюллетень М 2

Дата опубликования описания 15.01.82 (5! )М. Кд.

G 11 С 11/OO

3Ьеудврстааииый комитат

СССР дв делам иаабрвтеиий и открнтий

{ 53 ) УД К 68 1.327 (088.8) (72) Авторь1 изобретения

Г; Б. Энтин и Г, H. Острась (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам и может быть использовано в вычиспитепьных системах, содержащих запоминающие устройства с произвольной выборкой чисел.

Известно запоминающее устройство, содержащее накопитель на феррит овых сердечниках, адресный блок, усипитепи очи» тывания, формирователи токов запрета, соединенную с разрядными обмотками накопителя, регистр числа и блок управления (11 .

Недостатком этого устройства являет ся низкая надежность.

Наиболее близким техническим решени1S ем к изобретению является запоминающее устройство, содержащее накопитепь, соединенный с выходами двухпопярных формирователей тока запрета, с усилителями воспроизведения и адресным блоком, блок управления, соединенный с двухпопярными формирователями тока запрета;. с усилителями воспроизведения н регистром числа, выход которого подключен - к

2 блоку приема и выдачи кодов, блок связи, соединенный с адресным блоком. Кроме того, оно содержит допопнитепьный (управляющий) разряд в накопителе, соеди-. ненный со входом усилителя воспроизведения допопнитепьного (управпяюшего) разряда и выходом однопопярного формирователя тока запрета (управляющего разряда), причем выход усилителя воспроизведения дополните пьного (управпяюшего) разряда подключен к блоку управления, выход которого соединен со входом однополярного формирователя тока запрета (управляющего разряда) Г2).

Недостатком этого устройства является низкая надежность вследствие по- вышенного потребления MQIHHocTH большим числом возбуждаемых одновременно формирователей тока запрета.

Uemь изобретения - повышение падеж ности запоминающего устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее ацресный блок, формирователи тока

3 8985 запрета, усипители, регистр числа, блок управпения, бнок ввода-вывода данных и накопитель, адресные входы которого соединены с выходами адресного бпока, а информационные входы и выходы под» кпючены соответственно к выходам одних из формирователей тока запрета и ко входам одних из усипителей, выходы которых подключены ко входам регистра числа, управпяюшие вход и выходы накопи-0 тепя соединены соответственно с выходом другого формироватепя тока запрета и со входами другого усипитепя, управляющие входы усилитепей, одних из формирователей тока запрета и регистра чис-1 ла подключены к выходу бпока управпения, введены триггер, дешифратор, группы элементов И. и элементы НЕ, причем входы эпементов И первой группы соединены с прямыми выходами регистра числа, а управпяюшие входы подкпючены к прямому выходу триггера, инверсный выход которого соединен с управпяющими входами энементов И второй группы, входы которых подкпючены к инверсным выходам регистра чиспа, выходы эпементов И первой и второй групп соединены со входами блока ввод-вывода данных, единичный и нупевой входы триггера подкпючеиы соответственно к выходу другого усипитепя и к выходу блока управпения, входы эпементов И третьей группы соединены с выходами блока ввода-вывода данных и входами элементов НЕ, выходы которых подкпючены ко входам дешифратора и элементов И четвертой группы, управпяюшие входы которых соединены со входом другого формироватепя тока запрета и первым выходом дешифратора, второй выход которого подключен к управпяюшим . входам элементов И третьей группы, вы40 ходы которых соединены с выходами элементов И четвертой группы и входами одних из формирователей тока запрета.

Ф

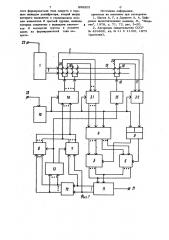

На фиг. 1 изображена функционапьная схема предложенного устройства; на фиг. 2 — пример выпопнения функционапьной схемы дешифратора для запоминающего устройства на четыре разряда.

Устройство (фиг. 1) содержит адресный блок 1, накопитель 2, усипители 3,1 и 3.2, регистр 4 чиспа, первую 5, вторую 6, третью 7 и четвертую 8 группы элементов И, триггер 9, бпок 10 управления, блок 11 ввода-вывода данных, элементы НЕ 12, дешифратор 13 и формироватепи 14 и 15 тока запрета, На фиг. 1 обозначены управпяюшие вход 16 и выходы 17, ферритовые сердечники 18, 03 4 адресные 19 и разрядные 20 шины накопителя, а также информационные входы (и выходы) 21, адресные 22 и управпяющие 23 входы устройства.

Входы элементов И 5 соединены с прямыми выходами регистра 4, а управляющие входы подключены к прямому выходу триггера 9. Инверсный выход триггера 9 соединен с управляющими входам ми эпементов И 6, входы которых подключены к инверсным выходам регистра 4. Выходы элементов И 5 и 6 соединены со входами бпока 11. Единичный и нулевой входы триггера 9 подкпючены соответственно к выходу усилителя 3.2 и к выходу блока 10. Входы эпементов

И 7 соединены с выходами блока 11 и входами эпементов НЕ 12, выходы которых подключены ко входам дешифратора

13 и элементов И 8. Управпяюшие входы элементов И 8 соединены со входом формирователя 15 и первым выходом дешифратора 13, второй выход которого подключен к унравпяюшим входам эпементов И 7. Выходы элементов И 7 и 8 соединены со входами формироватепей 14.

Дешифратор 13 содержит (фиг. 2) эпементы И 24-27, элемент ИЛИ 28 и эпе мент HE 29.

Выходы элементов И 24-27 соединены соответственно со входами элемента

ИЛИ 28, выход которого подключен ко входу эпемента HE 29. Первый вход первого элемента И 24 соединен с первыми входами третьего 26 и четвертого 27 элементов И и явяяется первым входом дешифратора 13. Второй вход эпемента

И 24 подкпючен к первому входу второго 25 и второму входу третьего 26 элементов И и явпяется вторым входом дешифратора 13. Третий вход эпемента И

24 соединен со вторыми входами второго 25 и четвертого 27 элементов И и явпяется третьим входом дешифратора

13. Третьи входы второго i 25, третьего 26 и четвертого 27 элементов И явпяются четвертым входом дешифратора

13. Выходы элемента НЕ 29 и эпемента ИЛИ 28 являются соответственно первым и вторым выходами дешифратора 13.

На фиг. 2 обозначены сигнапы А, В, С и 0 на входах дешифратора.

Устройство работает спедующим образом.

В исходном состоянии регистр 4 и триггер 9 находятся в нулевом состоянии. При записи на входы бпока 11 со входов устройства 21 поступает входная информация,.которая с выходов этого

7 898503 8 гого формирователя тока запрета и пер- Источники информации, вым выходом дешифратора, второй выход принятые во внимание при экспертизе которого подключен к управляющим вхо- 1. Шигин А. Г. и Дерюгин A. А. Бифдам элементов И третьей группы, выходы .ровые вычислительные машины, M., Энер.которых соединены с выходами элемен- к гия, 1978, с. 71, 72, рис. 3-20, тов И четвертой группы и входами 2. Авторское свидетельство СССР одних из формирователей тока за-;. % 429466, кл. б 11 С 11/00, 1973 п рета. (прототип).

898503

Фиг. 2

Составитепь Т. Зайаева

Редактор А. йопинич Техред А. Савка Корректор В, сутяга

Заказ 11958/69 Тираж 623 Подписное

ВНИИПИ Государственного комитета СССР по депам изобретений и открытий

113035, -Москва, Ж-35, Раушская наб., д. 4/5

Фипиап ППП "Патент, г, Ужгород, уп. Проектная, 4