Ассоциативная запоминающая матрица

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик п 898504 (6! ) flînîëíèòåëüíîå к авт. свид-ву— (22) Заявлено 28,04.80 (2l ) 2915187/18 24 с присоединением заявки №вЂ” (23) Приорнтет—

Опубликовано 15,01.82, Бюллетень № 2

Дата опубликования описания 18.01,82 (51) М. Кл.

G 11 С 15/00

ГооуАорственный комнтет

СССР оо долам нэобретеннй н открытнй (53) УДК 681. .327(088.8) Й. A. Тодуа, T. A. Клдиашвили, N. A. Абрамя

О. E. Жуковская и Н. A. Шемягин (72) Авторы изобретения

Тбилисский научно-исследовательский институт приборостроения и средств автоматизации Науч производственного объединения Элва" (71) Заявитель (54) АССОБИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИБА

Изобретение относится к запоминающим устройствам.

Известна ассоциативная запоминающая матрица, содержащая элементы цамяти с подключенными к ним шинами onроса, записи, считывания 11 .

Недостатком этой матрицы является сложность конструкции.

Наиболее близкой по технической сущности к предлагаемой является ассоциативная запоминающая матрица, содержащая строки и столбцы элементов ассоциативной памяти, каждый из которых содержит запоминающую ячейку, блок считывания, блок сравнения, две группы блоков выдачи, три группы входных элементов НЕ, а также входные шины поиска (записи), шины выбора строки, выходные шины считывания и шины результата поиска, позволяющие выполнить операции записи информации с выходных шин в любые элементы ассоциативной памяти и считывание из них информации, сравнения содержимого этих элементов с информацией на входных шинах и маскирование записи и сравнение определенных столбцов памяти (2).

Недостатком этой матрицы является отсутсивие контроля ее исправности, что снижает надежность матрицы.

Цель изобретения — повышение надежности матрицы.

Поставленная цель достигается тем, что в ассоциативную запоминающую матрицу, содержащую элементы памяти, причем входы элементов памяти, принадлежащих одноименному столбцу матрицы, подключены к соответствующим входным информационным и маскирующим шинам, а выходы - к выходным информационным шинам, входы элементов памяти, прина длежащйх од« ноименной строке матрицы, соединены с соответствующими шинами выборки строки, а выходы - с шинами результата поиска, введены логические блоки по числу столбцов матрицы и элемент И-НЕ, входы которого подключены к выходам логических

3 89850 блоков, 0 выхоп является контрольным выходом матрипк, одни из входов логических блоков подключены к управляющей шине, а другие — к соответствующим входным информационным шинам, маскирующим шинам и выходным информационным шинам.

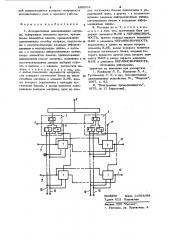

При этом логический блок целесообразно выполнять в виде блока, содержащего элементы И-НЕ и НЕРАВНОЗНАЧНОСТЬ, причем выходы первого элемента И HE u элемента НЕРАВНОЗНАЧНОСТЬ подключены к одним из входов второго элемента

И-НЕ, выход которого является выходом .логического блока„ входами которого являются другой вход второго элемента

И-НЕ и входы первого элемента И-HE u элемента. НЕРАВНОЗНАЧНОСТЬ, На чертеже представлена структурная схема ассоциативной запоминающей матрицы. 30

Матрицы содержат элементы памяти 1, логические блоки 2 по числу столбцов матрицы, состоящие из первого элемента

И-НЕ 3, элемента НЕРАВНОЗНАЧНОСТЬ

4 и второго элемента И HE 5, элемент

2$

И-НЕ 6, управляющую шину 7, испо льзуемую в режиме записи, шину 8 сиг: цала неисправности, шины 9 выборки строки, входные 10 и выходные 11 информационные шины, маскирующие шины

12 и щнны 13 результата поиска.

Входы элемента И HE 6 подключены к выходам блоков 2, а выход соединен с шиной 8 и является контрольным выходом матрицы, одни из входов блоков 2 подключены к шине 7, а другие - к соответствующим шинам 10, 11 и 12.

В каждом блоке 2 выходы элементов

И-НЕ 3 и НЕРАВНОЗНАЧНОСТЬ 4 подключены к одним из входов элемента

И-НЕ 5, выход которого является выходом блоке 2, входамн которого являются ,другой вход элемента И-НЕ 5 и входы элементов И HE 3 н НЕРАВНОЗНАЧНОСТЬ 4.

Матрица работает следующим образом.

B режиме записи на соответствующих информационной 10 и маскирующей 12 шинах может быть одна из трех следующих комбинаций логических сигналов:

1 "1 - запись с маскированием данного разрядочного столбца 1, "О«запись "1" в элемент ассоциативной памяти; 0", «1« - запись «О». Кроме того, в этом режиме на вход элемента HHB 5 всех логических блоков 2 по шине

7 подводится сигнал логической 1, который не мешает поступлению резуль4 4 татов сравнения с элементов И HE 3 и

НЕРАВНОЗНАЧНОСТЬ 4. В случае, если запись производится с маскированием данного разрядного столбца, с выхода элемента И-НЕ 3 снимается сигнал логического "0", который поступает на вход элемента И-НЕ 5. При этом игнорируется результат сравнения с элемента

НЕРАВНОЗНАЧНОСТЬ 4-, a с выхода элемента И-НЕ 5 снимается сигнал логической "1, который поступает на вход элемента И-НЕ 6 и означает нормальное функционирование элементов данного замаскированного разрядного столбца.

В режиме немаскированной записи

«1" или "0«в соответствии с таблицей истинности ассоциативного поля в случае правильной работы элементов памяти 1 информация на шинах; 11 совпадает с той, которая присутствует на соответствующих входных шинах 10, т.е. на входы элемента НЕРАВНОЗНАЧНОСТЬ 4 подается смешанная комбинация логических сигналов "1, «1" при записи «1" и "0", "0 при записи 0", а с его выхода сни: мается сигнал логического 0", который поступает на вход элемента И-HE 5, с выхода которого уровень логической 1« подается в элемент И-НЕ 6. Если соответствующий элемент памяти 1 работает неправильно, ro входы элемента НЕРАВНОЗНАЧНОСТЬ 4 поступает комбинация сигналов «1", «О", либо "0", "1", а с его выхода снимается сигнал логической 1", который подается на вход элемента И-HE

5, с выхода которого уровень логического «О" (так как на остальных входах данного элемента И-HE 5 присутствуют логические "l") подается в элемент ИНЕ 6, Если хотя бы на одном входе элемен- та И-НЕ 6 появляется сигнал логического «О, то по шине 8 выдает сигнал неисправности ассоциативной памяти (к шине 8 может быть подключен, например, индикатор неисправности).

В режиме отсутствия записи сигнал логического «О" по шине 7 подается на элемент H HE 5 всех логических блоков

2 и исключает ложное появление сигнала неисправности на шике 8, Предложенная матрица значительно повышает достоверность информации как хранимой, так и обрабатываемой в ней, повышает надежность систем, в которых применяется данная матрица.

Важным положительным качеством предложенной матрицы является то, что в

5 8985 ней осуществляется контроль исправности ассоциативного поля в процжсе работы.

Формула изобре гения

1, Ассоциативная запоминающая матриI ца, содержащая элементы памяти, причем входы элементов памяти, принадлежащие одноименному столбцу матрицы, подключе-1О ны к соответствующим входным информационным и маскирующим шинам, а выходы - к выходным информационным шинам, входы элементов памяти, принадлежащих одноименной строке матрицы, соединены с t5 соответствующими шинами выборки строки, а выходы — с шинамм результата поиска, отличающаяся тем, что, с целью повышения надежности матрицы, она содержит логические блоки цо числу 2о столбцов матрицы и элемент И-НЕ, входы которого подключены к выходам ло» гических блоков, а выход является контрольным выходом матрицы, одни из вхо04 6 дов логических блоков подключены к управляющей шине, а другие - к соответствующим входным информационным шинам, максируюшим шинам и выходным информационным шинам.

2. Матрица по и. 1, о т л и ч а юи а я с я тем, что, логический блок содержит элементы И-HE и НЕРАВНОЗНАЧНОСТЬ, причем выходы первого элемента

И-НЕ и элемента НЕРАВНОЗНАЧНОСТЬ подключены к одним из входов второго элемента И-НЕ, выход которого является выходом логического блока, входами которого являются другой вход второго элемента И-HE и входы первого элемента

И-HE и элемента НЕРАВНОЗНАЧНОСТЬ, Источники информации, принятые во внимание при экспертизе

1. Крайзмер Л. П., Бородаев G. А., :Гугенмахер Л. И. и др., Ассоциативные запоминающие устройства. N., "Энергия, 1967, с. 83.

2. "Электронная промышленнос гь, 1975, N ll (прототип).

ВНИИПИ Заказ 11958/69

Тираж 623 Подписное

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4