Устройство для контроля блоков памяти

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

ОП ИСАНИЕ»,898508

ИЗОБРЕТЕН Ыя

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22)Заявлено 23.05.80(21) 2921101у18 24 с присоединением заявки № (23) Приоритет

Опубликовано 15.01.82, Бюллетень № 2

Дата опубликования описания 18,0l..82 (51)M. е(л.

G 11 С 29/00 Ъсудврстееыный кемытет ееер

ыо делем ыэабретеный

ы открытый (53) УДК е81. .327(088.8)-.. (72) Автор изобретения

А. И. Савельев

Московский ордена Трудового Красного Знамени= текстильный институт (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля блоков памяти, содержащее схемы сравнения, числовой регистр, усилители чтения, вспомогательное запоминающее устройство и

5 блок управления. B этом устройстве пре дусмотрена подача импульсов стробирования в разное время относительно начала сигнала чтения М .

Недостатком этого устройства является невысокая точность контроля.

Наиболее близким техническим решением к изобретению является устройство для контроля блоков памяти, содержащее блок уцравления, вспомогательное запоминающее устройство, схемы сравнения, чи« словой регистр, усилители чтения, соединенные с формирователями строба Г23.

Недостатком этого устройства является невысокая точность контроля, так как в нем не предусматривается определение оптимального времени подачи импульсов стробирования на усилители чтения.

Бель изобретения - повышение точности контроля блоков памяти.

Поставленная цель достигается тем, что в устройство для контроля блоков памяпт, содержащее регистр числа, усиля« тели чтения, формирователь стробируюших сигналов, схему сравнения, блок управления и накопитель, причем выход формирователя стробирующих сигналов подключен к одним иэ входов усилителей чтения, другие входы которых являются информапионными входами устройства, а выходы соединены со входами регистра числа, выход которого подключен к первому входу схемы сравнения, второй вход и выход которой соединены соответственно с выходом и с первым входом накопи теля, второй вход которого подключен к первому выходу блока управления, третий вход накопителя и второй выход блока управления являются соответственно управляющими входом и выходом устройства, введены счетчик, формирователи управляющих сигналов, элемент задержки, эле3 89850 мент ИЛИ и элемент И, причем входы счетчика и элемента задержки подключены соответственно к третьему и четвертому выходам блока управления, выходы элемента задержки соединены соответственно со входами формирователей управляющих сигналов, выходы которых подключены к первым входам соответствующих элементов И, вторые входы которых соединены с выходом счетчика, входы эле- о мента ИЛИ подключены к выходам элементов И, а выход соединен со входом формирователя стробируюших сигналов.

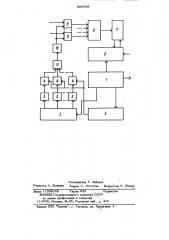

На чертеже изображена функциональная схема предложенного устройства.

Устройство содержит блок управления

1, элемент задержки 2, формирователи управляющих сигналов 3, элементы K 4:, счетчик 5, накопитель 6, схему сравнения 7, регистр числа 8, усилители чтения 9, формирователь стробируюших сигналов 10 и элемент ИЛИ 11. Выход формирователя 10 подключен к одним из входов усилителей 9, другие входы которых являются информационными входами устройства, а выходы соединены со входами регистра 8. Выход регистра 8 подключен к первому входу схемы сравнения 7, второй вход и выход которой соединены соответственно с выходом н с первым входом накопителя 6, второй вход которого подключен к первому выходу блока управления 1. Третий вход накопителя 6 и второй выход блока управления

1 являются соответственно управляющими входом и выходом устройства. Входы

3$ счетчика 5 и элемента задержки 2 подключены соответственно к третьему и к четвертому выходам блока управления

Выходы элемента задержки 2 соеди40 нены соответственно со входами формиро;вателей 3, выходы которых подключены

1 ,к первым входам соответствующих элементов И 4, вторые входы которых соединены с выходом счетчика б. Входы элемента ИЛИ 11 подключены к выходам элементов И 4, а выход соединен со входом формирователя 10. Информационные входы и управляющие вход и выход устройства подключаются к соответствующим выходам и входу контролируемого блока памяти (на чертеже не показан). Накопитель 6 является накопителем полупостоянного типа, Устройство работает . следующим образом.

Предварительно в накопитель 6 запи- 5$ сываются те же коды чисел и по тем же адресам, что и в контролируемый блок памяти, 8 4

По сигналу из блока управления l происходит считывание информации по очередному адресу из проверяемого блока памяти. В это же время из блока управления 1 поступает импульс тока на вход элемента задержки 2 и на запуск счетчика G. В соответствии с кодом числа, хранящегося в данный момент в счетчике 5, открывается один из элементов

И 4, например первый справа элемант И

4. При этом с соответствующего выхода элемента задержки 2 сигнал, сформированный соответствующим формирователем

3, проходит через элемент И 4 и элемент

ИЛИ l l на вход формирователя 10, который вырабатывает импульс стробирования, поступающий на первые входы усилителей 9 в момент времени, определяемый задержкой прохождения сигнала на элементе задержки 2. Считанное число из проверяемого блока памяти после усиления и стробирования поступает на ре.гистр 8, а затем на первый вход. схемы сравнения 7, на второй вход которой приходит код того же числа из накопителя

6, При совпадении или несовпадении кодов чисел в накопитель 6 записывается соответствующий сигнал. Затем из блока управления 1 подаются очередные сигналы опроса проверяемого блока памяти запуска счетчика 5 и сигнал на вход элемента задержки 2. В соответствии с кодом числа, хранящегося в данный момент в счетчике 6, открывается другой элемент

И 4 для прохождения сигнала на запуск формирователя 10, в результате чего стробирукиций сигнал смещается по времени относительно предыдущего стробируюшего сигнала.

Этот процесс опроса проверяемого блока памяти по одному и тому же адресу, но с воспроизведением сигналов чтения по смещенному стробирующему сигналу может проводиться несколько раз, что определяется техническими требованиями к информационной надежности проверяемого блока памяти и количеством выходов элемента задержки 2, количеством формирователей управляющих сигналов 3 и элементов И 4.. Режимы проверки могут быть установлены с помощью блока управления 1. Такими режимами могут быть, во-первых, режимы последовательной проверки безошибочного считывания всех чисел из проверяемого блока памяти при подаче сигнала стробирования в одно и то же время, а затем введение аналогичной проверки при последователь-ном смешении по времени стробирующе8988 го сигнала, а, во-вторых, смешение по времени стробирующего сигнала при многократном чтении числа по одному и тому же адресу, что позволяет в обоих случаях выбрать оптимальное время стробирования и в результате повысить точность контроля блоха памяти.

Технико-економическое;преимушество предложенного устройства заключается в обеспечении более высокой, цо сравнению с известным точности контроля, достигаемой за счет выбора оптимального време,ни стробирования сигнала чтения.

Формул а изобретения

Устройство для контроля блоков памяти, содержащее регистр числа, усилители чтения, формирователь стробируюших сигналов, схему сравнения, блок уп- 20 равления и накопитель, причем выход формирователя стробируюших сигналов подключен к одним из входов усилителей чтения, другие входы которых являются информационными входами устройства, а выходы соединены со входами регистра числа, выход которого подключен к первому входу схемы сравнения, второй вход и выход которой соединены соответственно с выходом и с первым входом на- ©

08 Ь копителя, второй вход которого подключен к первому выходу блока управления, третий вход накопителя и второй выход блока управления являются соответственно управляющими входом и выходом устройства, о т л и ч а ю ш е е с я тем, что, с целью повышения точности контроля, оно содержит счетчик, формировате-. ли управляющих сигналов, элемент за1 держки, элемент ИЛИ и элементы И, причем входы счетчика и элемента задержки подключены соответственно к третьему и к четвертому выходам блока управления, выходы элемента задержки соединены соответственно со входами формирователей управляющих сигналом, ьыходы которых подключены к первым вхо:-.. дам соответствутощих элементов И, вторые входы которых соединены с выходом счетчика, входы элемента ИЛИ нодключены к выходам элементов И, а выход соединен со входом формирователя стро бирующих сигналов.

Ис точники информапии, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 706882, кл. e ll С 29/00, l978, 2. Авторское свидетельство СССР

Иу 702412, кл. G, 1l С 29/ОО, 1978 (прототип) .

898508

Составитель Т. Зайцева

РедактоР A Aom Техред С. Мигунова KoppeKTop С. Шомак

Заказ 11958/69 Тираж 623 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

3. 13035, Москва, Ж-35, Раушская наб„g. 4/5

Филиал ППП Патент", r. Ужгород, ул. Проектная 4