Устройство для измерения флуктуационных характеристик узкополосных сигналов

Иллюстрации

Показать всеРеферат

Союз Советскик

Социапистичесиик

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН H $I

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ () ) )900203 (6! ) Дополнительное к авт. свид-ву (22) Заявлено 27,05,80 (21) 2930523/18-21 с присоединенйем заявки,)(й (23) ПриоритетОпубликовано 23 01 82 Бюллетень ¹ 3

Дата опубликования описания 28,01 82 (5()Ì. Кл.

G 01 Я 23/00

)Ьвударетво(нь(П кюнвтвт

СССР

Оо двлан кэобретевкй н оирыткй (53) УЙК 621 317, .3(088.8) (72) Авторы изобретения

А. В. Мулеванов, В. Г. Осипенко и В. П. Стенпк

Таганрогский радиотехнический институт им. В. Д. Калмыкова

- ...,1 (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ

ФЛУКТУАЦИОННЫХ ХАРАКТЕРИСТИК

УЗКОПОЛОСНЫХ СИГНАЛОВ

Изобретение относится к радиоизмерениям.

Известно устройство для измерения флуктуационных характеристик сигналов, содержащее смеситель, на один вход которого подан сигнал непосредственно, а на второй вход через перестраиваемую линию задержки, и амплитудный детектор„ вход которого соединен с выходом смесителя (.1)

Недостатками данного устройства являВгся малое быстродействие и необходимость в дополнительных вычислительных операциях.

Наиболее близким к предлагаемому

15 по технической сущности и достигаемому результату является устройство, содержащее первый перемножитель, на входы которого поступает исследуемый сигнал и опорный сигнал, второй и третий перемножители, первые входы которых лодключены к выходу первого перемножителя, выходы которых через фильтры соединены с входами блоков вычисления производных, выходы и входы которых соединены с входами блока вычисления частоты, выход которого подключен к индикатору 2

Однако устройство не обеспечивает

)1остаточной точности.

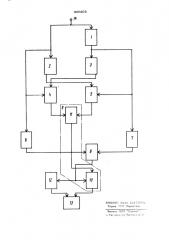

11ель изобретения — повышение точности, Поставленная цель достигается тем, что в устройство для измерения флуктуаыионных характеристик узкополосных сигналов, содержащее два блока вычисления нроиэводной, два перемножителя, первый вход одного из которых соединен с входной шиной, блок вычисления частоты, выход которого соединен с входом индикатора, введены линия задержки, два квадратора, блок извлечения квадратного корня н сумматор, один вход которого чере. -) первый квадратор соединен с входом первого блока вычисления производной и с входной шиной, а второй вход сумматора через второй квадратор соединен с первым входом второго перемножителя и входом второго блока вычисле3 90020 ния производной, а выход сумматора соединен с первым входом блока вычисления частоты непосредственно, а со вторым входом индикатора через блок извлечения квадратного корня, паничем вход второго блока вычисления производной соединен с входной шиной через линик задержки, выходы блоков вычисления производной перекрестно подклкчены ко вторым входам перемножителей, выходы которых соединены со вторым и третьим входами блока вычисления частоты, Кроме того, блок вычисления частоты содержит блок сравнения и вычитатель, входы которого соединены со вторым и третьим входами блока, а выход которогс подключен к первому входу блока сравнения, второй вход которого соединен с первым входом блока вычисления частоты, выход которого соединен с выходом бло- @ ка сравнения, На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство содержит линию 1 задерж- д ! ки на четверть периода сигнала, блоки

2 и 3 вычисления производной, перемножители 4 и 5, квадраторы 6 и 7, сумматор 8, блок 9 вычисления частоты, состоящий из блока 10 сравнения напря- и жений и вычитателя 11, блок 12 вычисления квадра тног о корня и индика тор 13.

Входной сигнал подан на входную шину 14.

Устройство работает следующим образом.

Исследуемый сигнал

ИЮ - АМ сааб(д.t + tH)3 поступает на вход линии 1 задержки, 40 которая задерживает его на четверть периода несущей частоты, в результате чего на ее выходе образуется колебание

V(t) = AЮ М 1)ю ++УИ)) квадрат квадратором 6 и в виде V2 (t) поступает на первый вход сумматора

В результате этого напряжение на выходе сумматора 8 поопорционально величине

0 (t ) + 0 (t ). Палее оно поступает в

2 2 блок 12 извлечения корня, выходное напряжение которого пропорционально амплиту-- °

1t l = жение с выхода блока 12 поступает на второй вход индикатора 13,;в котором

4 вычисляются флуктуационные характеристики амплитуды сигнала.

Одновременно исследуемый сигнал U(t) поступает на вход блока 2 вычисления производной, выходное напряжение котоt рого пропорционально величине q (t) „еступает на второй вход перемножителя 5, и на первый вход второго перемножителя 4. Задержанный сигнал V(t) поступает на вход блока 3, выходное напряжение 1 которого пропорциональное величине Ч Ю

L поступает на вход перемножителя 4, и на вход перемножителя 5. В результате этого, выходное напряжение перемножи а. теля 4 пропооциональное величине0():Ч () поступает на вход вычитателя 11, а выходное напряжение перемножителя 5 пооI порциональное величине0 (t) V(t) поступает на второй вход вычитателя 11. Выходное напряжение вычитателя 11 пропорциональное величине Ll(t) V (4)-U (t) V(t) поступает на первый вход блока 10, на второй вход которого поступает напрямжние пропорциональное величине0 (/ ч М с выхода сумматора 8. Поэтому выходное напряжение блока 10 пропорциональное величине мгновенной частоты сигнала

u O) « - u (t ) V й) А (Ц— поступает на вход

u2(t) +Ч2 (g) индикатора 13, в котором вычисляются и регистрируются флуктуационные характеристики частоты.

Формула изобретения

Из этих сигналов могут быть определены однозначно амплитуда и мгновенная частота в виде

АИ) =

df

u)(t) = — . ай

Поэтому, исслеу чемый сигнал U (Ф ) возводится в квадрат квадратором 7 и в виде V (г) поступает на второй вход

2 сумматора 8, а задержанный линией 3 задержки сигнал V (1 ) возводится в

1. Устройство для измерения флуктуашюнных характеристик узкополосных сигналов, содержашее два блока вычисления производной, два перемножителя, первый вход одного из которых соединен с входной шиной, блок вычисления частоты, выход которого соединен с входом индикатора, о т л и ч а ю ш е е с я тем, что, с целью повышения точности, в него введены линия задержки, два квадратора, блок извлечения квадратного корня и сумматор, один вход которого через первый квадратор соединен с вхо90 дом первого блока вычисления производной н с входной шиной, а втор и вход сумматора через второй и@адратор соединен с первым входом второго перемножителя и входом второго блока вычисления производной, а выход сумматора соединен с первым входом блока вычисления частоты непосредственно, а со вторым входом индикатора через блок извлечения квадратного корня, причем вход второго блока вычисления производной соединен с входной шиной через

I линию задержки выходы блоков вычисления производной нерекрестно подключены ко вторым входам перемножителей, вы ходы которых соединены со вторым и третьим входами блока вычисления . частоты.

0203 4

2. Устройство по и. 1, о т л и ч à юш е е с я тем, чо блок вычисления частоты содержит блок сравнения и вычитатель, входы которого соединены со

5 вторым и третьим входами блока, а выход которого подключен к первому входу блока сравнения, второй вход которого соединен с первым входом блока вычислМ ния частоты, выход которого соединен с выходом блока сравнения.

Источники информации, принятые во внимание при экспертизе

1. Берштейн И. Л. Флуктуации амплитуды и фазы лампового генератора.

Изв. AH СССР, сер. физическая, 1950, 14, с. 145.

2. "Радиотехника и электроника .

Т. "Õ"Ì 1979, М 5, с. 962.