Цифровой коррелятор

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

В,Д. Анисимов, В.А, Грачев и Е.H. Ли ман (71) Заявитель (54) ЦИФРОВОЙ КОРРЕЛЯТОР

Изобретение относится к вычислительной технике и предназначено для взаимно корреляционной обработки эхосигналов.

Измерение взаимно корреляционной функции (ВКФ) между входным и онорным сигналами в реальном масштабе времени требует обработки всего массива

N выборок (определяемого сложностью сигнала и точностньии параметрами измерения) за время между двумя сосед10 ними выборками, поступающими на вход коррелятора. Й выборок входного сигнала и N выборок опорного сигнала попарно (Й пар выборок) поступают на

Ij умножитель, где перемножы тся, а ре- зультат перемножения суммируется в накапливающем сумматоре, который усредняет результат перемножения на интервале длительности сигнала(К выборок). Таким образом, при большом количестве И и малом интервале между входньии выборками возникает сложность практической реализации цифро-,. вых корреляторов, работающих в реаль ном масштабе времени.

Быстродействие коррелятора опреде ляется в основном быстродействием умножителя, как наиболее сложного и трудоемкого узла.

Известен многоканальный коррелятор, содержащий цифровую линию задержки, цифровые блоки умножения, дешифратор, коммутаторы и интеграторы.

С целью повышения быстродействия циф» ровые блоки умножения умножают один отсчет входного сигнала на коды, рав ные уровням квантования другого (опорного) сигнала. Коррелятор позволяет одновременно вычислять несколько эна+ чений ординат ВКФ и при этом, чем больше ординат он вычисляет одновременно, тем эффективнее его работа Elf .

° Однако в системах обнаружения сигHBJIoB (неизвестно время прихода отра женного сигнала) использование такогф коррелятора не эффективно, так как там требуется последовательное не3 9002

Прерывное вычисление ординат ВКФ, соответствующих определенным моментам времени. Использование одного канала такого коррелятора сводит на нет его

Преимущества и приводит к избыточности аппаратуры.

Наиболее близким по,технической сущности к предлагаемому изобретению является цифровой коррелятор, содержащий два цифровых устройства задерж- щ ки с памятями (УЗП), счетчик, соединенный с адресными входами обоих УЗП, умножитель, соединенный входами с выходами обоих "УЗП„ накапливающий сум.матор, соединенный входом с выходом д умножителя, и генератор импульсов (ГЙ), соединенный со счетчиком, умножителем и накапливаюцим сумматором 23 .

Недостатком коррелятора является то, что использование его в трактах обработки сигналов, работающих в реальном масштабе времени, ограничивается быстродействием умножителя (как наиболее сложного и трудоемкого узла). Параллелизация узла умножения ве- дет к значительному увеличению аппаратурных затра r, что при большом числе каналов в тракте обработки не всегда приемлемо.

Цель изобретения — повышение быст- родействия коррелятора при относи" велько незначительном увеличении аппаратуры и при неизменной точности вычисления.

Поставленная цель достигается тем, что в цифровой коррелятор, содержащий первый и второй блоки задержки, первые входы которых являются соответственно первым и вторым входами коррелятора, блок умножения, первый вход которого подключен к выходу первого блока задержки, второй вход которого подключен к выходу счетчика, генератор импульсов, первый выход которого соединен с управляилщим входом первого накапливающего сумматора, информаци онный вход которого -подключен к выбору блока умножения, введены элемент запрета, второй накапливающий сумматор, блок памяти, дешифратор, элемент И, сумматор н второй счетчик, вход которого соединен со вторым вы" ходом генератора импульсов, а выход подключен к первому входу сумматора, второй вход которого объединен со вхо- дом решифратора и подключен к выходу блока памяти, вход которого объединен с первым входом элемента И и соеди89 4 нен с третьим выходом генератора импульсов, выход дешифратора подключен ко второму входу элемента И, выход которого соединен с управляющим входом второго. накапливающего сумматора, с первым входом элемента запрета и со входом первого счетчика, выход сумматора соединен со вторым входом второго блока задержки, выход которого подключен к информационному входу второго накапливающего сумматора, выход которого соединен со вторым входом элемента запрета, выход которого подключен ко второму входу блока умножения.

Сущность изобретения заключается в группировании выборок входного сигнала в каждом цикле вычисления ордикаты ВКФ по принципу равенства значений, соответствующих им в данном цикле выборок опорного сигнала с последующим суммированием значений выборок в пределах групП и умножения результатов суммирования с соответствующим группе значением выборки опорного сигнала. Погрешность измерения ординаты ВКФ остается неизменной, что обусловлено свойствами коммутативности и дистрибутивности аргументов функции которая определяет алгоритмы вычисления ординаты ВКФ.

В опорном сигнале обязательно будут встречаться равные по значению выборки, если и > 2, где q — разрядность хода опорной выборки. При обработке сложных сигналов, когда Й достигает нескольких тысяч, а q не превьппает 4-8, количество групп ограничивается сверху величиной 2, а время, необходимое на вычисление одной ординаты, сокращается приблизительно в И/2> раз за счет уменьшения времени, необходимого для выполнения операций умножения.

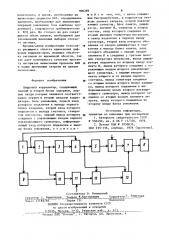

На чертеже представлена структурная схема предлагаемого устройства.

Коррелятор содержит последовательно .соединенные генератор 1 импульсов, блок 2 памяти, дешифратор 3, элемент И 4, первый счетчик 5, первый блок б задержки, блок 7 умножения и первый накапливающий сумматор 8, а также последовательно соединенные второй счетчик 9, сумматор !О, вто5 900209 рой блок 11 задержки, второй накапли- ние адресов ячеек памяти, как в самон вающий сумматор 12 и элемент 13 за- цикле так и кле, так и от цикла к циклу. С выпрета. Выход элемента И 4 соединен лока задержки значения выбос управляющим входом второго накаплн- рок « аняци

„ няциеся в опрошенных ячейках вающего сумматора 12 и с и авля и у р ющи S памяти, последовательно поступают во входои элемента 13 запрета, выход торо накапливающий сумматор 12, которого соединен со вторыи входом д они в пределах своих групп суими" блока 7 умножения. Второй выход гене- руются В ся. момент, соответствующий ратора 1 соединен со входом второго окончанию формирова рмирования группы, с бло счетчика 9, третий выход генератора 10 ка 2 наияти поступа поступает на дешифратор у соединен с управляющни входом перво- код "Оконч кончание -о-рмирования rpynnM1!. го накапливающего сумматора 8, вы- Дешнфрато 3 шн ратор выдает разрешающий по-. ход блока 2 памяти дополнительно со- тенциал на элемент И 4 через который единен со вторым входом сумматора 10 импульс с генератор I

1 с генератора проходит на первый выход генератора l импульсов IS вход счетчи а 5 счетчика, на управляющий вход дополнительно соединен со вторыи вхо- злеиента 13 запрета и на вход "Уст. дом элемента И 4.

Цифровой коррелятор работает сле- Элеиент 13 запрета по данному н; дующим образом. пульсу транслирует результат сумииВыборки входного сигнала после- 20 рования с накапливающего сумматора 1» довательно поступают в память блока 11 задержки, где каждая выборка хранится в течение Н циклов, а затем борок опорного сигнала нала, каждому иэ заменяется новой, вновь поступившей. которых соо в соответствует определенная

Таким образом, в памяти хранится И Ч группа входных б одних вы орок. Каждая иэ Ц

I текущих значений выборок входного сне- значений выборок ум орок умножается в блоке ени входных выборок в ала. В паузе между моментами поступг на сумму значений вхо х в ления в память блока ll задержки двух пределах группы. Счетчик 5 последовасоседних выборок входного сигнала осу. тельно по каждому аждому импульсу, поступаществляется групповой опрос всех Ч За ющеиу с выхо а выхода элеиента И 4, соотячеек памяти блока ll задержки (гз- ветствующег его окончанию формирования мять с произвольнм доступом) при по- группы выборок и суммирования в премощи счетчика 9, блока 2 памяти и делах данной группы фо рмнрует код сумматора 10. Ячейки опращюваются адреса ячейки памяти блока 6. Значегруппами, которые формируются по прин-, rrae выбоРки опорного сигнала осущестципу равенства значений соответству- вляет 0 онераций .умножения. Накаплнющих ии выборок опорного сигнала, вающий суьжатор 8 осуществляет суит.е. в калщой группе объединяются те MHpo»rnre и усреднение результатов выборки входного сигнала, которые в умножения. данком цикле умножаются на равные по,щ Hа первом выходе генератора 1 имзначению выборки опорного сигнала. пульсов формируется М+((1-1) нипульВ блоке 2 памяти хранятся и началь- сов синхронизирующих работу элеиенных кодов адресов ячеек памяти бло- та И 4 и осуществляющих считывание ка 11, объединенных по грунпаи и с блока 2 памяти, на втором. выходе ге(-1 кодов Ъкончания ф6рмирования 4з нератора I импульсов формируется ими группы, разделяющих группы. пульс, задающий код счетчика 9, соответствующий номеру цикла вычисления

Счетчик 9 фориирует код, соответру ци исления на тРетьем выходе генератора 1 форин ствующий номеру цикла вычислещюя на руется импульс, осуществляюций после сумматоре 10 текущий номер цикла вычисления очередной ординаты ВКф очии начальный код суммируются по моду- щение накапливающего сумматора В. лю И, а результат суммирования определяет адрес ячейки опроса. Таким об- В предлагаемом устройстве в каждом разом, записав в блок 2 памяти но цикле вычисления ВЕФ количество опегруппам начальные коды адресов (соот- раций умножения на блоке 7 умножения ветствующие формированию групп адре- равно 9 вместо и операций умножения в сов .для нулевого цикла вычисления ор- известном устройстве, т.е. на каждом динаты) -и, суммируя с ним текущий но- цикле время, необходимое на операции мер цикла, осуществляется фориирова- умножения, сокращается в К/Q раз.Сле

7 9002 довательно, и время, необходимое на вычисление ординаты ВКФ, определяемое временем, необходимым для выполнения операций умножения (как наиболее трудоемких), сокращается приблизительно в Й/Q раз. Во столько же раз сокращается объем памяти, необходимой для запоминаний значений выборок опорного сигнала.

Предлагаемое изобретение позволя-. )O ет расширить область применения цифровых корреляторов, ведущих обработку сигналов во временной области, так как дает возможность сочетать простоту алгоритма вычисления ордииаты ВКФ 15 и малые временные затраты на данные вычисления.

Формула изобретения

Цифровой коррелятор, содержащий первый и второй блоки задержки, первые входы которых являются соответст1венно первым и вторьи входами корре- 25 пятора, блок умножения, первмй вход ,которого подключен к выходу первого блока задержки, второй вход которого подклю ен к выходу счетчика, генератор импульсов, первьп1 выход которого 5О соединен с управляющим входом первого накапливающего сумматора, информационный вход которого подключен к выходу блока умножения, о т л и ч а ю—

89 8 шийся тем, что, с целью повышеЙия быстродействия, в коррелятор вве+ жены элемент запрета, второй накапливающий сумматор, блок памяти, дешифратор, элемент И, сумматор и второй счетчик, вход которого соединен со вторьм выходом генератора импульсов, а выход подключен к первому входу сумматора, второй вход которого объединен со входом дешифратора и подключен к выходу блока памяти, вход которого объединен с первым входом элемента И и соединен с третьим выходом генератора импульсов, выход дешифратора подключен ко второму входу элемента И, выход которого соединен с управлякж1им входом второго накапливающего сумматора, с первым входом элемента запрета и со входом первого счетчика, выход сумматора соединен со вторым входом второго блока задержки, выход которого подключен к информационному входу второго накапливающего сумматора, выход которого соединен со вторым входом элемента за,прета, выход которого подключен ко

|второму входу блока умножения.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

33 556450, кл. G 06 F 35/336, 1976.

2. Патент С333А 33 3950635, НКИ 235-156, опублик. 1976 (прототип).

Составитель В. Новинский едактор JI. Филиппова Техред Ж.Кастелевич Корректор Г. Решетник

Заказ 12183/66 Тираж 731 Подписное

ВШПШИ Государственного комитета СССР по делам изобретений и открытий

113035 Иосква 1К-35 Раушская наб. д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4