Число-импульсное линеаризующее устройство

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

А.И. Недашковский и А.В. Койнов

Ленинградский ордена Ленина политехнич ский институт им. M. И. Калинина (71) Заявитель (54) ЧИСЛО-ИМПУЛЬСНОЕ ЛИНЕАРИЗУЮЦЕЕ УСТРОЙСТВО

Кроме того, известные устройства не позволяют производить масштабирование, которое предполагается выполнять в аналогичных узлах, что менее точно и зависит от влияющих величин или требует больших аппаратурных затрат по сравнению с цифровым методом, либо масштабирование и линеариэация могут выполняться с использованием лишь целочисленных коэффициентов аппроксимации.

Наиболее близким по технической

Однако использование этих уст1$ ройств в многоканальных системах нецелесообразно, так как оно приводит к усложнению системы в связи с громоэдкостью построения многоканальных

20 устройств линеаризации, предназначенных для одновременного обслукивания датчиков, которые характеризуются различной степенью нелинейности.

Изобретение относится к измерительной технике и может найти применение при создании многоканальных информационных измерительных систем, предназначенных для измерения электрических и неэлектрических величин с использованием первичных преобразователей (датчиков), которые имеют нелинейную выходную характеристику.

Известны устройства линеаризации, преобразующие нелинейную выходную ха- т© рактеристику датчика в линейную путем ее кусочно-линейной аппроксимации 11 и 523. сущности к предлагаемому является устройство, содержащее делитель частоты, элемент И-ИЛИ, блок памяти, счетчик адреса и переключатель каналов, выход которого соединен с первым входом блока памяти, второй вход которого подключен к выходу счетчика адреса, вход которого соединен с первым выходом делителя частоты, второй выход которого подключен к первому входу элемента И-ИЛИ, выход которого является выходом устройства, вход дели90029 теля частоты является входом устройства, первый и второй входы переключателя каналов являются входами автоматической и ручной установки устройства ГЗ).

Недостаток известного устройства заключается в том, что входящее в его состав постоянное запоминающее устройство (ПЗУ) должно иметь большое число выходов, которое нропорциональ- 16 но числу формируемых на выходе устройства импульсов в пределах каждого участка аппроксимации. Это приводит к усложнению, удорожанию и снижению надежности ПЗУ и устройства в целом, 1S в также ограничивает воэможность исйользования ПЗУ, т.е. Уменьшает функ- циональные возможности устройства (например, сокращает число обслуживаемых устройством типов датчиков) или требует двойного и более увеличения числа однотипных ПЗУ.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что известное устройство, содержащее делитель частоты, элемент И-ИЛИ, блок памяти, счетчик адреса и переключатель каналов, выход которого соединен с первым входом блока памяти, второй вход которого подключен к выходу счетчика адреса, вход которого соединен с первым выходом делителя частоты, второй выход которого подключен к первому входу элемента И-ИЛИ, выход которого является выходом устройства, вход делителя частоты является входом устройства, первый и второй входы переключателя каналов являются входаж соответственно автомати40 ческой и ручной установки устройства, содержит реверсивный счетчик и управляемый генератор тактавйх импульсов, выход которого подключен к информационному входу реверсивного счетчика, выход которого соединен со вторьак входом элемента И-ИЛИ, первый выход делителя частоты подключен ко входу запуска управляемого генератора тактовых импульсов, управляющий выход Которого соединен с первым выходом блока памяти, второй выход которого соединен со входом записи реверсивного счетчика, вход режима работы которого подключен к третьему выходу блока памяти, а установочный вход реверсивного счетчика подключен к выходу переключателя каналов.

0 4

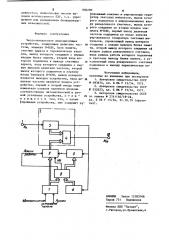

На чертеже представлена блок — схема предлагаемого устройства.

Устройство содержит вход I устройства, двоичный перемножитель 2, делитель 3 частоты, элемент И-ИЛИ 4, управляемый генератор 5 тактовых импульсов, счетчик 6 адреса, переключатель 7 каналов, блок 8 памяти (ПЗУ), реверсивньЖ счетчик 9 и выход 10 устройства.

Узлы и блоки линеаризукщего устройства имеют следующие функциональные связи. Число импульсов 11 нелинеаризованной и немасштабированной частоты fg поступает на вход 1 устройства и, следовательно, на вход двоичного.перемножителя 2, состоящего из делителя 3 частоты и элемента И-ИЛИ 4.

Импульсы с выхода делителя 3 частоты поступают на вход запуска управляемого генератора 5 тактовых импульсов и вход счетчика 6 адреса. Сигналы с выходов счетчика 6 и переключателй 7 каналов определяют формирование командных сигналов на выходах ПЗУ в пределах каждого участка аппроксимации.

Импульс на выходе делителя 3 частоты формирует начало очередного участка аппроксимации. При этом импульса— ми с выхода управляемого генератора 5, тактовых импульсов, число которых определяется сигналами, подаваемыми с выходов блока 8 на его управляющие входы, счетчик 9 изменяет свое состояние. В зависимости от сигнала, который подается на вход режима работы с выхода блока 8, число в счетчике 9 увеличивается или уменьшается.

Кодом с выходов переключателя 7 каналов при определенном сигнале (1 или 0} на входе управления записью исходного состояния, формируемом на выходе блока 8, производится начальная установка (НУ) счетчика 9 в состояние, соответствующее первому участку анпроксимации.Состояние счетчика на границе двух участков аппроксимации изменяется на наибольшее значение.

Число импульсов Й линеаризованной и масштабированной частоты Ч1 поступает на выход 10 устройства. Масштабирование одновременно с определением длины участка по аргументу выполняет делитель 3 частоты.

Таким образом, предлагаемое число-импульсное линеаризующее устрой— ство характеризуется повышенной на—

9002 дежностью, минимальным числом выходов используемого ПЗУ, т.е. упрощением или расширением функциональных возможностей.

Формула изобретения

Число-импульсное линеаризующее устройство, содержащее делитель час- 16 тоты, элемент И-ИЛИ, блок памяти, счетчик адреса н переключатель каналов, выход которого соединен с первым входом блока памяти, второй вход которого подключен к выходу счетчика 1з адреса, вход которого соединен с нервым выходом делителя частоты, второй выход которого подключен к первому входу элемента И-ИЛИ, выход которого является выходом устройства, вход де- щ лителя частоты является входом устройства, первый и второй входы переключателя каналов являются входами соответственно автоматической и ручной установки устройства, о т л и — 25 ч а ю щ е е с я тем, что, с целью прощения устройства, оно содержит ре90 d

Версывный- чепчик- -и -yapaanseragA гене

1 атор тактовых импульсов, выход кото» рого подключен к информационному входу реверсивного счетчика, выход кото рого соединен со вторьи входом элемента И-ИЛИ, первый выход делителя частоты подключен ко входу запуска управляемого генератора тактовых импульсов, управляющий выход которого соединен с первым выходом блока паня+ ти, второй выход которого соединен с4 входом записи реверсивного счетчика, вход режима работы которого подключев к третьему выходу блока памяти, а установочный вход реверсивного счетчикв подключен к выходу переключателя каналов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ф 483674, кл. G 06 F 15/34, !975.

2. Авторское свидетельство СССР

Р 552623, кл. G 06 F 15/34, 1977.

3. Авторское свидетельство СССР по заявке 9 274)146/18-24, кл. 6 06 F 1 5/34, 31.)0 .79 (прототип).

НИИПИ Заказ 12183/66 аж 73! Подписное

Филиал ППП Патент г.ужгород,ул.Проектная,4