Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскнк

Социалнстическнк

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. сеид-ву (22) Заявлено 28. 05. 80 (2! ) 2931722/18-24 (51)M. Кл. с присоедииеииект заявки рв

С 11 С 15/00

Государственный коиитет

СССР (23) Приоритет ло делам иаебретвиий и открытий

Онубликоваио 23.01 82 Бктллетеиь М 3

Дата опубликования описания 25.01.82 (53) УДК 681.

327(088.8) Д.А. Тодуа, T.À. Клдиашвили, M.À. Абрамян, А.К. Иманов, О.Е. Жуковская, Н.А. Шемягин, Н.С. Зедгинидэе и Н.Ш. Кобахидзе т

Тбилисский научно-исследовательский HHcTlilTQT приборостроения и средств автоматизации . (72) Авторы изобретения (71) Заявитель (54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области запоминающих устройств.

Известно ассоциативное запоминающее устройство (АЗУ), содержащее за" поминающие магнитные элементы и блоки управления (11.

Недостатком этого устройства являются ограниченные функциональные возможности.

Наиболее близким техническим ре10 шением к изобретению является АЗУ, содержащее строки и столбцы элементов ассоциативной памяти, каждый из которых содержит запоминающую ячейку, блок считывания, блок сравнения, две

1% группы блоков выдачи, три группы входных элементов НЕ, rpynny элементов

И-HE для разрешения выбора строк, логические блоки на каждый столбец, со" держащие в себе два элемента И-НЕ и элемент НЕ, два элемента И-НЕ для выбора режима работы, а также входные шины режимов чтения, записи, поиска, информационные и маскирующие шины, шины выбора строки, входные шины счи" тывания слова и шины результата поиска (21.

Недостатком этого устройства является невозможность разделения матрицы ассоциативных элементов памяти на группы и отсутствие тактируемого сигнала обращения к АЗУ, в результате чего снижается надежность устройства.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в АЗУ, содержащее матрицу ассоциативных элементов памяти, группы элементов И-НЕ, элементы НЕ и элементы И-НЕ, выходы которых подключены ко входам шин выбора строк матрицы ассоциативных элементов памяти, а выходы элементов И-НЕ группы - ко входам шин считывания, причем первые входы одних из элементов И-НЕ группы соединены со входами элементов НЕ, а первые входы других элементов И-НЕ группы - с выходами элементов НЕ, 900315

19

15 первые входы элементов И-НЕ, входы элементов НЕ и вторые входы элементов И-НЕ групп являются соответственно адресными, информационными и маскирующими входами устройства, введены логические блоки, элемент ИЛИ-НЕ и элементы И, выходы которых подключены ко входам элемента ИЛИ-НЕ, вйход которого соединен со вторыми входами элементов И-НЕ, первые и вторые входы логических блоков подключены соответственно к первым входам элементов И, а выходы - к третьим входам элементов И-НЕ групп, вторые входы элементов И, третьи и четвертые входы логических блоков являются управляющими входами устройства.

При этом каждый логический блок целесообразно выполнить содержащим элементы И и элемент ИЛИ-НЕ, входы которого подключены соответственно к выходам элементов И, а выход является выходом логического блока, входами которого с первого по четвер" тый являются сООтветственнО вхОд пер»15

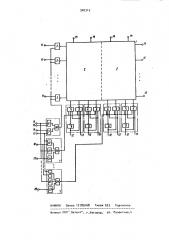

soro элемента И, первый и второй входы второго и вход третьего элементов И. ,На чертеже изображена структурная схема предложенного устройства.

Устройство содержит матрицу 1 ас" социативных элементов 2 памяти, элементы И-НЕ 3, группы элементов И-КЕ

4 и 5, элементы НЕ 6, логические блоки 7, первый 8 и второй 9 элементы И и элемент ИЛИ-НЕ 10. На чертеже обозначены адресные 11, информационные

12 и маскирующие 13 входы, информационные выходы 14 и выходы 15 результата опроса, входы чтения 16„ записи 17, опроса 18, обращения l9 и вы" бора 20 ассоциативных элементов памяти устройства.

Выходы элементов И 8 и 9 подключены ко входам элемента ИЛИ-НЕ 10, 45 выход которого соединен со вторыми входами элементов И-ИЕ 3. Первые и вторые входа логических блоков 7 подключены соответственно к входам первого 8 и второго 9 элементов И, а выходы - к третьим входам элементов И-НЕ 4 и 5 групп, Входы элементов И. 8 и 9, третьи и четвертые входы блоков 7 являются соответственно входами обращения 19„ 55 чтения 16, записи l7, опроса 18 и выбора 20 ассоциативных элементов па" мяти устройства. При этом логическим

4 блок 7 выполнен содержащим элементы И 21-23, выходы которых подключены соответственно ко входам элемента ИЛИ-НЕ 24, выход которого является выходом блока 7. Вход первого элемента И 2l первый и второй входы второго 22 и вход третьего 23 элементов И являются соответственно входами с первого по четвертый блока 7.

Устройство работает следующим образом.

Во всех режимах работы (запись, чтение, опрос) сигнал обращения осуществляет общую синхронизацию работы устройства, поэтому уровень логического "0" на вход 19 обращения приходит после подачи сигналов информации и маски на входы 12 и 13 и управляющих сигналов режимов работы. Таким образом, сигнал обращения приходит

Ьпоследним и снимается первым. При отсутствии сигнала обращения поле ассоциативной памяти находится в состоянии покоя, т.е. на всех входах матрицы присутствует уровень логической "1". В работе устройства активным считается уровень логического"0".

В режиме чтения уровень логического "0" на входах чтения 16 и обращения 19 разреаает выбор адреса строки матрицы 1 ассоциативных элементов памяти. Композиция значений на входах логических блоков 7 (логическая "1" на входах опроса 18 и записи 17) такова, что с выходов этих блоков 7 поступает уровень логического "0", который запрещает прохождение сигналов информации и маски и обеспечивает уровень логической "1" на информационных и маскирующих входах матрицы 1.

В режиме записи уровень логического "0" на входах записи 17 и обращения l9, так же как при чтении, разревает выбор адреса строки.

Однако запись в любую группу или несколько групп ассоциативных элементов памяти по одной или нескольким выбранным строкам. матрицы 1 осуществляется подачей сигнала логического "0" по соответствующему входу

20. При этом по входу 17 записи подается сигнал логического "0" на первые входы элементов И 22, а на вторые входы - сигнал логической "1" со входа 18 опроса, так как одновременно не могут быть установлены два режима работы устройства. На

И-НЕ, выходы которых подключены ко входам шин выбора строк матрицы ассоциативных элементов памяти, и выходы элементов И-НЕ группы - ко входам шин считывания, причем первые входы одних их элементов И-Н: группы соединены со входами элементов НЕ, а первые входы других элементов И-НЕ группыс выходами элементов НЕ, первые входы элементов И-НЕ, входы элементов НЕ и вторые входы элементов И-НЕ групп являются соответственно адресными, информационными и маскирующими входами устройства, о т л и ч а ю щ е е— с я тем, что, с целью повышения надежности устройства, оно содержит логические блоки, элемент ИЛИ-HE и элемент И, выходы которых подключены ко входам элемента ИЛИ-НЕ, выход которого соединен со вторыми входами элементов И-НЕ, первые и вторые входы логических блоков подключены соответственно к первым входам элементов И, а выходы - к третьим входам элементов И-HE групп, вторые входы элементов И, третьи и четвертые входы логических блоков являются управляющими входами устройства.

2. Устройство по и. 1, о т л ич а а щ е е с я тем, что каждый ло" гический блок содержит элементы И и элемент ИЛИ-НЕ, входы которого подключены соответственно .к выходам элементов И, а выход является выходом логического блока, входами которого с первого по четвертый являются соответственно вход первого элемента И, первый и второй входы второго и вход третьего элементов И.

5 90031 входы элементов И 21 поступает сигнал логического "0" со входа 19.

При этом на выходах элементов И 2123 выбранного блока 7 установятся сигналы логического "0", а на выходе элемента ИЛИ-НЕ 24 — сигнал логической "1", который подается на третьи входы элементов И 4 и 5 групп, соответствующей выбранным ассоциативным элементам памяти матрицы l, и 10 разрешает запись информации в выбранные элементы 2.

На входе 20 не выбранного блока 7 присутствует сигнал логической Ч", и с выхода элемента ИЛИ-НЕ 24 этого 1 блока 7 снимается сигнал логического, "0", который блокирует информационные 12 и маскирующие 13 входы, соответствующие не выбранным ассоциативным элементам 2 памяти матрицы 1, ис- 20 ключая таким образом ложную запись информации.

В опросе чтения комбинация сигналов логических "1" на входах 16 и 17 блокирует выбор адреса по входам 11.

Выбор ассоциативных элементов 2 памяти матрицы 1 для считывания из них информации происходит так же,как в режиме записи.

Технико-экономическое преимущество предложенного устройства заключается в его более широких, по сравнению с известным, функциональных возможностях за счет выполнения в нем логических операций, обеспечиваемых 3$ путем возможного разделения матрицы на группы ассоциативных элементов памяти и введения тактируемого сигнала обращения к устройству.

Формула изобретения

1. Ассоциативное запоминающее устройство, содержащее матрицу ассоциа- 43 тивных элементов памяти, группы элементов И-НЕ, элементы НЕ и элементы

Источники информации, принятые во внимание при экспертизе

1. Заявка Японии < 52-7903, кл 97(7)С, опублик. 1975.

2. Авторское свидетельство СССР по заявке 2814119/18-24, кл. G ..11 С 15/00, 1979 (прототип).