Преобразователь частоты в код

Иллюстрации

Показать всеРеферат

Союз Советскнн

Соцнапнстнческнн

Республик

i900447 (6I } Дополнительное к авт. свмд-ey— (22)Заявлено 290580 (2е) 2932683/18-21 с присоедниеннеке заявки М— (23) Приорнтет—

Опубликовано 2301.82. Втоллетень М 3

Дата опубликования оиисання 2301.82, 1)M. Кл.

Н 03 К 13/20

ГоеударстеенныИ «оннтет

СССР но делан нзабретеннй и открытн11

) УД (621 ° 317 (088.8) (72) Авторы, изобретения

3ÄK. Скворцов и В.И. Бутенко (71) Заявитель

Вычислительный центр Сибирского отделения АН СССР (54) ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для преобразования частоты в код.

Известны преобразователи частоты в код, содержащие приемники информации, вычислитель частот, блок синхро.низации и реверсивный счетчик, подключенные к блоку управления (11 .

Однако в них невозможно преобразоФО ванне сигналов со случайной фазой .

Наиболее близким по технической сущности к изобретению является преобразователь, содержащий приемники информации, вычитатель частот, блок синхронизации, реверсивный счетчик, сумматор и интегратор, подключенные к блоку управления (2).

Недостатком-этого преобразователя является то, что его нельзя использовать для преобразования в код частоты сигнала со случайной фазой, так .как в нем вычитатель частот непосредственно связан со входом-реверсивного счетчика приращения частоты. При этом скачок входного сигнала, больший половины периода, приводит к на-. рушению соответствия между входным сигналом и его кодом в счетчике, поскольку вычитатель частот, являющийся детектором относительных фазовых сдвигов входного и восстановленного из кода сигналов,при указанных свя зях между элементами схемы дает инфор-. мацию лишь о знаке разности фаз указанных сигналов,по которому определяются единичные приращения частоты, Таким образом, реакция известного преобразователя на скачок фазы входного сигнала выражается в появлении переходного процесса, необходимого для восстановления соответствия между входным сигналом и его кодом, т.е. в течение переходного процесса код оказывается недостоверным.

Целью изобретения является расширение функциональных возможностей устройства при одновременном сокраВ начале кодирования счетчик 8 и интегратор 10 сбрасываются сигналами от блока 12 управления. Входной сигнал, поступающий от приемника 1 на вычитатели 2 и 3 частот и соответствующий i ìó циклу работы устройства (1 1,2,3,...), сравнивается по фазе с сигналом, поступающим на другие входы вычитателей частоты, восстановленным из кода, содержащегося в интеграторе 10. Восстановление сигнала из кода с помощью преобразователя 11 дает сигнал, соответствующий i-1-му циклу работы преобразователя, так как код частоты сформирован в предыдущих циклах. Сигналы преобразователя 11 на двух его выходах представляют меандры, сдвинутые по фазе на

Эь

Сигналы раэностной частоты с выходов вычитателя частот поступают на информационные входы блока синхронизации 4, тактирующие входы которого воспринимают сигнал от блока 12 управления . Синхронизированные с работой вычислительных блоков преобразователя сигналы раэностной частоты задерживаются на один цикл работы преобразователя в 0-триггерах 5 1 и 5=2.

Сумматоры 61 и 62 формируют приращения, разностной частоты и одновре-. менно определяют знак приращения: на выходе одного из сумматоров получаются положнтельнйе приращения разностной частоты, а на выходе второго сумматора — отрицательные приращения.

Работа сумматоров 61 и 6 2 может быть описана разностными уравне)(иями

3 90044 щекин времени преобразования и расширения диапазона преобразуемых частот, Поставленная цель достигается тем, что в преобразователь частоты в код, содержащий последовательно соединенные приемник информации и вычитатель частот, выход которого соединен с первым входом блока синхронизации, H последовательно соединенные реверсивный счетчик, сумматор, интегратор и 10 блок выхода информации, блок управления, первый, второй и третий выходы которого подключены соответственно к управляющим входам блока синхронизации, реверсивного счетчика и интег- 1 ратора, дополнительно введены преобразователь код — частота, вычитатель частот, для 0-триггера и три сумматора по модулю два, причем выход приемника информации соединен с первым входом дополнительного вычитателя частот, выход которого подключен ко второму входу блока синхронизации, пер вый выход которого подключен к первым входам первых б-триггера и сумматора по модуло два, второй выход блока синхронизации подключен к первым входам вторых О-триггера и сумматора по модулю два, вторые входы О-триггеров обьедииены и подключены к первому выходу блока управления, выходы первого и второго 0-триггеров соединены со вторыми входами соответственно второго и первого сумматоров по модулю два, выходы которых подключеИ ны непосредственно ко входам реверсивного счетчика и сумматора и через третий сумматор по модулю два — к запрещающим входам реверсивного счетчика к интегратора, выход которого чеP es преобразователь код-частота подклю40 чвн ко вторым входам вычитателей частот.

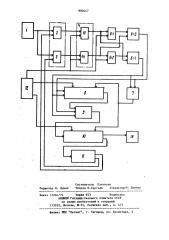

На чертеже представлена функцио,нальная схема преобразователя частоты s код.

1 -Преобразователь содержит последовательно соединенные приемник 1 информации, вычитатели 2 и 3 частот, блок 4 синхронизации, В-триггеры 5 1 и 52, сумматоры 6-1, 6-2,и 7 по модулю два.

Выходы двух сумматоров 61 и 6 2 под$0 ключены к соответствующим входам сумматора 7 по моду)ж два, входам реверсивного счетчика 8 и входам сумматора 9. Третий вход сумматора 9 соединен с выходом счетчика 8, а к выходу сум- матора 9 подк)ючен интегратор 10. Вы" ход сумматора 7 подключен к запрещающим входам счетчика 8 и интегратора

7 4

10. Преобразователь ll код — частота включен между выходом интегратора IO и входами вычитателей частот 2 и 3.

К выходам блока 12 управления подключены блок 4, 0-триггеры 51, 5 2, счетсчетчнк 8 и интегратор IO, Блок синхронизации 4 выполнен на двух 0"триггерах 13 и 14, К выходу интегратора 10

10 подключен блок 15 вывода информации связи с ЭВИ.

Преобразователь работает следующим образом. А (1) + А (j1) * +Ь;

)яМ

f (А (() + А,(I-1))щ»)» -Ь!

Формула изобретения

S 9004 где Al (i-1)t A (1) — состояния 0,1 на одном выходе блока 4 синхронизации в моменты времени 1-1, А (i-1), А (i) — состояния 0,1 на втором выходе блока 4 синхронизации; А — приращения часто- io ты с учетом их знака.

Приращения разностной частоты суммируются счетчиком 8, содержимое которого интегрируется по времени интегратором 10. Кроме того, интегратор

l0 интегрирует по времени приращения частоты, которые поступают в него, как и информация из счетчика, через сумматор 9. Добавление приращений 3О частоты в интегратор необходимо для устойчивой работы преобразователя гашения в нем колебаний.

С помощью сумматора 7 осуществляется запрет работы счетчика и интегра-33 тора при одновременном появлении приращений частоты разных знаков, а также при отсутствии приращений частоты.

При этом содержимое счетчика 8 и интегратора 10 не разрушается.

36

- После завершения переходного процесса, возникающего только при включении преобразователя, код в интеграторе 10 представляет код частоты входного сигнала, который вводится в ЭВМ

3$ с помощью блока 15. Таким образом, случайные фазовые сдвиги входного сигнала не влияют на работу предложенного преобразователя, т.е. преобразователь обладает свойством пропускать скачки фазы без переходных процессов, т.е ° без потери точности.

Преобразователь частоты в код, содержащий последовательно соединенные приемник информации и вычитатель частот выход которого соединен с перЭ

47 6 вым входом блока синхронизации, и последовательно соединенные реверсивный счетчик, сумматор, интегратор и блок вывода информации, блок управле" ния, первый, второй н третий выходЫ которого подключены соответственно к управляющим входам блока синхронизации, реверсивного счетчика н интегратора, отличающийся тем, что, с целью расширения функциональных воэможностей преобразователя при одновременном сокращении времени преобразования и расширении диапазона преобразуемых частот, в него дополнительно введены преобразователь код — частота, вычитатель частот, два 0-триггера и трн сумматора по модулю два, причем выход приемника информации соединен с первым входом дополнительного вычитателя частот, выход которого подключен ко второму входу блока синхронизации, первый выход которого подключен к первым входам первых 0-триггера и сумматора по модулю два, второй выход блока синхронизации подключен к первым входам вторых 0-триггера и сумматора по модуло два, вторые входы 0-триггеров объединены и подключены к первому выходу блока управления, выходы первого и второго 0-триггеров соединен со вторьин входами соответственно второго и первого сумматоров по модулю два, входы которых подключены непосредственно ко входам реверсивного счетчика и сумматора и через третий сумматор по модулю два — к запрещающим входам реверсивного счетчика и интегратора, выход которого через преобразователь код — частота подклочен ко вторым входам вычитателей час: :тот.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

В 705674, кл. Н 03 К, 1979.

2. Авторское свидетельство СССР по заявке IP 2755272/21, 16.04.?9 (прототип) .

900447

Соетавитель Плетнева

Редактор Л. Лукач Техфед И.Гергель Корректор N. Демчик

Заказ !2204/74 Тнраа 953 Подписное

ВНИИПО ГасудЖрствениого. комитета СССР по делай изобретений и открытий

)13035, Иосква, %-35, Рауаская наб., д. 4/5

Филиал ИПП "Патент", г. Ужгород, ул,,Проектная, 4