Многопороговый логический элемент четности

Иллюстрации

Показать всеРеферат

(72) Автор изобретения

И.А.Пальянов

Омский политехнический институт (7I ) Заявитель (5Ц ИНОГОПОРОГОВЦЙ ЛОГИЧЕСКИЙ ЭЛЕИЕНТ

ЧЕТНОСТИ

Изобретение относится к автомати ке и вычислительной технике, в частности к пороговым логическим элементам.

По основному авт. св. Р 538490 известен многопороговый логический элемент четности, содержащий линейный сумматор, состоящий из входных диодов и резисторной матрицы, подключенный через разделительные диоды к резистивному делителю и многопороговому дискриминатору, выполненному в виде нескольких взаимосвязанных одно. пороговых дискриминаторов на двухвходовых элементах И-НЕ. В цепь обратной связи многопорогового элемента включен RS-триггер на логических элементах И-НЕ,один вход триггера соединен с выходом однопорогового дискриминатора с наибольшим порогом срабатывания, второй вход соединен с источником стробирующего сигнала, а выход триггера подключен к одному из входов линейного сумматора tlat, 2

Недостатком многопорогового логического элемента четности является то, что перед подачей на входы линей ного сумматора очередного двоичного набора RS-триггер, входящий в состав многопорогового элемента, должен быть установлен в исходное (нулевое) состояние. Это сужает функциональные возможности, исключает возможность применения подобного многопорогового логического элемента четности в асинхронных схемах цифровых устройств.

Белью изобретения является расши-: рение функциональных возможностей, 3S т.е. обеспечение возможности использования многопорогового логического элемента в асинхронных схемах цифровых устройств.

2в

Поставленная цель достигается тем, что в многопороговом логическом элементе четности второй вход RSтриггера соединен с выходом линейного сумматора и через дополнительный

3 90045 резистор подключен к резистивному делителю.

Указанные изменения сделали возможным использование многопорогового логического элемента четности в асинхронных схемах цифровых устройств, за счет автоматического возврата RSтриггера в исходное состояние в тех случаях, когда последовательно сменяющие на входах линейного сумматора 16 двоичные наборы удовлетворяют условиям и х„ж4 4 и K x,þ <4 !

-и

1$ соответственно.

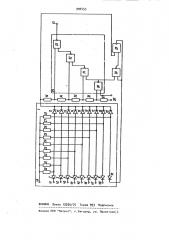

Многопороговый логический элемент четности содержит линейный сумматор 1, состоящий из диодов 2-19 и резисторов 20-28, образующих резис- 36 торную матрицу, многопороговый дискриминатор 29, состоящий из двухвходовых логических элементов И-НЕ 3033, резистивный делитель из резисторов 34-37, RS-триггер, образованный И логическими элементами И-HE 38 и 39 и дополнительный однопороговый дискриминатор, состоящий из логического элемента И-НЕ 39 и резистора 40. На входы 41-48 линейного сумматора 1 36 поданы входные сигналы, на входы 49 и 50 - напряжение питания,. Выходные сигналы снимаются с выхода 1 °

Работает многопороговый логический элемент четности следующим образом.

Значения весовых коэффициентов основных входов линейного сумматора равны единице, Вес входа многопорогового элемента, связанного с нулевым выходом RS-триггера равен 4, по" рог срабатывания однопорогового дискриминатора на элементе И-НЕ 39 равен

4, а на элементах 30 - 33 соответственно 8, 7, 6, 5.

4$

В исходном cocToRHI4I4 диоды 2 9g связанные со входами 41-48, проводят ток от источника питания -через соответствующие резисторы 20-27, Ток че рез резистор 28 от положительного полюса источника питания, диод и резистор 40 поступает в цепь после1 довательно соединенных резисторов

34-37 и далее к отрицательному полюсу источника питания, На выходе 51 И многопорогового логического элемента и выходе элементов. И-НЕ 30-33 в этом спучае присутствует уровень логичес5 4 кой единицы, 1!S-триггер находит я в нулевом состоянии и на выходе элемента И-НЕ 39 присутствует потенциал логической единицы, Входные сигналы в форме положительных потенциалов напряжения запирают в любых комбинациях диоды 2-9.

Если положительный потенциал присутствует только на одном из входов линейного сумматора 1, то соответствующий диод запирается и ток от источника питания чеоез соответствующие резисторы 20-2) и соответствующие диоды 11-18 переключается в цепь резисторов 40, 34-37. При этом потенциал на входе элемента И-НЕ 33, связанном с резистивным делителем, становится достаточным для появления на выходе 51 низкого уровня напряжения, соответствующего логическому нулю. При наличии высоких потенциалов на двух или трех входах линейного сумматора 1, соответствующие диоды 2-8 запираются и ток через резисторы 20-27 и диоды 11- 19 переключается в цепь резисторов 40, 34-37. Это приводит к срабатыванию дискриминаторов на логических элементах 32 и

33 или 31 — 33, что вызывает появление на выходе 51 многопорогового логического элемента .четности высокого или низкого уровня напряжения, соответствующего логической единице или нулю. Ток от источника питания через резистор 28 и диод 19 протекает через резисторы 40, 34-37 до тех пор, пока RS-триггер на элементах 38-39 не изменит своего состояния на противоположное. А это произойдет в том случае, когда ко входам линейного сумматора 1 поступит четыре или более единичных логических сигналов.

При этом на выходе логического элемента 30, имеющего значение порога

Т-8, установится низкий потенциал, триггер изменит свое состояние на противоположное. После этого ток через резистор 28 от источника питания переключится в цепь диода 10 а на выходе 1 многопорогового логического элемента для реализации функции четности установится значение сигнала, определяемое входным воздействием. Возврат RS-триггера в исходное состояние осуществляется в том случае, если последовательно сменяющие на входах линейного сумматора 1 двоичные наборы содержат четыре или бо900455 4 ное состояние, если последовательно сменяющие на входах линейного -ухеатора двоичные наборы содержат четы" ре и более единйц и менее четырех

З единиц.

Формула изобретения лее единиц и менее четырех единиц.

При этом величина напряжения на связанном с выходом линейного сумматора входе логического элемента И-HE 39 оказывается недостаточной для под" держания на выходе логического эле.мента И-НЕ.39 низкого уровня напряжения соответствующего логическому нулю. Это приводит к возврату RS-триггера в исходное (нулевое)состояние, запиранию диода 10 и переключению тока через резистор 23 в цепь последовательно соединенных резисторов 40, 34"37. На выходе 51 многопорогового логического элемента четности установится сигнал, определяемый входным воздействием, Таким образом, организация однопорогоеого дискриминатора с порогом срабатывания Т-4 на логическом weменте И-НЕ 39, входящим в состав

RS-триггера, сделала возможным автоматический возврат триггера в исход в Иногопороговый логический элемент. четности по авт. св. У 538490, о т л и ч а ю шийся тем, что, с целью расаирения функциональных воэможностей в нем, второй вход RS-триг "

1% гера соединен с выходом линейного сумматора и через дополнительный резистор подключен к резистивнсму делителю.

29 Источники информации, принятые Во внимание при экспертизе

1. Авторское свидетельство СССР

4 538490, кл, и 03 К 19/12, 24. 11.75.