Устройство для защиты нагрузки

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социал истическик республик

< >902008 (6 I ) Дополнительное к авт. санд-ву ¹ 678477 (22) Занвлено 21.04.80 (2I ) 2913809/24 (У7 с присоединением заявки И— (23) Приоритет .Опубликовано 30.01.82. Бюллетень № 4

Дата опубликования описания 30 01 82 (5E)M. Кл.

G 05 1/58

3Ъоудорствеивый комитет

СССР ио делом изобретений и открытий (53) УД3(621.316. .722.1 (088.8) В. П. Зотов, А. В. Власова и A. С. Зинке ич (72) Авторы изобретения (7() Заявитель т !

Г

I (54) УСТРОЙСТВО ДЛЯ ЗАШИТЫ НАГРУЗКИ

Изобретение относится к электротехнике и может быть использовано для зашиты различных радиотехнических уст ройств от повышения напряжения источника питания.

По основному авт. св. № 678477 известно устройство для защиты нагрузки, содержащее последовательно включенный в выходную шину переключающий элемент на транзисторе, управляющий транзистор, эмиттер которого подключен к отрицателт ной шине, а база - к датчику перенапряжения, включенному параллельно источнику питания и выполненному из последовательно соединенных порогового элемента и резистора, переключающий элемент выполнен по меньшей мере на двух параллельно соединенных защитных транзисто.рах, у которых соответственно объедине ны коллекторы, эмиттеры и через введенные резисторы базы, причем коллекторы подключены к плюсу источника питания, эмиттеры — к нагрузке и к минусу введенного дополнительного источника питайия, базы — к эмнттеру введенного согласующего транзистора, коллектор которого, подключен к плюсу дополнительного ио точника питания, а база - к коллектору управляющего транзистора, который че5 рез резистор подключен к плюсу дополнительного источника питания, а база управляющего транзистора подключена к средней точке делителя напряжения, образованного введенным резистором, оттии

10 вывод которого подключен через пороговый элемент к плюсу источника питания, а другой — к минусу источника питания, к которому подключен анод введенного диода, включенного параллельно нагрузке(13.

Однако в известном устройстве от сутствует запирающее напряжение за щитных транзисторов для быстрого вы ведения их из глубокого насыщения, что приводит к проникновению кратковременных бросков входного напряжения на вы ход устройства, кроме того, отсутству-. ет защита перехода эмиттер-база защитных и согласуюшего транзисторов в момент выключения, что понижает быстродействие и Надежность устройства.

Пель изобретения — повышение быстродействия и надежности устройства. 5

Поставленная цель достигается тем, что в устройство для зашиты нагрузки введе1гы две цепочки из последовательно соединенных двух резисторов и двух диодов, аноды KoTopúiõ; соединены H подклю- 10 чены х эмиттеру согласуюшего транзиотора и через цепочку из последовательно соединенных двух резисторов — к эмиттерам зашитных транзисторов, общая точка указанных двух резисторов подключена к 15 .точке соединения резисторов зашитных транзисторов, и к катоду одного из после довательно включенных диодов, а катод другого диода подключен к точке соединения базы согласуюшего транзистора с 20 коллектором управляющего тра из истора.

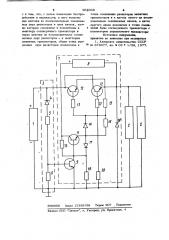

На чертеже представлено устройство, принципиальная схема.

Устройство для защиты нагрузки со.держит источник 1 питания, нагрузку 2, 25 датчик 3 перенапряжения, включаюигий последовательно соединенные стабилитрон

4 и делитель напряжения на резисторах 5 и 6, средняя точка которого соединена с исполнительным блоком 7, содержа- 3Q ши> г дополнительный источник 8 питания, управляющий транзистор 9, подключенный эмиттером к отрицательной шине, коллектором через резистор 10 — к дополнитель ному источнику 8 питания, базой — к средней точке делителя напряжения на резисторы 5 и 6. К плюсу дополнительного источника 8 питания подключен коллектор согласуюшего транзистора 11, база которого подключена к коллектору управляю- 4О щего транзистора 9. Зашитные транзисторы 12 подключены эмиттерами к нагрузкам 2 и к минусу дополнительного источника 8 питания, коллекторами - к положительной шине, а базами через резисторы

1 3 к катоду диода 14 и к точке соединения резисторов 15 и 16. Второй выBoll резистора 15 подключен к эмиттерам зашитных транзисторов 1 2, второй вывод резистора 16 подключен к точке соединения анодов диодов 14 и 17 с эмит-тером согласующего транзистора 11. Катод диода 1 7 подключен к точке соединения резистора 10 с базой согласуюшего транзистора 11 и коллектором управляюшего транзистора 9. К отрицательной шине подклгоче11 анод диода 18. Диод 18 включен параллельно нагрузкам 2. Резистор 19 включен между. коллектором управляюшего транзистора 9 и отрицательной шиной. Резистор 20 включен между точкой соединения резисторов 13 с катодом диода 14 и отрицательной шиной.

Устройство работает следуюшим образом.

При нормальном напряжении источника

1 питания зашитные транзисторы 1 2 находятся в режиме глубокого насьпцения (И <3 насыше1пге «< 0,2 В} за счет базового тока, протекаюшего через переход коллектор-эмиттер согласуюшего транзистора 11 развязываюшего диода 4. и резисторов 1 3 от дополнительного источника 8.

Стабилитрон 4 не пробит и напряжение на резисторе 6 недостаточно для открывания управляюшего транзистора 9.

При увеличении напря>кения источника

1 питания до определенной величины стабилитрон 4 пробивается, увеличивается падение напряжения на резисторе 6, что вызывает открывание управляющего транзистора 9 и отключение дополнительного источника 8 питания. Выходное напря:жение из-за инерционности насыщенных зашитных транзисторов 12 и наличия емкостных фильтров в нагрузках мгновенно пони>кается до нуля. За счет этого ток, протекающий через коллектор-эмиттер управляющего транзистора 9, резисторы 1 5 и 1 6 и диод 1 7 вызывает падение напря>кения на резисторе 15 и диоде 17, которое является запирающим для зашитных 12 и согласуюшего 11 транзисторов.

Включение управляющего транзистора

9 и появление отрицательного запираюше го напряжения на согласующем транзисторе 11 и зашитных транзисторах 12 происходит одновременно, что вызывает мгновенное запирание зашитных транзисторов 12.

Резисторы 15 и 16 выбираются такой величины, чтобы отрицательное запираюшее напряжение эмиттер -база зашитных транзисторов 12 не превышало допустимой величины при максимальном выходном напряжении. °

Предлагаемое устройство для защиты нагрузки имеет повышенную надежность и быстродействие.

Формула изобретения

Устройство для зашиты нагрузки по авт. св.¹ 678477, отлича юшее902008

ВНИИПИ Заказ 12383/58 Тираж 907 Подписное

Филиал ППП "Патент, г. Ужгород, уп. Проектная, 4 с я тем, что, с целью повышения быстродействия и надежности, в него введены две цепочки из последовательно соединенных двух резисторов и двух диодов., аноды которых соединены и подключены к 5 эмиттеру согласующего транзистора и через цепочку нз последовательно соединенных двух резисторов - к эмиттерам защитных транзисторов, общая точка указанных двух резисторов подключена к точке соединения резисторов защитных транзисторов и к катоду одного из последовательно соединенйых диодов, а катод .другого диода подключен к точке соединения базы согласуюшего транзистора с коллектором управляющего транзистора

Источники информашки, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 678477, кл. G 05 C 1/58, 1977.